基于FPGA实现TDC的布局布线优化方法研究

尹文芹,施韶华,3,刘音华,3,李孝辉,3,4

(1.中国科学院 国家授时中心,西安 710600;

2.中国科学院大学,北京 100049;

3.中国科学院 时间频率基准重点实验室,西安 710600;4.中国科学院大学 天文与空间科学学院,北京 100049)

0 引言

时间—数字转换是测量时间间隔的基本方法之一,在该技术发展的早期,半导体集成电路等电子学技术比较落后,模拟测量是时间间隔测量的主流方法。随着科学技术的进步,数字化技术因其灵活性、稳定性、低成本等优势逐渐成为时间间隔测量方法的主要研究方向[1]。

现场可编程门阵列FPGA(field programmable gate array)是一种数字化集成电路,是以PAL(programmab1e array logic)、PLA(programmab1e logic array)、CPLD(complex programmab1e logic device)等可编程器件为基础,进一步发展而来的更复杂的可编程逻辑器件[2-3]。

如何利用FPGA实现高分辨率时间数字转换器成为目前时间间隔测量技术的重要发展方向。但因FPGA灵活性较高,在设计中对于同种器件,相同的程序进行编译后,其布局布线结果也会不相同,导致实现统一电路设计难度增强。尤其在TDC(time-to-digital converter)的设计中,进位链的一致实现是保证其精确分辨率的前提条件。文章根据TDC基本原理,结合时间间隔计数器研制方案,利用FPGA底层结构,对加法进位链的布局布线进行优化,以确保其设计分辨率可达到皮秒量级。

1 时间数字转换器设计方案

1.1 时间数字转换器工作原理

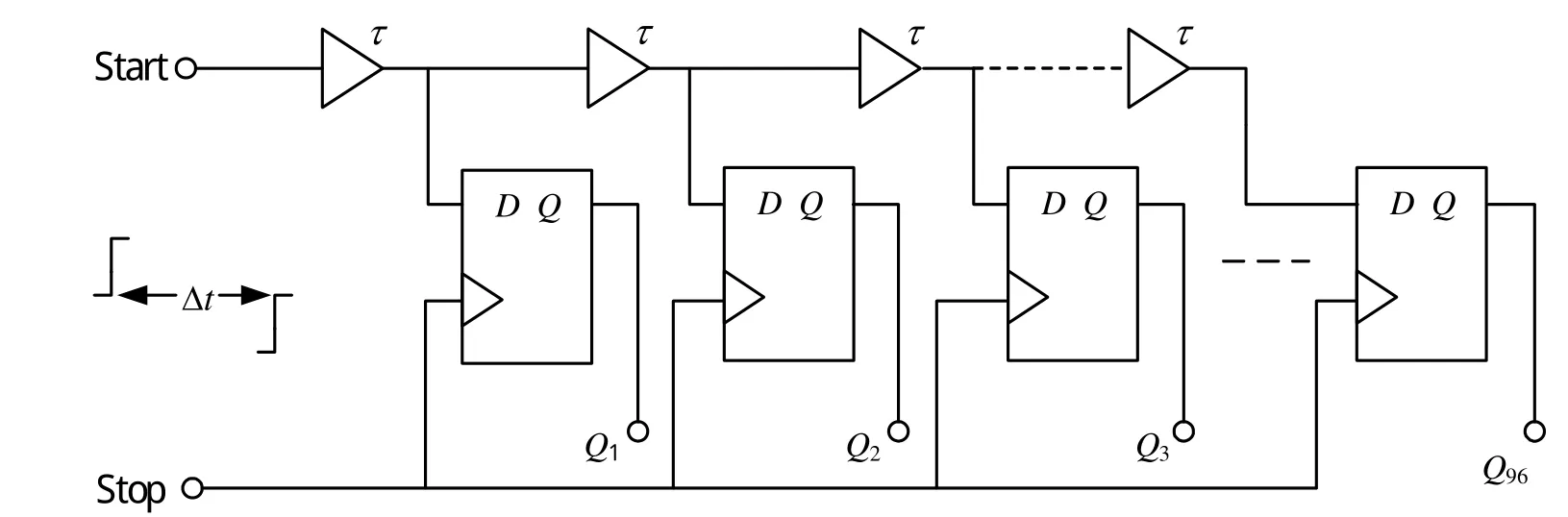

时间数字转换器的工作原理如图1所示。图中tD为被测时间间隔,即为Start信号的上升沿和Stop信号上升沿之间的时间间隔。Start信号上升沿到达后,在专用延迟线中进行传播,等待Stop信号;当Stop信号的上升沿到达锁存器,Start信号传播到第n级延迟线的状态被锁存记录,通过计算便可得到时间间隔。其中延迟线由多个延迟单元构成,每个延迟单元都有相同的传输延迟t,延迟t的大小可以决定转换器的最终分辨率[4-6]。

图1 延迟线型TDC结构

1.2 时间数字转换器设计方案

设计需实现量程为4 ns、分辨率为0.1 ns的时间数字转换器,其中采用加法进位链实现方法,以保证其分辨率达到设计要求。其方案为图2所示,用96个1位全加器构成了96位串行全加器。根据串行全加器的逻辑,只有前一级的逻辑运算完后,才会产生下一级的进位信号,因此,进位信号只能逐级从左到右依次产生且传播下去。如若进位输入信号为“0”,将测试信号(即Start或Stop信号)引入到全加器的加数的最低位,其余位设置为“0”,另一加数各位设定为“1”。这样,当Start或Stop信号为“0”时(即没有测试信号),总和信号各位均为“1”,也不产生进位信号;当Start或Stop为“1”时(即测试信号产生),产生了进位信号并且逐级向后传播,总和信号各位依次从“1”跳变为“0”[7]。将测试信号的跳变引入进位链中,通过总和信号的跳变能及时反映测试信号的位置信息。FPGA的每个逻辑单元均有进位输入到进位输出的延迟线路,进位输入到进位输出的进位延迟大多在几十皮秒量级,因而采用加法进位延迟链实现时间间隔测量的分辨率较高。

图2 TDC设计结构示意图

2 时间数字转换器的实现

考虑到如速度等级、功耗、成本等一些指标,最终选择Altera公司主流低成本CycloneIV系列。

2.1 Cyclone IV系列

Altera公司的Cyclone IV系列FPGA器件是其Cyclone系列产品,具有低成本、低功耗的特点。Cyclone IV器件采用了与之前的Cyclone系列器件相同的核心架构。这一架构包括由四输入查找表(LUTs)构成的LE,存储器模块以及乘法器。每一个Cyclone IV器件的M9K存储器模块都具有9 Kbit的嵌入式SRAM存储器。

2.2 底层布局布线

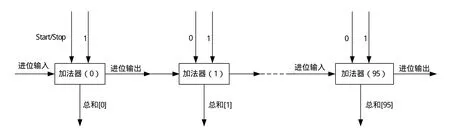

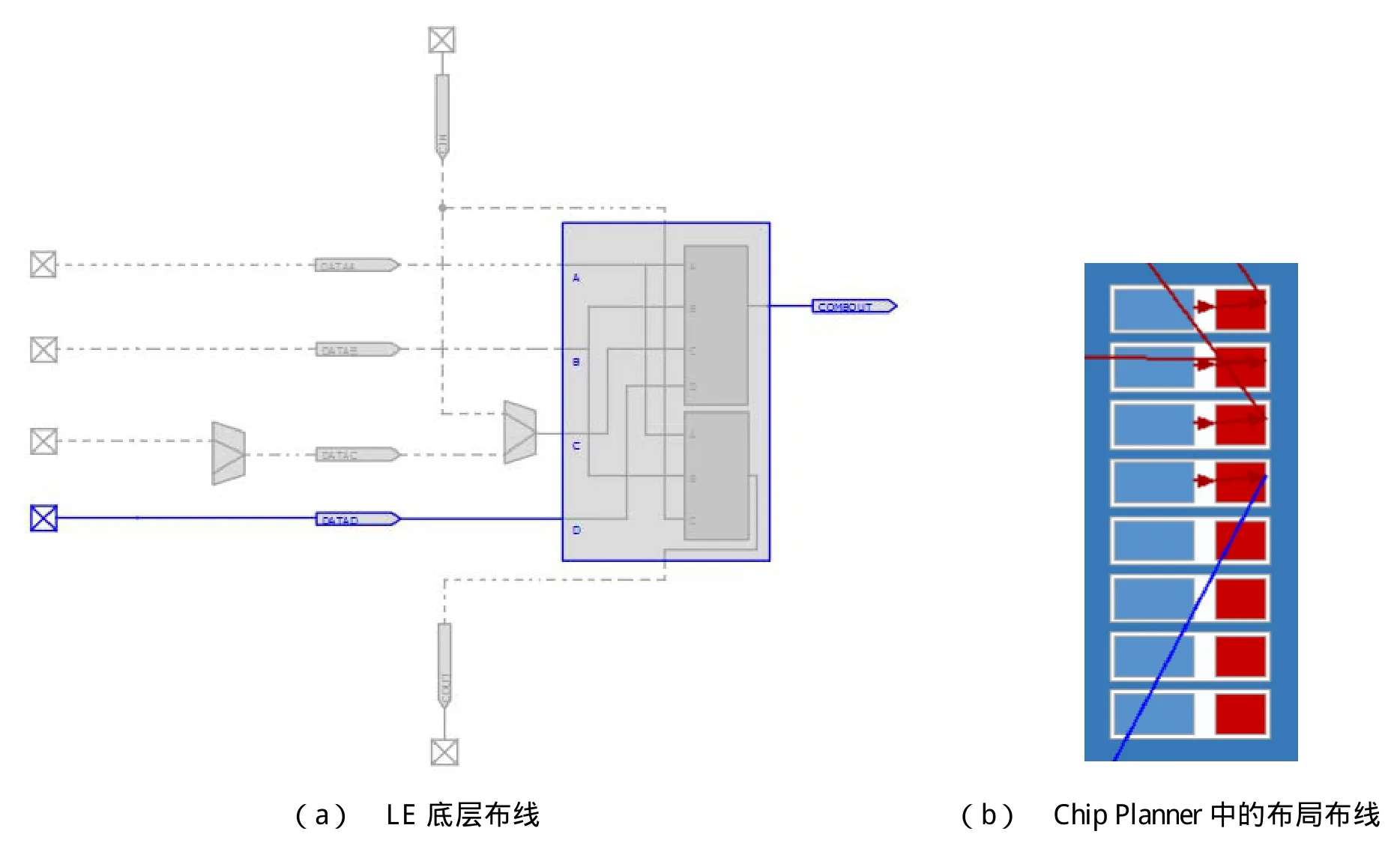

图3(a)为实现加法进位链底层布线图,每级均由上方的cin到cout,即为图2中所提及的每个逻辑单元均有进位输入carry-in到进位输出carry-out的延迟线路。图3(b)为1个LAB,由图可知每个LAB中都包含有16个LE。而 LE为Cyclone IV中最小的逻辑单元,每一个LE中包括1个LUT,1个可编程的寄存器,1个进位链。

图3 加法进位链底层布局布线

3 Quartus II布局布线优化方法

Quartus II是Altera公司为FPGA器件开发所提供的一款布局布线、设计仿真的软件,可通过该软件完成功能编译,综合优化,功能仿真、时序仿真及实现布局布线等。下面分别介绍在Quartus II 10.0及Quartus II 15.0下,应用FPGA生成进位链,并进行布局布线优化的方法[8]。

3.1 Quartus II 10.0

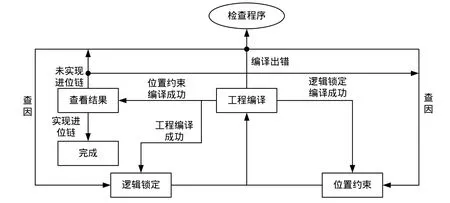

Quartus II 10.0是Altera公司2010年推出的一款软件,同时支持32位操作系统以及64位操作系统。在工程中,使用软件构建一个多位加法器,其中会产生多条进位链,且与寄存器匹配输出,方便计算,可使用反标注及逻辑锁定等功能固化布局布线,为确保通过FPGA能够实现统一的电路设计。其操作流程如图4所示。

图4 优化流程图

3.1.1 逻辑锁定(LogicLock)

逻辑锁定(LogicLock)是Quartus II内嵌的高级工具之一,通过在FPGA物理位置的区域性约束完成提高设计性能、继承以往设计成果、增量编译等功能。它能很容易地完成对每一模块的设计、测试和优化,再将这些模块集成为一个系统,进行系统优化设计,同时又能很好地保持原来已设计好的每单个模块的优化特性。逻辑锁定只能保证在更高层的设计锁定区域的大小和位置不变,但不保证原模块在此锁定区域中的电路的布局布线方式不变,从而无法保证在此后的更高层设计适配后模块的电路结构与性能不变。这种方式并不能解决本项目的问题。因此我们需要在逻辑锁定结束后进行反标注,以达到固化已经过优化的布局布线结果。其中逻辑锁定具体操作如下,反标注方法见节3.1.2。

逻辑锁定具体操作方法:

① 为要锁定的模块创建新的布局区域;

② 在LogicLock Region窗口处,将该模块位置选择为锁定,大小选择为固定,并且设制该模块所在位置及所需大小(高和宽);

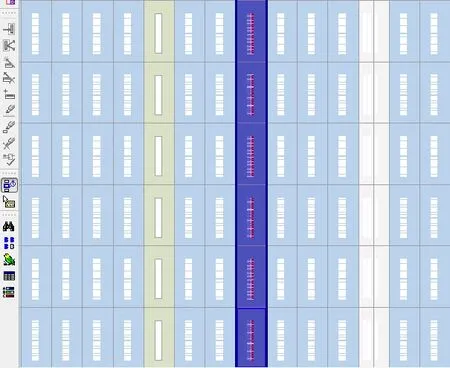

③ 编译,在Chip Planner中查看结果,如图5,图中top模块已被逻辑锁定。

图5 逻辑锁定示意图

3.1.2 反标注(Back-annotate)

反标注(Back-annotate)是逻辑锁定(LogicLock)设计流程中的重要环节,通过反标注操作,用户可以继承以往经过优化的布局布线结果。对优化后的模块进行反标注后,用户便能在顶层设计中导入该模块的反标注的布局布线信息,这样该模块的逻辑结构与性能在顶层中便能得到保证。

在对模块逻辑锁定后,进行反标注。反标注是在目前编译后,工程已达到所需目标,但为防止在加入其他工程后,编译结果发生变化,因此使用反标注功能,可将目前工程进行固化,可方便以后使用。反标注布线信息仅对固定大小和锁定位置的逻辑锁定区域有效,对于定义为浮动状态和自动大小的逻辑锁定区域,Quartus II软件将忽略布线信息。

通过逻辑锁定及反标注,这两种方法结合使用,可实现模块不被自动处理。

3.2 Quartus II 15.0

Quartus II 15.0只支持64位操作系统。在Quartus II 15.0中,不支持反标注,导致我们需要寻求别的方法来保证工程模块不被自动处理。逻辑锁定方法可正常使用,我们在逻辑锁定的同时增加位置约束,确保不被自动处理。其具体操作流程与图4相同,将实现反标注更改为位置约束,而后待位置约束编译成功后,查看结果。位置约束既可以使用菜单选择增加约束,也可在文件中自己添加约束。下面介绍文件添加约束方法。

在.qsf文件中,加入位置约束语句,保存编译后,可达到位置约束的作用。约束语句语法如下所示:set_location_assignment FF_X6_Y4_N7-to"add96:add96_1|add96_top:add96_top_1|result_1[0]"。

完成逻辑锁定及位置约束后,选定不想被自动处理的文件,对文件进行设计分离设置,完成以上步骤后,可确保Quartus II在编译时,不会将我们需要的自动处理。

4 测试与验证

设计采用Altera公司型号为EP4CGX150DF31C7的FPGA作为实例验证的器件。选用友晶科技DE2i_150开发板,搭配4 MHz校准时钟及三通道输入信号进行测试。

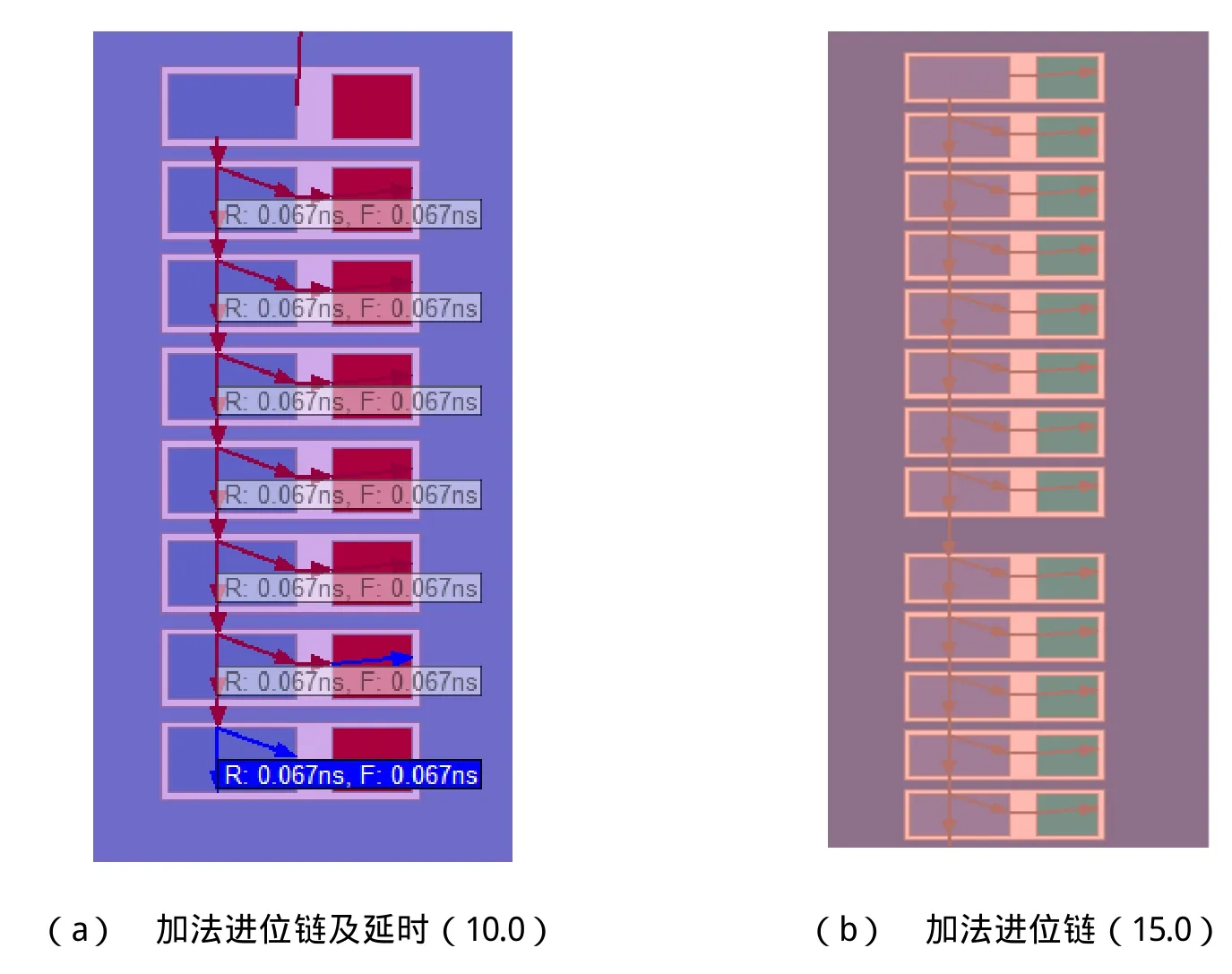

首先是在软件为Quartus II 10.0的情况下,所采用工程为用加法器实现96级进位链。工程中包括两个文件top.v和moban.v文件。初次编译后,如图6(a)及图6(b)所示,未能实现图3(a)中所介绍的cin,cout,进而也没有实现图3(b)中实现的加法进位链。

图6 初次编译后的布局布线

我们先对top.v文件进行逻辑锁定,限制区域及大小,编译,查看结果。而后根据文章前面所介绍的方法,对工程进行反标注。反标注成功后,再次对文件进行编译,查看Chip Planner,如图7(a)所示,可以发现工程实现了96级进位链,且图中显示了延时时间,因此,我们可根据这一特性,实现其他工程功能。

其次是在软件为Quartus II 15.0的情况下,防止自动处理的实现方式。工程相同,需求相同,逻辑锁定方法相同,区别在于并不进行反标注,而是将工程中的寄存器进行位置约束,使用文章之前所介绍的菜单选择方法或在文件中用语句完成均可进行位置约束,还需对模块进行设计分离,然后编译,编译成功后,查看Chip Planner,可以发现在使用Quartus II 15.0时,用以上方法也可防止被自动处理,实现96级进位链,如图7(b)所示。

图7 加法进位链及延时

5 进位链延时数据测量及分析

5.1 测试原理

本次测试是利用码密度测试方法进行的,标准的码密度测试(code density test,CDT)方法可以对每个延迟单元大小进行测试。现对于码密度测试方法进行简单的介绍。如果使用大量跳变时间均匀分布在[0,T]内的随机脉冲作为待测信号输入时间数字转换器,T为系统工作时钟周期,每个延迟单元被记录的次数的累加结果称为码密度,由此可以得到由各个延迟单元组成的离散直方图。如果随机脉冲足够多且输入的非均匀分布性可以忽略不计的话,那么直方图中每个延迟单元的统计次数正比于该单元的延迟量,从而可以计算出每个延迟单元的延迟大小。

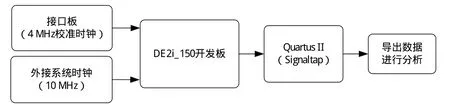

5.2 测试方案

根据上述原理介绍,设计测试流程图,如图8所示。在测试中需要产生大量的随机校准脉冲,且应保证系统时钟的频率和校准信号的频率不相关,即它们之间不能成整数倍关系。因此本次测试中采用4 MHz时钟作为校准时钟,带有校准时钟的接口板同系统时钟一同接入DE2i_150开发板,利用Quartus II中的Signaltap对各个延迟单元进行数据采集,分析数据,得到每级进位链延时。

图8 测试流程图

5.3 测试数据分析

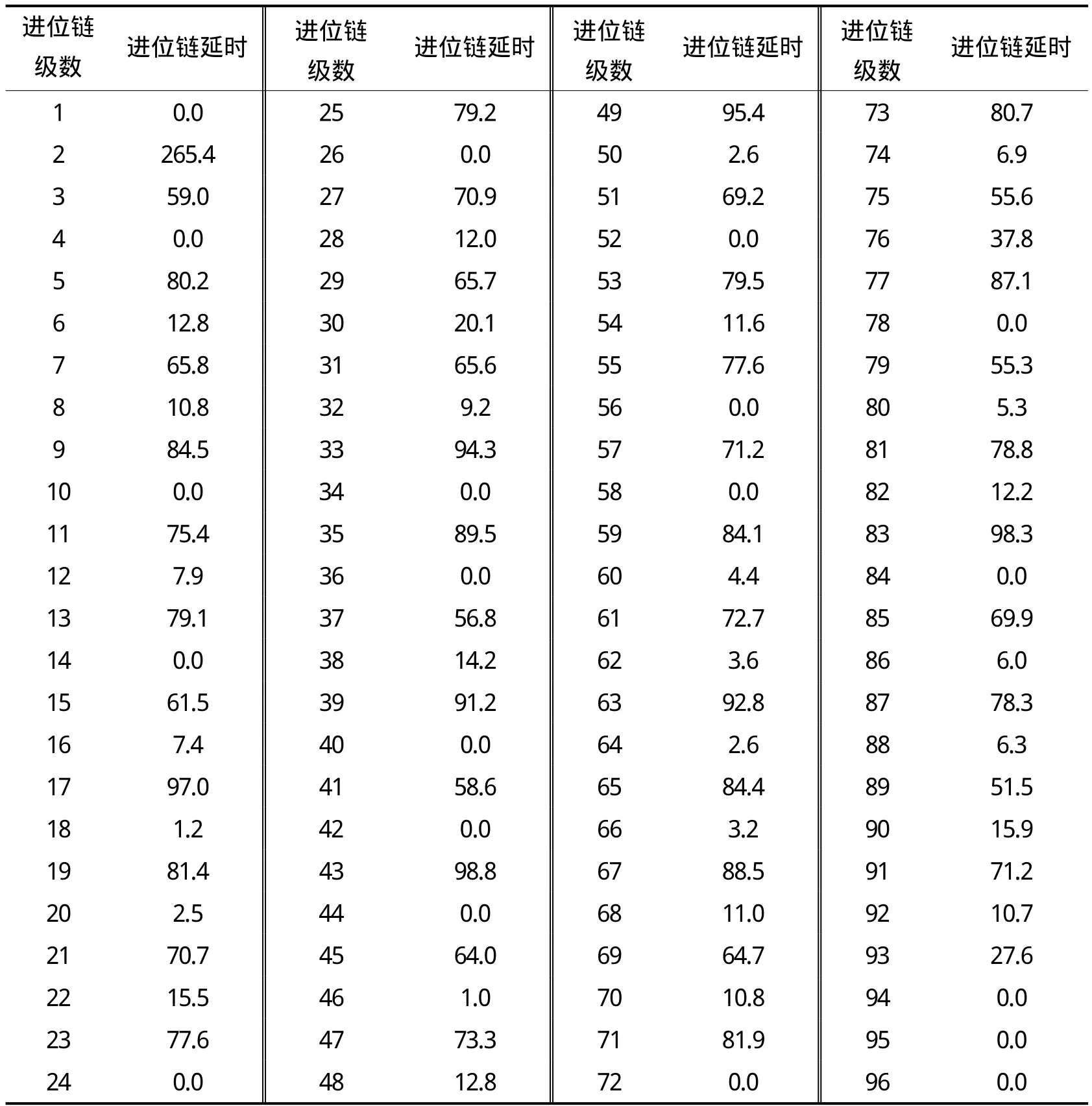

使用上述介绍的方法,实现96级加法进位链,其链路延时如表1所示。表1中有多级进位链延时为0 ns,而加法进位链延迟是一个物理延迟,不可能出现0 ns的情况,因此表中0 ns应是一个极小值或者是非常接近0 ns的值,通过分析认为可能是由于测试方法导致的,测试中产生的随机脉冲并未到达该级进位链,并且与进位链的位置以及内部布线也有一定的关系。

表1 96级加法进位链延时数据 ps

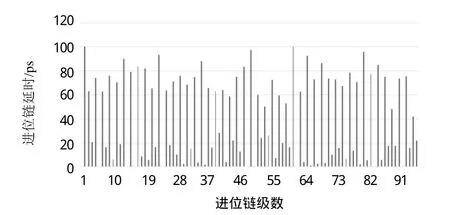

根据表1数据进行分析得到图9结果。

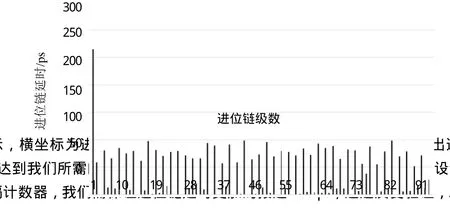

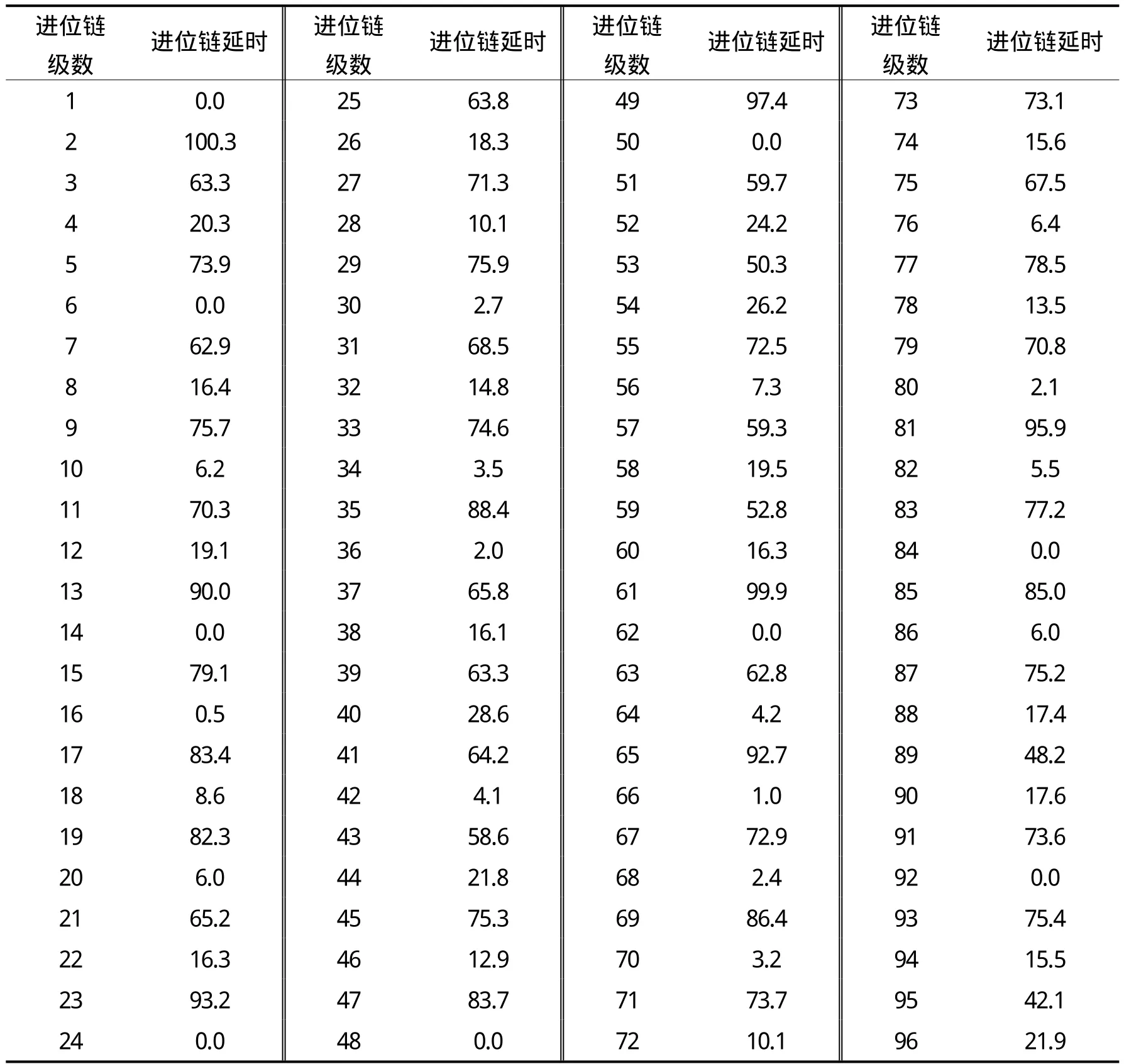

如图9所示,横坐标为50进位链级数,纵坐标为延时时间,由分析结果可以看出进位链延时最大为265 ps,远没有达到我们所需0的要求。同时表1中频繁的出现延时,也不利于设计实现。为实现高分辨率时间间隔计数器,我们需保证进位链延时更加的接近,通过反复验证 ,发现进位链延时与进位链所处位置以及内部的布线均有的关系,因此,找寻到合适的位置,可减小进位链延时,提高分辨率。表2为改变位置后,进位链延时数据。由表2数据分析进位链延时数据,分析结果如图10所示。

图9 进位链进延位时链数级据数分析结果

表2 改变位置后96级加法进位链延时数据ps

图10 改变位置后进位链延时数据分析结果

表2中出现了进位链延时为0 ns的情况,但出现的次数不像表1过为频繁,因此更有利于实现高分辨率TDC设计。由图10可以看出其链路延迟时间除第1级进位链延时在100.3 ps外,其余进位链延时均在100 ps以下,且延时大小分布较均匀,这为实现高分辨率TDC设计提供了基础。

6 结语

文章基于Altera的FPGA芯片采用Quartus II软件进行开发设计,实现了96级加法进位链的时间数字转换器。在设计实现过程中,采用反标注和逻辑锁定的方法对布局布线进行人工干预,并通过逻辑锁定改变进位链的位置,寻找合适的进位链位置,实现后95级进位链各级时延为0.1ns以下,第1级进位链时延为0.100 3 ns。该方法有效的解决了基于FPGA实现TDC的布局布线优化问题,实现了测量分辨率为100.3 ps的时间数字转换器。

参考文献:

[1] 张延.用FPGA实现高精度时间间隔测量[D].上海:中国科学院上海天文台,2006:2-18.

[2] 何宾.Xilinx FPGA数字设计:从门级到行为级双重HDL描述[M].北京:清华大学出版社,2014:94-114.

[3] 曾宪雄.基于FPGA的短时间间隔产生技术研究[D].西安:西安电子科技大学,2013:21-24.

[4] 李孝辉,杨旭海,刘娅,等.时间频率信号的精密测量[M].北京:科学出版社,2010:78-97.

[5] 罗敏,宫月红,喻明艳,等.时间—数字转换器研究综述[J].微电子学,2014,44(3):374-375.

[6] 徐振.基于TDC的时间间隔测量技术的研究[D].哈尔滨:哈尔滨工业大学,2008:8-15.

[7] 黄海舰.基于FPGA时间内插技术的TDC设计[D].武汉:华中师范大学物理科学与技术学院,2013:19-4.

[8] 张甘甘,陈文艺,李青,等.基于QuartusII的布局布线[J].科技信息,2008,35:478-479.