DDR3上的双读写通道设计与实现

唐 瑞,叶李萍,王经坤,姚远程

(1.西南科技大学信息工程学院,四川 绵阳 621010;2.西华师范大学商学院,四川 南充 637000)

0 引言

第三代双倍数据传输速率同步动态随机存储器(double-data-rate three synchronous dynamic random access memory,DDR3 SDRAM)自面世以来,以其相对于DDR2更高的运行效能与更低的电压功耗等优势,迅速在诸多领域中取代了DDR2,成为新一代高速、大容量数据缓存器中的较好选择[1]。通常Xilinx官方提供的DDR3 IP核中默认只有一套读写通道,读写共用同一套地址[2]。本设计是在DDR3上,切割出两套独立读写通道,基于时分复用(time division multiplexing,TDM)原则,使每一套读写接口互不影响。在第一套接口中向DDR3写入数据的同时,该设计实现了向第二套接口中写入或者读出数据,增强了DDR3的灵活性,提高了DDR3的使用效率。

1 DDR3的双读写通道设计

随着高速图像处理技术的飞速发展,在实现图像算法的过程中,往往需要实时处理大量的数据,所以必须采用高速数据缓存器DDR3作为实时数据缓存工具。目前,各大FPGA厂商都提供了对DDR3读写控制的IP核。但该IP核仅支持一套读写接口[3],无法同时进行读写。这是由于DDR3本身的特性所决定的。为了弥补这一缺点,需要设计一种从用户接口到DDR3的桥接电路。该电路使用时分复用的设计理念,能充分提高DDR3的读写效率;同时,结合外部的缓存器先入先出队列(first input first output,FIFO),可同时实现对DDR3的读写操作。

2 实现方案设计

本文使用Xilinx公司提供的IP核,生成控制DDR3的控制器核(memory interface generator,MIG),并与用户接口[4]。本设计在该控制器的基础上,通过时分复用原则,将一套不独立的读写通道搭建为双独立的读写通道,能满足用户同时读写的要求。

2.1 硬件模块结构

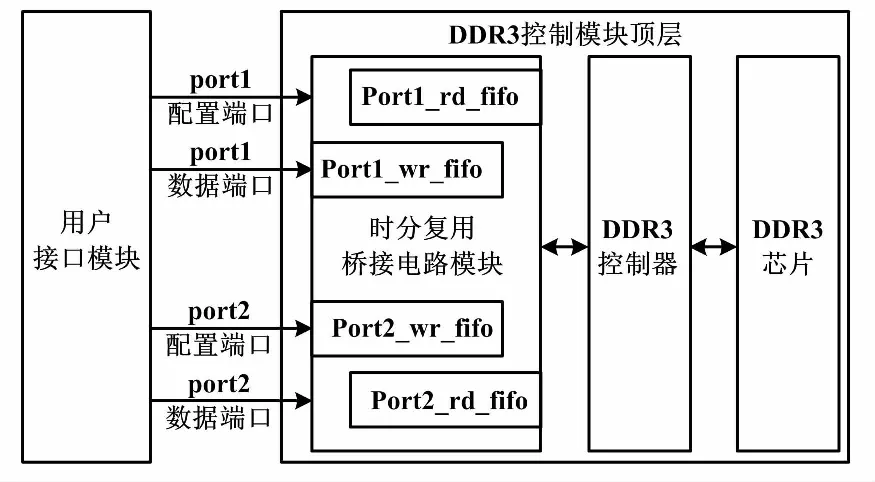

整个硬件模块分为4大部分:用户接口模块,时分复用桥接电路模块,Xilinx公司所提供的DDR3控制器以及DDR3芯片。其中,用户接口模块作为面向用户的接口,包含两套独立的读写接口。此模块是发起读写操作的源头。时分复用桥接电路模块可实现双读写端口向单读写端口的转换。此模块内部包含4个FIFO,用于DDR3读写双通道的数据临时缓存。DDR3控制器由IP核MIG生成,能完成对DDR3写入数据和读出数据的操作,是DDR3的主要控制器,但其仅有一套非独立读写通道。DDR3高速数据缓存器属于外部硬件器件,可实现数据存储功能。整个系统硬件设计结构如图1所示。

图1 系统硬件设计结构图Fig.1 Structure of system hardware design

2.2 用户接口模块设计

用户接口包括两套独立的读写接口port1和port2,可实现用户数据、用户配置信息与桥接电路模块之间的交互。在每套读写接口中均有配置端口和数据端口。配置端口包括用户需要读(写)的数据长度,读(写)操作的起始地址,读(写)命令信号的触发,读(写)操作完成反馈信号;数据端口包括写入的数据信号,写入数据有效信号,读出数据有效信号与读出的数据信号。port1与port2两套读写接口完全一致,皆包含以上信息。本设计所采用的同步时钟是由DDR3控制器核输出的用户时钟。该同步时钟为200 MHz。

2.3 时分复用桥接电路设计

2.3.1时分复用状态机设计

本文采取时分复用的思想,通过数据切换器,使两套读写接口分时地与DDR3控制器接口相连接。每组读写接口负责读和写两种任务。所以,总的状态可以分为4种:port1写数据任务,port1读数据任务,port2写数据任务,port2读数据任务。由用户接口模块配置的指令决定执行哪些指令。用户可以同时下达多个指令任务,由时分复用轮循机制轮流执行任务,以达到同时读写的效果[5]。

为了让4个任务在执行时避免因建立冲突而相互独立,需要定义4个状态。每个状态对应执行一个任务。状态机在空闲状态中经过条件判断结构,确定跳转到用户下达的任务状态;进入任务状态后,开始任务执行计时;任务计时计满后,无论该任务是否执行完毕,都通过一个额外的结束状态跳转到空闲状态,以完成循环。时分复用状态机设计如图2所示。

图2 时分复用状态机设计图Fig.2 Design of the TDM state machine

图2中,IDEL为空闲状态。在该状态中,可实现4种任务命令检测,并对用户已下达的多个任务指令进行执行顺序的划分。任务执行顺序的划分采用了1个2 bit位宽的单向计数器flag来实现。flag值为1,对应port1写数据任务;flag值为2,对应port1读数据任务;flag值为3,对应port2写数据任务;flag值为0,对应port2读数据任务。规定flag在任务执行计时满8个时钟周期之后,不管任务是否完成,都跳转到空闲状态,flag自动单向加1。flag的不同值代表着对不同任务指令情况进行检测。当flag为1时,若检测到用户下达过port1写数据任务,而此时又是在port1写状态中,则执行该任务;若没有检测到用户下达过port1写数据任务,则返回,flag自动单向加1,并进行下一个任务状态检测[6]。

2.3.2实现时间片的划分

用户下达的不同指令任务信息会存储在不同的对应寄存器中。当上电复位时,该寄存器值为0。当用户发送读(写)指令任务(上升沿脉冲触发)时,该寄存器值置1,完成任务下达。当任务执行一段时间后,如通过地址长度检测到该任务被执行完成,则该命令寄存器被清零,完成任务。

为了实现用户发布的指令任务能同时进行,设计中若单个任务耗时长于8个时钟单位,则该任务不能被一次性执行完毕,而是采用任务执行计时的机制。通过定义一个任务执行时间计数器,无论任务是否执行完毕,只要该计数器达到阈值,便立即跳出执行状态并回到IDEL,flag加1,自动检测执行其他队列任务。这样使用轮循的时分复用机制,能满足同时读写的目标。该过程完成了对DDR3执行各种任务时间片的切分。设计中所设置的两组接口读写数据任务定时阈值为8个时钟周期,同步时钟为200 MHz[7]。

在经过多次循环后,用户发布的所有任务被执行完毕。在此过程中,读写数据个数计数器对任务中读写的数据总量进行计数。系统每读写一个数据,则与任务相对应的读写数据个数计数器便累加一次。当累计值达到用户配置的读写数据个数(用户配置读写数据长度,通过读写数据长度来换算出具体的读写数据个数)时,判定本次任务执行完毕,从而将该任务对应的寄存器中的任务信号置0。

系统检测到读(写)命令后,即跳转到相应的状态执行任务。每个不同的任务状态映射为对DDR3控制器读(写)操作的不同配置。在进入不同状态的同时,对应任务起始地址端口的地址值被寄存在相应的地址寄存器中。4个这样的地址寄存器通过任务状态控制的数据选择器连接到DDR3控制器的地址端口。在DDR3和对应FIFO准备完毕的前提下,每次对App_wdf_data端口读(写)一个数据,地址寄存器便自增8。由于该端口位宽为512 bit,而DDR3存储单元位宽只有64 bit,即相当于一次存取了8个DDR3单元数据。当地址寄存器计数至用户配置的地址缓存长度时,读(写)数据个数计数器同时记满,任务执行完毕,解除任务指令,任务寄存器有效信号置0。

用户接口电路中使用了4个FIFO作为数据缓存。待写入DDR3的数据被缓存在写数据FIFO中。写数据FIFO输入位宽为256 bit,输出位宽为512 bit,以便与DDR3控制器对接。待读取的数据被缓存在读数据FIFO中。读数据FIFO的输入位宽为512 bit,输出位宽为256 bit,以便与用户接口对接。当读写FIFO出现任何读空或因写满而导致其未准备好时,整个系统的任务都将暂停执行,直到FIFO恢复正常才可继续执行。

3 板级实际测试

系统采用Xilinx的SUME开发板作为实现平台。FPGA采用Vertex7系列的XC7VX690TFFG1761。在Xilinx的VIVADO集成开发环境中,根据以上硬件设计方法,采用VerilogHDL建模实现系统功能。编写用户模块产生数据和控制信息源,通过综合布局、布线生成比特流文件;然后将比特流文件下载到FPGA板卡上,借助集成在VIVADO中的在线逻辑分析仪工具Debug,实现对测试信号的抓取分析[8]。

经实际上板测试,若同时往port1与port2写入一定长度的数据:分析Debug工具抓取到的结果,基本实现了同时向DDR3的port1与port2写入数据,数据和有效信号都能同时从用户接口模块送入时分复用桥接电路。但从抓取DDR3核的写入数据端口可以看到,实际上数据是被轮流写入port1与port2的,地址在两个接口间轮流切换,直至写完用户规定的地址长度。同样地,同时对写入数据进行读取,分别从port1里读取刚才写入port1的数据,从port2里读出刚才写入port2的数据。此时可以看出,虽从总体上是两个端口同时在读数据,但实际放大后是分时间片读数据。port1和port2接口交替读取,提高了DDR3实际使用效率,没有闲置状态。

为了验证数据的正确性,定义了一个累加数据源,同时向port1与port2写入一定大小的数据;分别利用Debug工具抓取用户接口模块的写入数据与DDR3核接口的写入数据,对比其是否相同,以确定数据是否成功写入。从板级测试可以确认,在按照规定时序送入port1与port2的累加数时,从0开始累加,并随着数据有效信号每次加1,一直写到规定长度。因此,从地址对应的数据来看,写入DDR3数据验证成功。而在写入数据完成之后,port_wr_done信号拉高,告知用户已经准备好读取数据。用户接口此时送入读取指令,在port1和port2中同时读取刚才写入的数据。从Debug的信息来看,port1与port2能同时读取数据,且数据为从0开始依次累加,与写入数据一致,所以DDR3读取验证成功。此外,用户每次下达任务时都能在DDR3的任意地址范围内选择读、写数据的地址,比如选择性读取几段而非全部数据,以此来测试本设计的灵活性。板级测试表明,DDR3能按要求灵活选择写入或读出地址,各功能可正常使用。

4 结束语

基于Xilinx公司提供的DDR3 IP核控制器MIG,完成了在DDR3上切割为双独立读写通道的用户接口。两套接口互不干扰,能同时完成读写操作[9]。设计了一种时分复用桥接电路,将DDR3 IP核MIG提供的一套控制接口搭建为两套独立的用户读写接口,通过数据切换器使两套用户读写接口按时间片分时与DDR3控制器接口相连。通过Virtex-7 XC7V690T板级测试,证明了该DDR3双读写通道控制器能高速、稳定、有效地工作,能满足用户同时进行两套接口的读写操作;用户接口操作时钟达到200 MHz,DDR3内部数据存储时钟达到800 MHz。此双通道DDR3缓存器适用于各种需要大量高速缓存数据的系统的研发工作,突破了传统DDR3仅有一套非独立读写接口的局限,提高了DDR3的灵活性与工作效率。

参考文献:

[1] 唐瑞,姚远程,秦明伟.高速图像模拟源的研究与实现[J].自动化仪表,2017,38(8):40-44.

[2] 严振杰,俞磊,周鹏成.AP1000无线通信系统电磁兼容性试验设计[J].自动化仪表,2017,38(2):82-85.

[3] 董旭明,李志斌.计算机视觉在并联机器人运动学标定中的应用[J].自动化仪表,2016,37(5):16-19.

[4] WANG B P,DU J S,BI X.High bandwidth memory interface design based on DDR3 SDRAM and FPGA[C]//International Soc Design Conference,Gyeongju,2016.

[5] 高胜.高速采样数据存储控制器的设计与实现[D].成都:电子科技大学,2016.

[6] ANIL L,SIDDHARTH V,MICHAEL P.A Case Study:Power measurement and optimization of DDR3 DIMM in servers[C]//2015 IEEE Electrical Design of Advanced Packaging and Systems Symposium,Bangalore,2015.

[7] HITESH S,MERVIN J,DAVID S.DDR3 Interconnect optimization-signal integrity and timing analysis perspective[C]//2015 International Conference on Control,Electronics,Renewable Energy and Communications,Bandung,2015.

[8] 毕然.基于DDR3的CMOS高速图像采集系统的FPGA设计与实现[D].哈尔滨: 哈尔滨理工大学,2015.

[9] JANESKV J,RIZZO N D,HOUSSAMEDDINE D.Device performance in a fully functional 800MHz DDR3 spin torque magnetic random access memory[C]//Memory Workshop (IMW),2015 5th IEEE International,Taipei,2015.