含变阻结构的线性光耦隔离MOSFET/IGBT高速驱动

刘俊灵,付 星,孙浩巍,王天一

(成都信息工程大学 控制工程学院,四川 成都 610225)

0 引 言

一般的对于电力电子器件而言,都需要具备满足一定条件的驱动电路来连接微处理器与电力电子器件。驱动电路的好坏直接影响整个系统的性能。这就要求驱动电路具有较快响应速度、较强的驱动能力,并且功耗不能太高。随着功率密度增加,开关管的开关频率提高,对驱动电路的响应速度和驱动能力的要求也随之提高[1]。由于电路拓扑结构的需要(如全桥电路)和提高电路抗干扰能力的要求,在功率主回路和控制电路之间需要实现电隔离。隔离环节的性能直接影响功率器件的工作和整个电路系统的抗干扰能力[2]。

在隔离驱动电路中采用光耦隔离是目前较领先的技术方式。目前MOSFET/IGBT光耦隔离驱动电路主要有集成驱动与采用分离元件两种方式。集成的光耦驱动电路目前工作频率能到100 kHz左右,如果驱动信号频率再进一步提高,则输出波形发生畸变,使电力电子系统不能正常工作。而采用分离元件构成的光耦隔离驱动电路,其关键元件光耦合器如果采用开关型光耦,高频的开关型光耦的工作频率可以达到几MHz,能满足频率要求,但是工作电压一般为5 V,因此电平不兼容,不能驱动12 V及以上的MOSFET/IGBT电力电子器件。如果采用能工作在12 V及以上的线性光耦,其工作频率一般在几十kHz,满足不了高频率的要求。采用光耦隔离可以很好地实现高频信号隔离,具有较低的输入输出电容,隔离效果好,可以有效的消除电路中产生的EMI,没有辐射也不易受周围电磁场的干扰[3]。但是光耦的开关速度较慢,对驱动脉冲的前后沿产生较大延时,影响系统的控制精度[4]。所以问题的核心在于满足驱动电平要求的条件下,提高隔离光耦的工作频率。

为了改善目前电力电子器件高速工作与光耦隔离驱动速度不高两者之间的矛盾,本文在采用分离元件的前提下,对如何提高核心器件线性光耦隔离器的工作频率的问题做了研究。

1 光耦隔离的常用电路

一般驱动信号隔离所使用的四脚线性光耦,其常见的电路使用方法如图1所示,其中R1、R2为限流电阻,R3为光耦集电极电阻,Uo为光耦输出信号。

图1 线性四脚光耦常用隔离电路

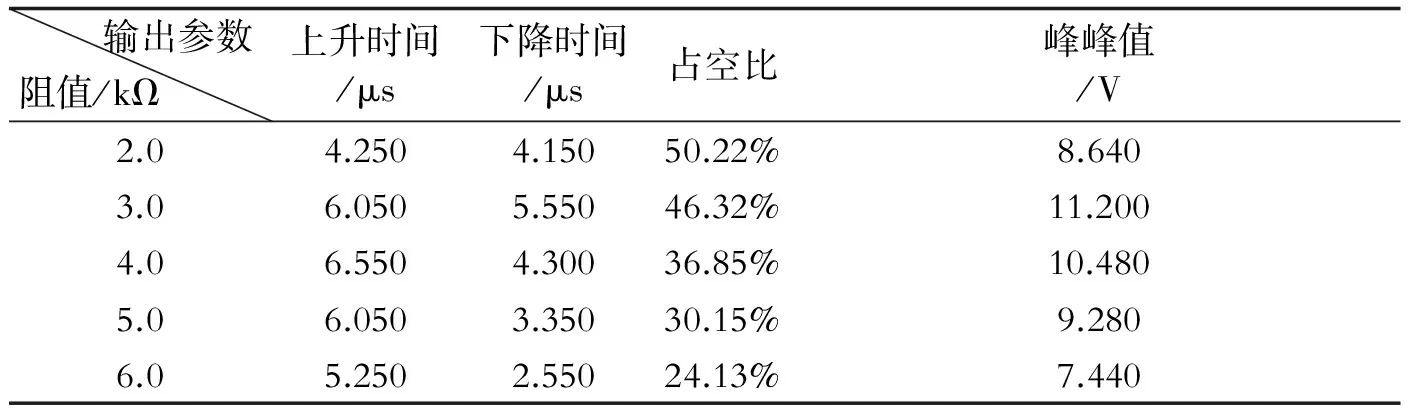

根据图1所示电路,光耦集电极电阻的不同值,以SFH610A-2四脚线性光耦为例,在实验室条件下当驱动信号的频率为43.2 kHz时,测得Uo的输出数据如表1所示。

表1 光耦在集电极电阻值不同情况下的输出参数

由表1中数据可知,当光耦集电极电阻值小于2 kΩ时,此时光耦不能完全开通;当光耦集电极电阻大于6 kΩ时,此时光耦不能完全关断。所以在以上两个电阻区间,光耦的输出信号不利于作为工程使用的参数。本文主要分析在2~6 kΩ之间的阻值光耦的输出特性。

当光耦集电极电阻阻值在2~6 kΩ之间时,由表中数据可得到光耦的输出信号在单位电压变化所需要的时间,分别如图2和如图3所示。

图2 单位电压上升所需时间

图3 单位电压下降所需时间

由于光耦的电流传输比的限制,导致其集电极的输出信号电压的幅值,受到集电极电阻的影响较大。当集电极电阻过小,就会导致输出电压的幅值摆幅过小,并且会导致集电极输出电压下降沿变缓,从而不能产生有效的MOSFET/IGBT门极控制信号。但是当集电极电阻值越大,由于光耦自身分布电容的存在,集电极输出电压上升沿变缓,光耦的频率特性就越差,传输时延也就越长。

所以一般在低频下使用光耦隔离,集电极电阻可以找到一个合适的阻值,能同时兼顾输出电压幅值与传输频率,但是在高频下,一个固定的电阻值无法保证输出电压的波形质量。

2 对线性光耦的输出特性分析与输出电路改进

针对由四脚线性光耦构成的集电极电阻为固定值的传统隔离驱动电路不能用于高频驱动的情况,结合前文实验室条件下测得的光耦上升/下降沿与其集电极电阻阻值的关系,需要设计一种集电极电阻阻值在光耦开关过程中变化的变阻值电路。

当线性光耦工作在开关方式时,从线性光耦集电极和射极间电压上升(图2)和下降特性(图3)看,线性光耦的集电极和射极相当于一个受控可变电阻和一个等效电容的并联,线性光耦的集电极和射极间的输出电压相当于等效电容上的电压。受控可变电阻的阻值受线性光耦中发光二极管控制,当发光二极管通过电流时,受控可变电阻阻值变小;当发光二极管没有电流时,受控可变电阻阻值变大。如果保持线性光耦的集电极或射极上串联电阻的大小不变,当受控可变电阻阻值变小时,等效电容放电速度快于充电速度,等效电容电压下降;当受控可变电阻阻值变大时,等效电容放电速度慢于充电速度,等效电容电压上升。所以,等效电容上电压的升降以及升降的速度受等效电容充电效应和放电效应的共同影响,放电效应由受控可变电阻决定,而充电效应由线性光耦的集电极或射极上串联电阻决定。

由图2与图3可知,在线性光耦的发光二极管施加方波电流时,线性光耦的集电极或射极上串联的电阻越大,线性光耦的集电极和射极间的电压下降沿的时间越短,而上升沿的时间越长;反过来,如果线性光耦的集电极或射极上串联的电阻越小,线性光耦的集电极和射极间的电压下降沿的时间越长,而上升沿的时间越短。所以可以构造一种变阻结构,使得变阻结构阻值在光耦开通时变大,在光耦关断时阻值变小,从而改善光耦的频率响应。

图4 变阻结构做光耦集电极的光耦隔离电路

在图4所示四脚线性光耦隔离驱动电路中,由R3、Q1、C1三个元器件可以构成变阻结构支路。当光耦关断时,三极管导通,此时变阻结构的等效电阻主要由PNP三极管Q1导通后的集射极电阻决定,三极管导通后电阻值很小,从而加速光耦集射极电压的上升;当光耦开通时,三极管截止,三极管截止后电阻值很大,此时变阻结构的等效电阻主要由电阻R3决定,此时等效电阻变大,从而加速光耦集射极电压的下降。由图4变阻结构的光耦集电极输出的电压波形如图5所示。

图5 光耦集电极采用变阻结构输出的实测波形

由表1中数据可得,在电阻值为3 kΩ时,光耦能完全开通关断,单位电压上升时间为0.540 μs/V,单位电压下降时间为0.496 μs/V。把光耦集电极电阻设计为可变电阻值的变阻结构之后,在实验室条件下,测得光耦输出的波形如图5所示,改善之后的单位电压上升时间为0.093 μs/V,单位电压下降时间为0.376 μs/V。对比可知,单位电压上升时间比原来减少了82.8%,单位电压下降时间比原来减少了24.2%。

常见线性光耦的光敏三极管的响应速度是微秒级,属于光耦固有的响应时间,一般很难改变。经过变阻结构做为线性光耦的集电极上拉电阻后,从改变外部驱动电流的角度,加快了光耦输出信号的上升/下降沿的变化速度,从而改善了光敏三极管的响应速度,而这正是线性光耦作为高速驱动中的瓶颈。如图5所示,线性光耦输出较好的信号波形,还并不能直接驱动MOSFET/IGBT,所以一般在之后再加上一级放大电路,最后经过推挽电路输出驱动信号,信号的上升/下降沿只需数百纳秒,如此便能实现高速驱动MOSFET/IGBT。

3 含有变阻结构的光耦隔离MOSFET/IGBT高速驱动应用实例

如图6所示,使用含有变阻结构所构成的光耦隔离MOSFET/IGBT高速驱动,其中电阻R4、电容C2和PNP型三极管Q2组成动态电压比较器。动态电压比较器中有加速电容C2的存在,因为电容两端电压不能突变,当光耦输出信号变化的开始阶段,那么电容C2相当于短路,此时能给三极管基极提供瞬间的大电流,使三极管在光耦输出信号的拐点处便提早开通或者关断。由于光耦相对三极管开通关断的速度缓变的特性,缺少加速电容会导致信号传输过程中发生占空比畸变,导致信号的占空比丢失或者增加。动态电压比较器既能在线性光耦输出信号由高电平变低电平的起始阶段检测到信号的变化,也能在线性光耦输出信号由低电平变高电平的起始阶段检测到信号的变化。这样,无论是在检测线性光耦输出信号由低电平变高电平时,还是在检测线性光耦输出信号由高电平变低电平时,都几乎没有延时,从而避免了信号传输过程中的占空比畸变。

图6 含变阻结构的光耦隔离高速驱动实例

图7为高速驱动电路实测输出波形,MOSFET门极驱动信号上升时间为250 ns,下降时间小于150 ns,实测波形表明,该驱动电路在满足线性光耦隔离条件下,高速驱动效果良好。

图7 驱动实测的MOSFET门极驱动信号

4 结 论

本文设计了一种基于四脚线性光耦的新型高速率驱动器结构,改善光耦的开关频率特性,利用特殊的能改变电阻值的电路结构来提高光耦的开通与关断的速率,从而缓解因光耦的开关频率给整个MOSFET/IGBT驱动带来的频率限制。在实现高速驱动的前提下,整个驱动器能有效地完成电平兼容,并且隔绝了MOSFET/IGBT的开关噪声对微控制器端的影响。整个电路结构简单,易于实现,能够有效运用于PWM控制中。但是对于变阻结构的设计并不仅限于此,例如在变阻结构中,对变阻结构中PNP三极管引入正反馈就是未来的一个改进方向。

参考文献:

[1]史凌峰, 王庆斌, 许文丹. 用于APFC的低功耗MOSFET驱动电路设计[J]. 西安电子科技大学学报(自然科学版),2011, 38 (1) :54-58.

[2]王正仕,陈辉明.无传输时延的调制型功率MOSFET驱动电路[J].电气自动化,1999, (4): 61-66.

[3]陈建萍.一种基于IR2113的隔离型MOSFET驱动电路设计[J].赣南师范学院学报, 2011, (3): 57-59.

[4]周晨松,沈颂华. UC3724/UC3725 功率MOSFET驱动电路芯片组的应用[J].沈阳航空工业学院学报, 2001, 18(1): 43-45.