一种基于平方环的载波提取方法

中国电子科技集团公司第三十九研究所 王小妹 龙甫煜 王永华

引言

在抑制载波的调制信号中,一般都含有载频信息,这样在空中才能传输足够远。在接收端,需要消除载频产生的影响,才能得到需要的信息。而传输信息是有符号的,这些信息的符号对载波的提取会造成误判影响,严重的甚至无法解调,所以需要寻找一种能够去掉信息符号影响的解调方法。而平方环的处理方法是对输入信号首先进行平方操作,将符号跳变的因素消除,得到了较好的效果[1]。

1.平方环基本原理

在软件无线电(SDR)技术实现的收发系统中,数字锁相环在载波同步、位同步、相干解调、信号跟踪、频率选择等方面发挥着重要作用,已成为数字调制/解调,数字上变频/下变频中不可缺少的核心器件。接收机为了提取载波,普遍采用平方环法和科斯塔斯环法,其中平方环以其电路结构简单而得到了广泛应用。

平方环的基本原理为:首先将输入信号进行平方操作,这样就消除了信息符号的影响;接着平方操作的结果与数字控制振荡器(NCO)的输出进行乘法操作,乘法输出再进行低通滤波,滤除高频分量,得到低频或直流信号,低通滤波的输出即低频或直流信号送给环路滤波器,环路滤波器的输出送NCO,环路滤波器调整NCO的输出以使低通滤波的输出为直流信号,此时即实现了对传输信号载频的提取。低通滤波器的输出即为包含原始信息且去掉载频的信号。具体实现流程框图如图1所示。

图1 平方环实现框图

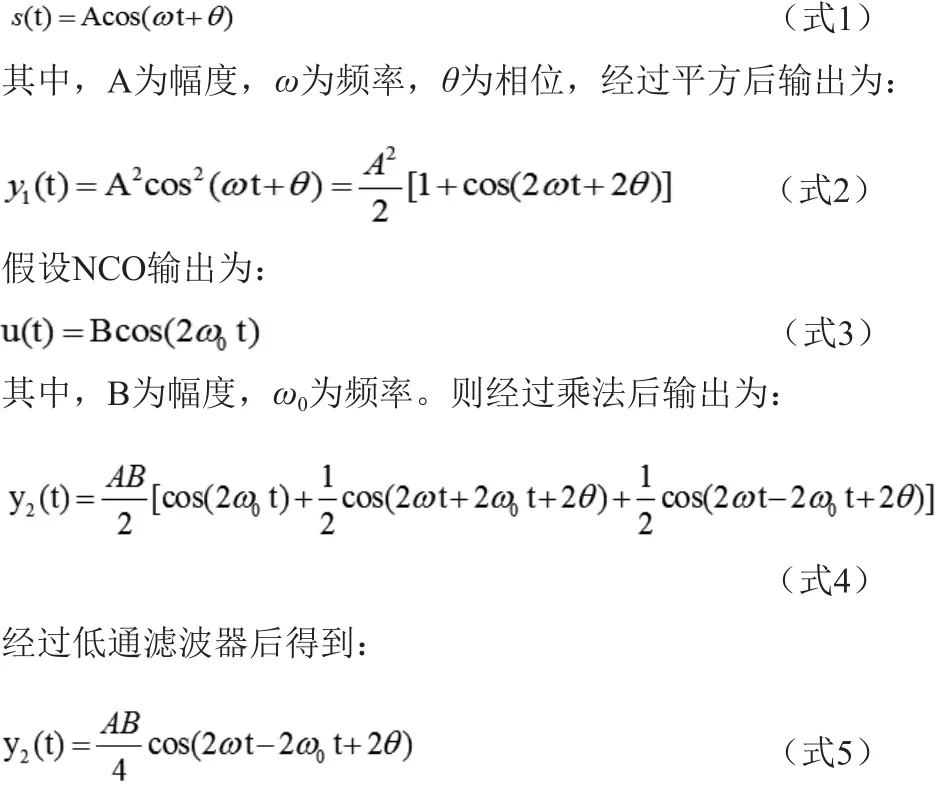

以上介绍了平方环的基本实现原理,下面对其进行公示推导:

假如输入信号为:

当ω = ω0时,低通滤波器得到直流信号,即包含原始信息且去掉载频的信号,再经归一化即得到原始信息。

由以上分析可知,平方环的处理过程完全去掉了信息符号的影响,但是NCO的输出不是真实的载波频率,而是真实载波频率的两倍,要得到真实的载频,则需要把NCO的输出进行2分频即可得到。

2.FPGA实现

FPGA是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它作为专用集成电路(ASIC)领域中的一种半定制电路出现,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。它以硬件描述语言(Verilog或VHDL)完成电路的设计,经过简单的综合、布局,快速的烧写到 FPGA 上进行测试,是IC设计验证的主流技术。能够实现一些基本的逻辑门电路(如AND、OR、XOR、NOT)或者更复杂的组合电路(比解码器或数学方程式)。内部具有丰富的逻辑资源,如可编程输入输出单元、可配置逻辑块、数字时钟管理模块、嵌入式块RAM、丰富的布线资源、底层内嵌功能单元、内嵌专用硬核等。

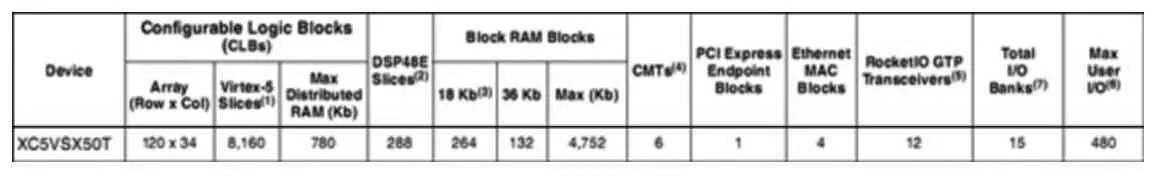

FPGA选择使用Xilinx公司的Virtex-5系列的XC5VSX50T。Virtex-5系列FPGA是全球首款采用65nm工艺且基于创新的Express Fabric架构。它采用先进的第二代ASMBL(Advanced silicon modular block-高级硅片组合模块)架构。和以往产品相比,性能稳定提升35%,动态功耗降低35%,面积缩小45%。而本次选择的Virtex-5系列中XC5VSX50T主要针对的是信号处理方面的应用,该型号的FPGA资源情况见下表1。

表1 Xilinx Virtex-5 FPGA XC5VSX50T资源分布表

XC5VSX50T内嵌的RocketIO GTP收发器模块可实现100Mbit/s-3.75Gbit/s范围内数据稳定传输,为信号预处理后向通用信号处理板传输的高速链路设计提供了方便;该芯片内含6个CMT模块,每个CMT模块包含2个DCM和1个PLL,为复杂的时钟网络设计提供了方便;同时,780Kbit的分布式RAM与4752Kbit的Block RAM为设计提供了足够的缓存空间;8160个Slices和550MHz的工作时钟频率为高速处理的逻辑控制提供了保障。内部高达288个DSP48乘法器,是信号处理的强大硬件支撑。FPGA在本设计中承担最主要的信号处理工作,主要原因就是借助了该FPGA高速、强大的运算能力。

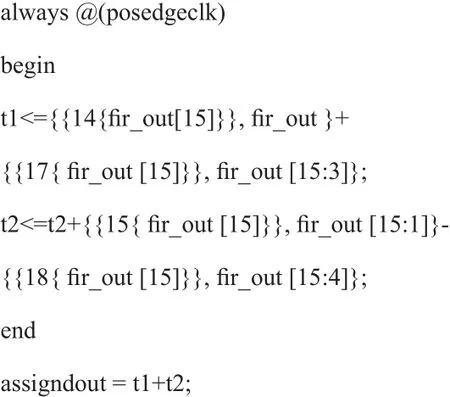

在FPGA之内,平方操作和乘法操作都采用FPGA内的乘法IP核实现;低通滤波器采用FPGA内的滤波器IP核实现,滤波系数经过MATLAB的FDATOOL工具产生,低通滤波器的带宽与传输信号的多普勒频移有关,多普勒频移越大则带宽越大。环路滤波器采用比例积分的形式实现,采用FPGA语句实现,即Verilog语言实现[2]~[6],具体如下:

其中,t1为积分支路,t2为比例支路, fir_out为低通滤波器的输出。总的来说t1和t2越小,跟踪所需时间越长,抗噪声性能越好;t1和t2越大,跟踪所需时间越短,抗噪声性能越差。

NCO采用FPGA之内的可编程DDS核实现。它是一个数字与频率的变换装置,简单来说就是输入相应的控制字字,输出对应频率的单频信号。数控振荡器主要由三部分组成:相位累加器、数字转换器、正弦查找表。Xilinx公司FPGA提供免费的DDS的IP核,直接调用该IP核即可使用,其内部结构图如图2所示。

图2中的PINC和POFF是两个最主要的寄存器。PINC可输入相位累加值,POFF输入相位偏移值。主要用到的是PINC(相位累加值)寄存器。给PINC寄存器中输入相应的值,就能得到相应的频率值。

图2 DDS IP核内部结构图

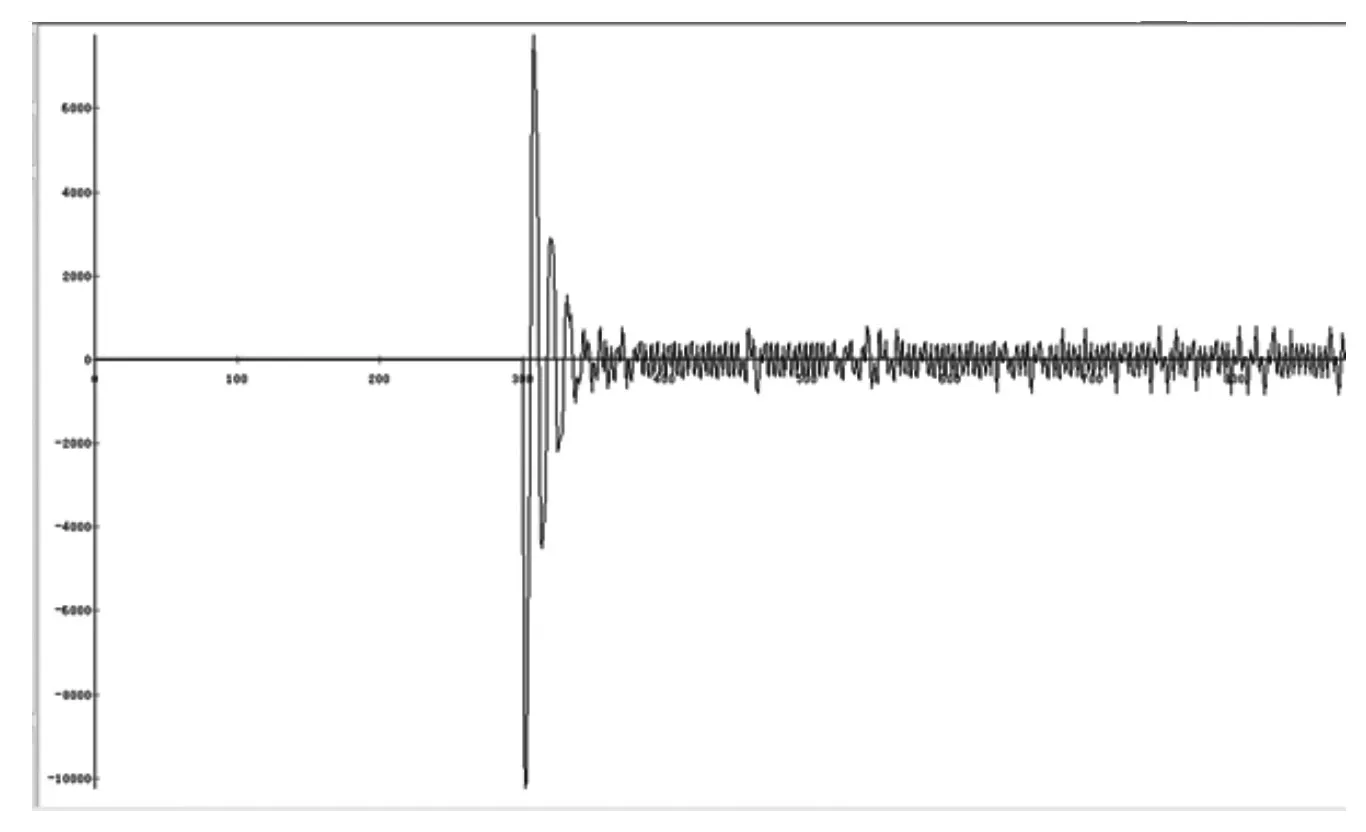

FPGA代码实现后,用MATLAB产生测试信号,输入FPGA,得到跟踪滤波器的输出如图3所示:

图3 载波提取环路滤波器输出过程

其中,在信噪比为20dB时测试的当载波能够正常提取的截图,从图中能够看出,解调过程是一个从不稳定到稳定的过程,输入信号得到了正确的解调。

3.结论

本文首先介绍了平方环的工作原理以及进行了公式推导,在理论基础上验证了平方环消除了符号的影响,得到了正确的检测。最后在FPGA上实现程序的实现,并通过MATLAB产生输入信号测试代码的正确性,达到了目的,取得了较好的效果。

[1]杨小牛,楼才义,徐建良.软件无线电技术与应用(第二版)[M].北京:北京理工大学出版社,2014.

[2]杜勇.业出版社,2014.

[3]杜勇.数字通信同步技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2013.

[4]杜勇.数字调制解调技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2014.

[5]田耘,徐文波.Xilinx FPGA 开发实用教程[M].北京:清华大学出版社,2008.

[6]XILINX.LogiCORE IP CORDIC v4.0 [EB].http://www.xilinx.com.2011.3.