一种新型低功耗C类压控振荡器设计

赵 阳,袁圣越,赵 辰,田 彤

(1.中国科学院上海微系统与信息技术研究所,上海201801;2.中国科学院大学 电子电气与通信工程学院,北京100049)

近年来,物联网技术掀起一场信息技术革命,低功耗也越来越成为物联网广泛应用的瓶颈,而物联网射频系统中VCO消耗了大量能量,因此低功耗VCO成为研究的关键。低功耗VCO一直是学术界研究的热点。在无数学者努力下,VCO的研究成果不断涌现[1-3],相比于传统LC交叉耦合VCO,C类VCO具有更好的噪声性能,更易于实现低功耗[4]。

论文提出一种新型C类PMOS压控振荡器,其动态偏置环路解决了C类VCO的起振和稳态保持问题。动态偏置环路在VCO起振后自动关闭,将VCO的偏置电压保持在固定值;文献[5]表明在电流限制范围,LC谐振回路等效并联电阻越大,VCO输出摆幅越大,噪声性能越好,故高阻值LC谐振回路的设计尤为重要。

通过后仿真验证,文中所设计高阻值LC谐振回路和动态偏置环路有效降低VCO功耗,在0.6 V供电下功耗低至0.5 mW。

1 电路结构设计与分析

1.1 C类VCO分析

C类VCO结构不同于传统交叉耦合结构,其MOS管栅极增加了两个额外电容用来隔离电源或地的电压,通过额外偏置电压给MOS管栅极提供偏压。当工作在C类状态时,VCO的电流和电压重叠范围更小[6],并且其电流效率相对AB类更高[7],因此功耗更低。另一方面由负阻理论分析可知,为了使VCO起振,交叉耦合MOS管产生的负阻必须小于等于LC谐振回路等效并联电阻2Rp。在实际设计过程中,为确保VCO起振并考虑到设计余量,一般会将设计余量因子取为2.5~3[8]。在VCO起振后,VCO只要保持gmRp≥1便可以维持振荡,此时负阻提供的能量恰好补充谐振回路的能量损耗,即VCO的起振条件要求高于其维持振荡的条件。本文所设计的VCO利用这一特性,在VCO起振后,通过动态偏置环路改变VCO偏置电压,VCO从AB类转换到C类工作,并减小MOS管跨导从而减小电流降低功耗。

VCO电流减小也导致VCO输出幅度减小,因此设计高Q值高Rp阻值的LC谐振回路,使VCO输出信号在较小电流时也具有较大摆幅。VCO输出幅度减小会导致动态偏置环路的电压发生变化,导致VCO PMOS管偏置电压不稳,甚至使VCO在AB类和C类之间循环,因此设计一种新型动态偏置环路避免VCO偏置电压的变化至关重要。

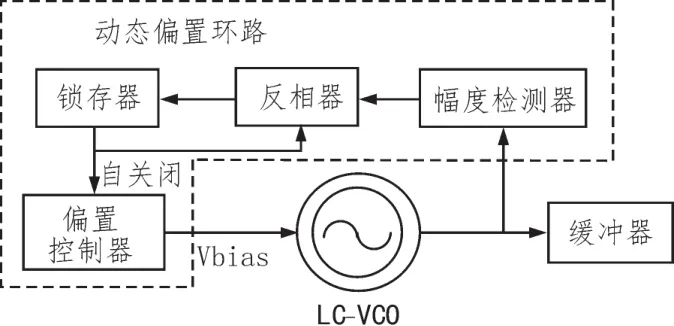

1.2 C类VCO框架图

文中所设计VCO框架结构如图1所示,动态偏置环路包括幅度检测器、锁存器、反相器,偏置控制器等模块。VCO起振在AB类状态下,此时LC-VCO的PMOS管栅极偏置电压Vbias为0 V。VCO起振后随着VCO输出信号振幅增加,其摆幅增大到一定幅度,通过动态偏置环路增大Vbias,使VCO稳定工作在低电流C类状态,随后动态偏置环路自关闭,Vbias保持特定值,VCO被锁定在C类状态工作,避免VCO起振后在AB类和C类状态之间摆动,同时隔离外界环境变化对偏置电压的影响。

图1 本文所设计VCO简化框架图

1.3 LC-VCO设计

图2所示为VCO核心电路的原理图,使用交叉耦合PMOS管产生负阻,在背栅效应下PMOS管阈值电压可降低到约0.25 V。由于PMOS管构建于N阱中,其闪烁噪声表现优于NMOS管。采用高Q值的可变电容阵列和固定电容阵列并联形式,以提高LC谐振回路等效并联电阻Rp,并获得较大的电容可调范围[9],前仿真结果表明电容电感网络等效并联电阻Rp高达 920 Ω。

图2 VCO核心和可变电容阵列原理图

1.4 可变电容分析与设计

单个可变电容的在可调范围、线性度等性能较差,采用4个变容管串联高Q值电容和四组按比例分配的直流偏置电压组成可变电容阵列,偏置电压分别为0 V,0.2 V,0.6 V,1 V,如图2所示。四组变容管的非线性相互补偿使得整体电容在较大调谐电压下具有很好的线性度,使得VCO调谐特性具有良好线性度[10],如图3所示。偏置电压可利用系统其它模块高电压进行分压得到,调谐电压变化范围也会增大。

图3 可变电容阵列调谐特性曲线

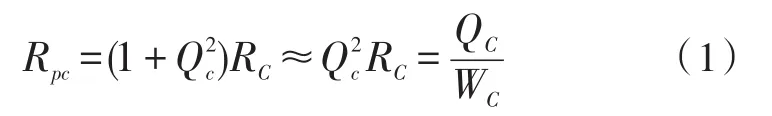

偏置电压通过大电阻抑制谐振环路影响,由公式(1)可知变容管的等效并联电阻:

在中心频率2.4 GHz附近,变容管的等效并联电阻高达十千级欧姆,因此并联电阻必须足够大才不会影响整体谐振腔的等效并联电阻Rp。

将变容管与高Q值MOM电容串联不仅可以改善VCO了频率特性曲线的线性度和调谐范围,也可以使用较大尺寸的可变电容管减小闪烁噪声。

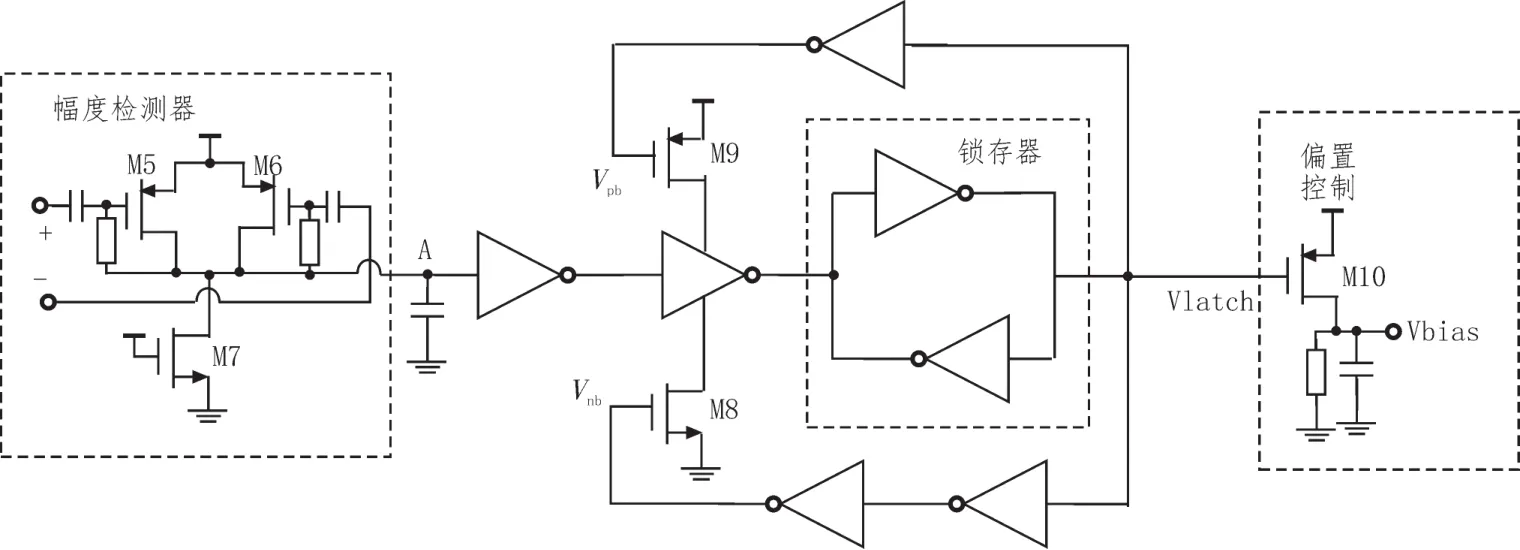

图4 动态偏置环路原理图

1.5 动态偏置环路设计

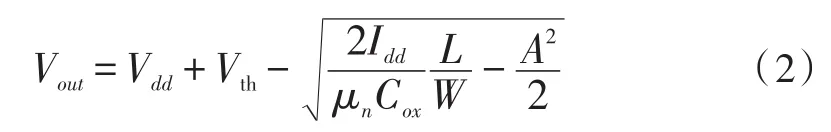

图4为动态偏置环路的原理图,包含幅度检测器、锁存器、反相器和偏置控制器等模块。振幅检测电路采用差分结构,相对单端结构,差分结构对共模噪声有较强的抑制能力。振幅检测器将射频信号幅度大小转化为直流电压输出,输入端接隔直电容,将VCO的小信号输入到M5、M6的栅极,栅极和漏级间接大电阻,因为没有直流通路,M5、M6管的直流栅源电压等于直流漏源电压。M7提供一个很小的电流,使M5、M6的栅源电压接近阈值电压。A点接一个电容相当于一个低通滤波器,维持振幅检测输出电压稳定。当VCO起振后,M5和M6的输入信号幅度增加,由公式(2)可知相应的A点电压增加[11]。

其中,A是输入正弦波的峰值,L和W是M1管的栅长和栅宽,Vdd和Idd分别是直流电压和直流电源,μn和Cox分别是电子迁移率和单位面积的栅氧化层电容。

锁存器由两个反相器首尾相接组成,将信号锁存并维持输出为特定电平状态,不随输入端的变化而变化,只有输入状态改变时输出才改变。而且锁存器环路是一个正反馈,其输出只会是0 V或VDD,确保M9完全打开或关闭,Vbias电压保持稳定。

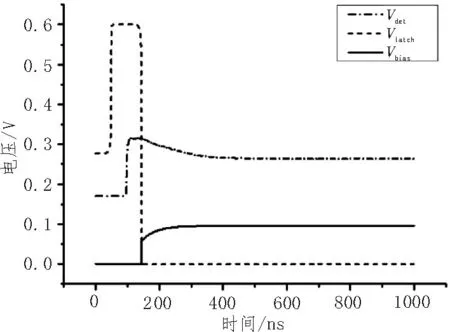

如图5所示,当VCO起振后,振幅检测输出电压Vdet升高,经反相器延时后,锁存器输出Vlatch初始化后从高电压变为低电压,低电压Vnb和高电压Vpb分别将M8和M9关闭,将偏置控制环路关闭,关闭环路后锁存器输出钳制在低电位,Vbias从0 V变为固定的100 mV左右,VCO电流也随之变化,从起振时AB类高电流状态进入低电流C类状态工作。升高Vbias仍可降低功耗,但是过低的功耗会导致VCO输出幅度过低。

图5 Vdet,Vlatch,Vbias的瞬态仿真波形

2 仿真结果与分析

采用UMC 65 nm CMOS工艺,本文所设计的VCO版图如图6所示。

图6 本文VCO电路版图

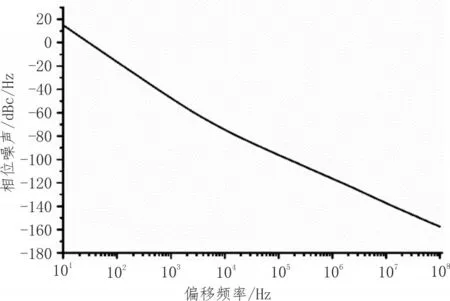

使用Cadence软件对电路进行设计仿真,在前仿真的基础上对版图进行反复的优化和调整设计参数。提取版图寄生参数后对VCO进行后仿,在0~1.2 V的调谐电压下,VCO调谐范围为2.32~2.49 GHz,且调谐线性度良好;当中心频率为2.4 GHz,在频偏100 KHz和1 MHz处的相位噪声分别为-96 dBc/Hz和-115 dBc/Hz,如图7所示;在0.6 V电压供电下,功耗仅为0.5 mW。

图7 VCO相位噪声曲线

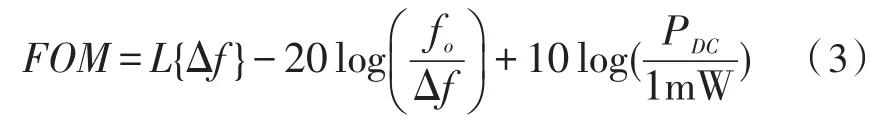

VCO的FOM值用于综合比较VCO性能的参数,其定义如下:

其中fo是VCO的中心频率 ,Δf是频偏,L{Δf}为在频偏Δf处的相位噪声,PDC是VCO的直流功耗。计算得本文设计VCO的FOM值为-186,FOM绝对值越大,VCO的综合性能越好。

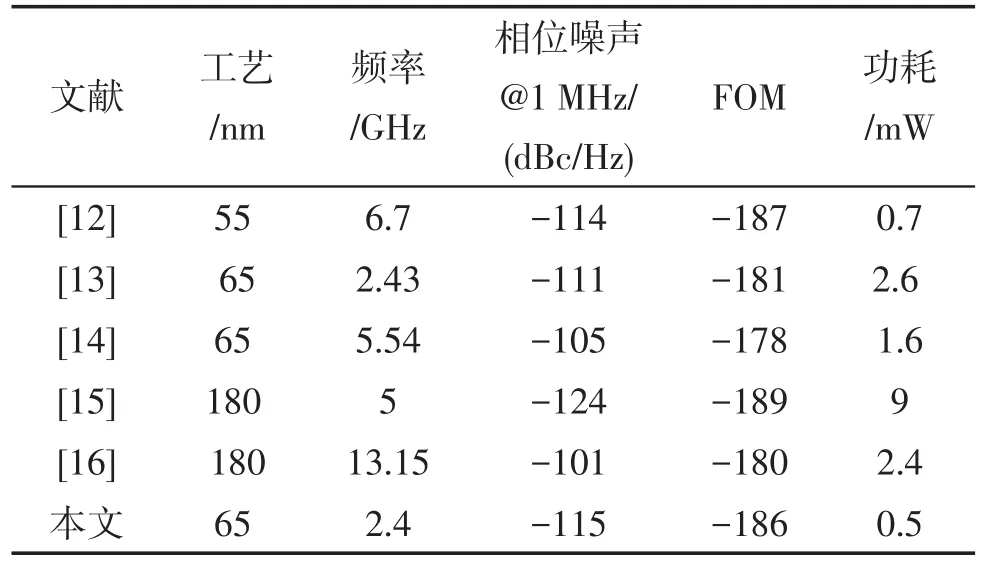

表1所示近年所发表VCO的性能对比,本文所设计的VCO功耗方面有绝对优势,相位噪声较好,FOM优良。

表1 几种LC-VCO性能参数比较

3 结论

文中为解决物联网广泛应用瓶颈而设计一款超低功耗VCO,其核心是设计新型偏置回路可以大幅度降低VCO功耗,另外设计的高Q值高阻值的LC谐振回路保证VCO输出幅度。新型动态偏置环路保证VCO在初始偏置电压下起振于AB类,通过动态偏置环路改变偏置电压将VCO锁定在C类状态,从而有效降低功耗。

[1]Shin J,Shin H.A 1.9~3.8 GHz fractional-N PLL frequency synthesizer with fast auto-calibration of loopbandwidthandVCOfrequency[J].IEEE Journal of Solid-State Circuits,2012,47(3):665-675.

[2]Kim B,Park B,Jin S.Design of an advanced CMOS power amplifier[J]. Journal of Electromagnetic Engineering&Science,2015,15(2):63-75.

[3]Perticaroli S,Toso D S,Palma F.A Harmonic Class-C CMOS VCO-Based on Low Frequency Feedback Loop[J].IEEE Journal of Solid-State Circuits,2014:1-13.

[4]Siriburanon D,Deng W,Cokoda K.A currentreuse Class-C LC-VCO with an adaptive bias scheme[J].IEEE Radio Frequency Integrated Circuits Symposium,2013:35-38.

[5]肖航.C类电压控制振荡器的研究[D].成都:电子科技大学,2015.

[6]唐攀.基于CMOS工艺的毫米波压控振荡器芯片设计[D].成都:电子科技大学,2015.

[7]王伟.基于65nm CMOS工艺低能耗低噪声LC振荡器研究与设计[D].合肥:中国科学技术大学,2016.

[8]别梅,肖巍.超宽带低相位噪声双模LC压控振荡器设计[J].中国电子科学研究学报,2016,11(4):383-387.

[9]姚婧婧,赵红东,毛键,等.锁相环电路中压控振荡器的分析与设计[J].电子设计工程,2011,19(24):177-180.

[10]Chuang Y R,Yu Y H,Lu Y C.A V-band CMOS 90nm PLL[C]//Proceedings of Asia-Microwave Conference.Nanjing:Dongnan University Press,2014:1259-1261.

[11]Yang X,Uchida Y,Liu Q.Low power ultrawideband power detector IC in 130 nm CMOS technology[C]//IEEE Microwave Workshop Series on MillimeterWaveWirelessTechnology&Applications,2012:18-20.

[12]Fanori L,Liscidini A,Andreani P.A 6.7-to-9.2GHz 55nm CMOS hybrid Class-B/Class-C cellular TX VCO[J].IEEE International Solid-state Circuits Conference Digest of Technical Papers,2012:354-356.

[13]Yang X,Uchida Y,Xu K Y.2.4 GHz-band ultralow-voltage class-c LC-VCO IC in 65 nm CMOS technology[J].Microwave Conference,2013,14(6):325-327.

[14]Ikeda S,Kamimura T,Lee S,etal.A 0.5-V 5.5-GHz class-C-VCO-based PLL with ultra-lowpower ILFD in 65 nm CMOS[C]//IEEE Asian Solid-State Circuits Conference,2012:357-360.

[15]马佳琳,张文涛,张博,等.一种面向IEEE 802.11ac标准的5 GHz LC压控振荡器[J].微电子学,2016(4):484-487.

[16]Wang Tp,Yan YM.A low-voltage low-power wide-tuning-range hybrid class-AB/class-B VCO with robust start-Up and high-performance[J].IEEE Transactionson Microwave Theory &Techniques,2014,62(3):521-531.