基于FPGA的全景视频图像拼接的设计与实现

李勇,王磊,钱罕林

(新疆轻工职业技术学院信息与软件分院,新疆乌鲁木齐830021)

近年来视频处理技术日新月异,以全景式、沉浸式用户体验为对象的视频技术开发已成为研究热点。FPGA器件以高性能、高可靠性、高运行速度、低设计周期、低成本和设计灵活等已成为视频图像处理的优先选项。目前实时全景摄像机已充分融入网络传输、云计算和大数据等新兴技术,发展迅猛。本次设计以FPGA为平台,采用SIFT算法,对系统采取优化设计,提出一种拼接全景视频图像的改进方法,旨在探索弥补在拼接中的实时性低的不足。设计中借助ARM平台来辅助进行算法换算及图像信号的压缩和网络传输,将图像拼接参数送达FPGA最小系统处理最终呈现出实时全景图像。文中重点探究FPGA平台中的全景图像的拼接模块部分。

1 视频图像拼接算法

尺度不变特征转换(ScaleInvariantfeaturetransform,SIFT)算法是由David G.Lowe创立的,它有以下几个基本步骤:

1.1 构建图像尺度空间

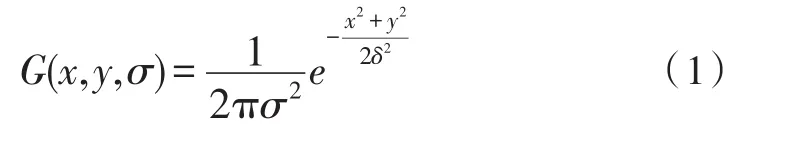

SIFT算法中对图像的尺度构建是通过高斯算子的差分算子DOG算子实现的,G(x,y,σ)为高斯算子,D(x,y,σ)为差分算子。σ是尺度因子,它的较大值表示视频图像的整体轮廓特点,它的较小值显示图像的局部细微特点。

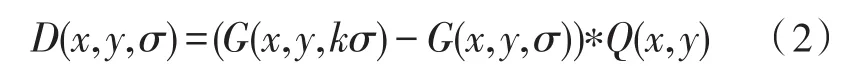

1.2 检测尺度空间关键点

由上一步可以逐渐构建高斯金字塔M组每组N层,在除第1层和第N层以外的各层像素点的邻域最值点位极值点,也叫关键点。在关键点确定以后,需要除去低对比度点。对比度由表示,由极值点X的尺度空间函数D(X)的泰勒展开求导,导数为0得,一般情况下出去的第对比度点是的极值点

1.3 确定关键点的方向

因旋转图像的不变性原则,关键点的确立需要贯以方向性描述。通常为保证画面配准精确度的需要,关键点的方向应用直方图法计算。统计区域为关键点的邻域圆,半径为1.5σ。将该圆区域均匀划分为36个扇圆,邻域点对关键点方向的参与度与二者距离成高斯递减,同时以超过直方图内80%的方向统计值作为其辅方向。

1.4 为已确定的各关键点生成特征点描述子

关键点同向坐标下,切离出16×16邻域子区域,每部分再均分为8个扇圆,根据直方图估量不同区域对象的权重。再由直方图计算统计各邻域子区域与关键点的距离得出128维向量。通过完成对所有关键点的128维向量生成,最后由相似度检测函数得出图像相似度,以实现图像配准。

2 全景视频图像拼接模块的设计及FPGA实现

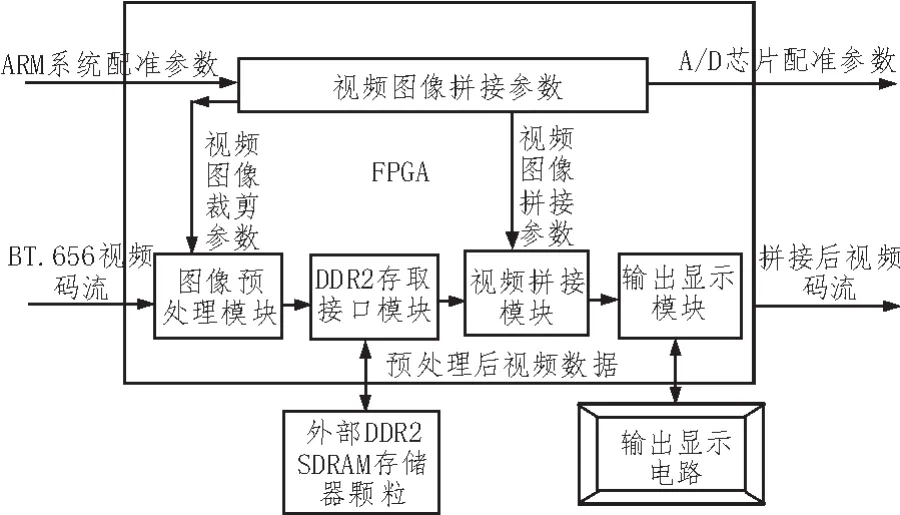

如图1所示为FPGA最小系统内主要功能整体模块设计框图。FPGA最小系统主要接受图像配准参数信号和视频码流,同时根据此参数将多路视频信号进行拼接处理形成拼接后视频码流。系统内的拼接功能模块主要依据配准参数估量图像的裁剪、缩放和移位等状态参数;DDR2 SDRAM模块为进行32bits数据的存取工作;视频拼接模块主要进行图像平移和缩放,由输出显示模块来显示输出,同时涉及后端视频信号的压缩和网络通信传输。

图1 FPGA内部各主要功能关系模块框图

2.1 图像配准参数接收模块设计

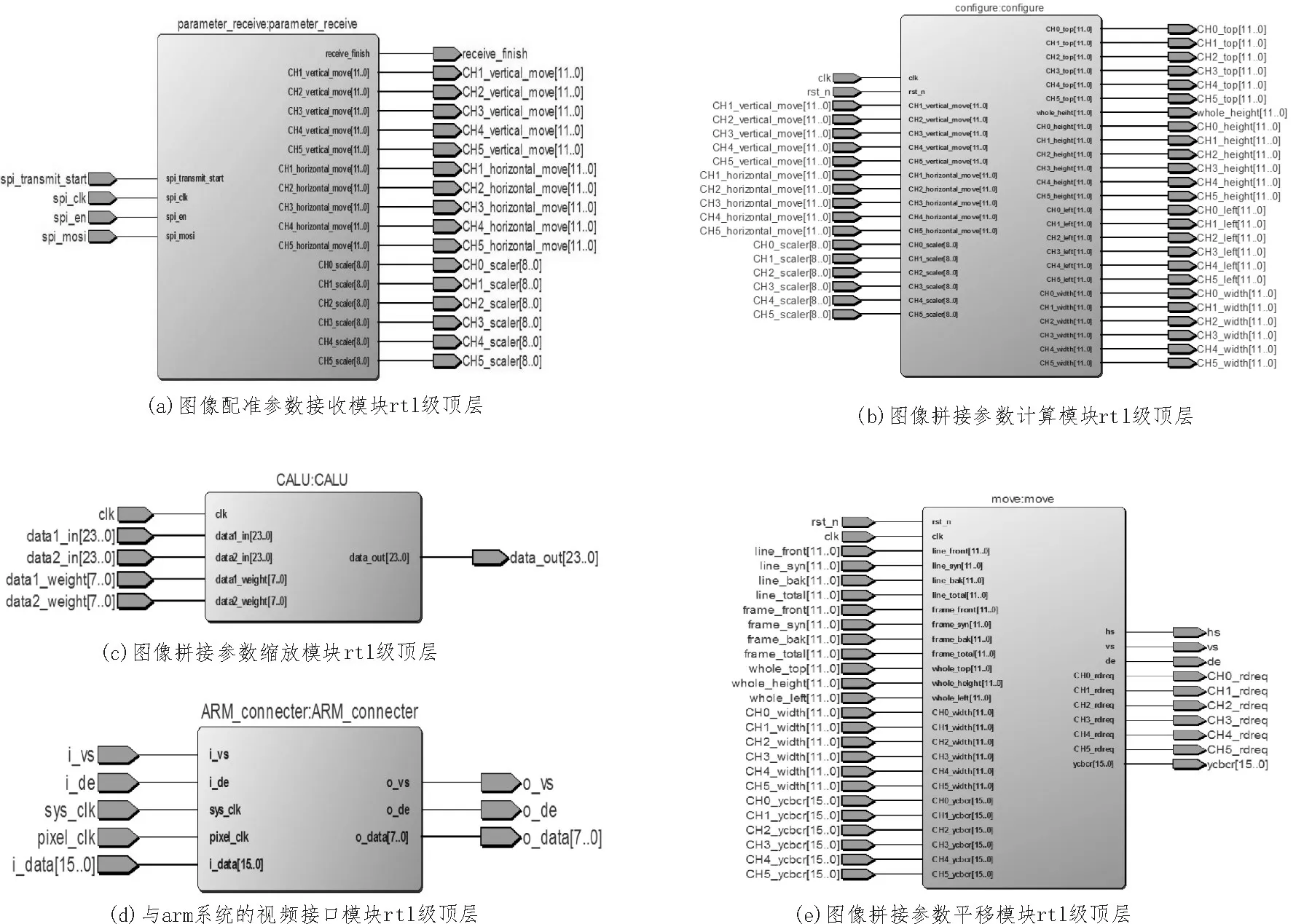

图像配准参数接收模块先变换收到的串行信号为并行信号,得到宽12 bit的配准信号,在配准信号前置有宽4 bit的配准标记。由不同的配准标志解析得到如通道垂直和水平平移及缩放参数,如图2 RTL级框图所示,spi_transmit_start信号起作用时为配准参数实际工作阶段,来完成以上处理,并从receive_finish端回复发送处理完成。

2.2 图像配准参数计算模块设计

图像配准参数计算模块主要用来处理得出图像平移及裁剪参数,而缩放参数是借助ARM系统实现的,以上都是以SIFT算法为依据的。通道1-5针对参照基,由绝对位移的最高位判定相对于通道0的移动,将最大或最小绝对位移的通道的上沿作为图像通道0-5整体的上沿。由RTL级框图,CH0_vertical_move-CH5_vertical_move表示输出通道0-5宽12 bit的相对水平位移参数信号,CH0_horizontal-CH5_horizontal则表示输出通道0-5宽12 bit的相对垂直位移参数信号。在图像拼接时为了保证实时性,需对图像冗余部分进行裁,CH0_top-CH5_top为垂直裁剪的起点。

2.3 图像缩放模块设计

模块使用双线性差值算法属于逆向映射法,DDR2 SDRAM存放原始图像,异步FIFO完成缓存用来存放待处理的数据。设计出2组RAM,每组含8×1 024 bit的RAM一个和8×512RAMbit的两个,前者寄存亮度值Y,后者寄存色差值Cb和Cr。图像缩放采取先垂直再水平的方式设计,采用状态机实现对RAM的读写,新像素值通过图像内插法采集垂直和水平状态缩放机传输出的像素值对应权值计算。如图3的RTL级框图data_weight为像素点对应的权值。

2.4 图像平移模块设计

模块由传输时序对像素阵列进行填充实现平移,如图3的RTL框图所示,参考信号传输时序和平移参数,视频图像产生同步信号(帧)vs、同步信号(行)hs和有效信号de。CH0width-CH5width为裁剪后通道0~5的图像宽度。在各通道读请求信号CH0_rdreq-CH5_rdreq发出邀请两周期后在CH0_ycber-CH5_ycber输入有效数据,处理后由ycber端输出并送入下一模块。

图2 图像拼接模块子模块RTL级顶层框图

3 视频拼接模块功能仿真

图3 模块功能仿真波形图

视频拼接模块功能仿真包含有对参数接收模块、参数计算模块、缩放和平移模块以及与ARM的接口模块等的仿真。

Spi_transmit_start信号起作用后,参数接收模块开始工作。receive_finish信号呈1时此接收工作完成。接下来,图像拼接计算模块依据此参数结果快速计算平移和裁剪参数。视频图像缩放模块在缩放时在像素点和权重值输入的3个时钟以后得出新的像素。根据拼接参数完成0~5路图像的平移。

CH0_rdreg-CH5_rdreg六路读申请信号时序与平移参数的准确协作保证了视频图像的平滑输出,然后送入ARM系统。

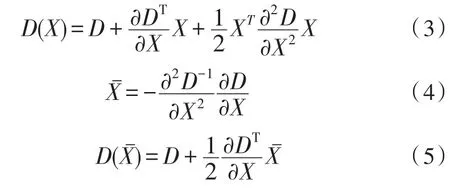

图4 实时全景视频拼接在板调试结果

如图4所示为在板调试结果画面,全景视频图像经由Quartus II EDA综合的sof文件被载入FPGA芯片实现在板调试后显示图像整体拼接效果达到预期。

4 结束语

本次设计成功实现了一种FPGA与ARM的协同配合的方法,基于SIFT算法,由ARM计算图像配准参数,再由FPGA根据参数完成缩放、平移等拼接处理,快速有效地实现了对全景视频图像的拼接。因为多端全景摄像机的结构固定,其产生的系列图像相对稳固,基于此特点而对画面拼接前的配准过程进行了简化,以精简算法和转变工作方式为突破进行了一种新的尝试,有一定的应用研究价值和借鉴意义。

[1]贡镇.基于FPGA的实时视频图像采集与显示系统的设计与实现[J].现代电子技术,2013,36(13):46-48.

[2]陈全兵.基于FPGA的高清实时全景视频拼接的研究与设计[D].成都:电子科技大学,2015.

[3]冯雁军,周清海,孙伟昶,等.FPGA平台的实时全景视频系统设计[J].电子产品世界,2013(2):72-74.

[4]张雄辉,郑力新,周凯汀.基于区域划分的快速图像插值算法[J].微型机与应用,2013:38-40.

[5]陈全兵,习友宝.基于双线性内插算法的多路视频的缩放设计[J].电视技术,2015,39(1):43-46.

[6]Donald G.Bailey.Digital for embedded image processing on FPGA[M].原魁,何文浩,肖晗.北京:电子工业出版社,2013.

[7]Meyer-baese U.Digital signal processing with field programmable gate arrays,third edition[M].刘凌,译.北京:清华大学出版社,2012.

[8]Richard E.Woods,Steven L.Eddins.Digital Image Processing Using MATLAB[M].北京:电子工业出版社,2012.

[9]何宾,陶丹,彭勃.高实时性F-SIFT图像拼接算法[J].红外与激光工程,2013,42(2):440-444.

[10]崔得龙,弓云峰,左敬龙.基于改进SIFT的图像拼接算法[J].电子设计工程,2013,21(2):34-37.

[11]党建武,宗岩,王阳萍.基于SIFT特征检测的图像拼接优化算法研究[J].计算机应用研究,2012,29(1):329-332.

[12]谭杰,王殊轶.基于Halcon的图像拼接算法研究[J].微电子学与计算机,2011,28(12):184-187.

[13]宋佳乾,汪西原.基于改进SIFT特征点匹配的图像拼接算法[J].计算机测量与控制,2015,23(2):512-515.

[14]熊苗苗,王鹏.基于SIFT算法的图像拼接技术[J].数字技术与应用,2016(11):129-130.

[15]杨磊,任龙.基于FPGA的大视场图像实时拼接技术的研究与实现[J].红外与激光工程,2015,44(6):1929-1935.

[16]张洋,李庆忠.一种多摄像机全景视频图像快速拼接算法[J].光电子·激光,2012,23(9):1821-1826.

[17]黄沄,罗明伟,张鹏.一种含有常数项的新超混沌系统及其FPGA实现[J].重庆师范大学学报:自然科学版,2015(1):116-120.

[18]陈军.基于FPGA的FFT变换分析与电路设计实现 [J].工业仪表与自动化装置,2016(1):40-42.