集成电路的失效物理的相关检测研究

宋钦泽

(辽宁科技大学 辽宁 鞍山 114000)

集成电路的失效物理的相关检测研究

宋钦泽

(辽宁科技大学 辽宁 鞍山 114000)

随着我国半导体技术的成熟,集成电路市场的拓展也一步一步的不断加快,而传统的“预计手册”虽然能够有效的检测产品的性能和可靠性,但无法准确的检测集成电路的更新周期和使用范围。因此可靠性的物理预计方法开始逐渐的替代“预计手册”,成为集成电路检测的有效手段。但是物理预计方式在集成电路的时效性和失效分布上存在一定的缺失,如何通过失效物理机制提高物理预计方法的检测集成电路,直接关系到集成电路的运用。

集成电路;失效物理;检测

1 引言

随着我国半导体市场的成熟和发展,半导体不仅仅在重要工业领域或者高新企业得到广泛的应用,还更加生活化和日常化,进入了人们日常生活的方方面面。尤其是在民用和商用的市场应用中,半导体的可靠性成为衡量集成电路相关产品使用效率和产品功能的重要标准。而随着集成电路可靠性要求越来越高,如何能够提高产品性能和可靠性之间的平衡和检测,成为生产厂商和集成电路设计者共同关注的问题。而其中,如何检测集成电路的失效物理状态成为保证集成电路行业发展的一项重要的标准。

2 失效物理

失效物理是一种研究电子产品失效原因机理的科学,主要研究各类电子产品在工作、环境和时间等应力下产生的关系与规律,同时进一步在原子和分子的水平上探讨和分析电子元件和材料失效情况发生时的过程和机理。对集成电路进行失效物理分析主要是为了能够将电子元件的可靠度依赖化学和物理的方法进行测量,检测零件或者产品的失效机理,从而有效的减少或者彻底消除电子元件失效现象的发生,从而确保集成电路在投入生产与生活时能够安全可靠。因此失效物理的检测和分析可以说是十分重要的一个环节。

失效物理研究和分析主要包括6个步骤,第一,调查失效产品和收集失效数据,包括失效的时间、环境、条件以及现象等,了解其盈利情况。第二,鉴定失效模式,将被观测失效的产品现象进行分类,了解其失效现象与同产品的嗯啊一部分有直接关系。第三,描述失效特征,包括形状、大小、位置、颜色等,除此之外还包括产品的机械结构、物理以及电性能等。第四,假设失效机理,根据受检测的失效产品特征,结合其材料的性质和制作工艺进一步分析产生失效情况的内因和外因。第五,验证,验证前一步失效机理的正确性,如果失效机理不正确则重新假设另一种失效机理,重复第四、五部开始验证。

3 四种集成电路检测模型

3.1 热载流子注入

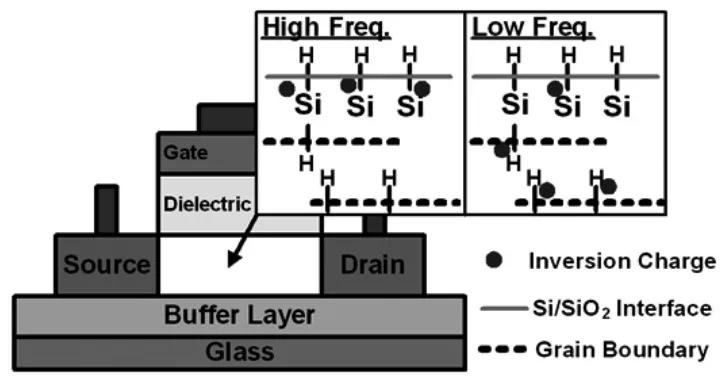

热载流子注入即HCI,电路MOS的管阈值电压变化或出现不稳定、影响集成电路的跨导性能退化等原因,容易造成电路最终失效,而热载流子注入是很好检测这一失效原因的方法,这一检测手法的物理模型表现在使用MOS沟道中载流子在横向电场中的加速变化,造成Si-SiO2界面变化,尤其是当这一界面产生陷阱时,器件中的电场分布开始变化,迁移率也产生显著的不同,此时的器件在阈值电压上明显退化,即可以判定失效的发生。

在集成电路中,热载流子注入变现在两个主要的方面,其一是器件中的非线性速度与电场的关系,即当Si中的载流子在高电场中时,会出现漂移速度的饱和现象。此时热载流子会发射光学波声子,产生热量,集成电路中的GaAs被加热,其散发的能量增加,就会造成集成电路中产生负阻现象,形成非线性速度-电场的关系。

其二是碰撞电离效应:电子器件中的热电子和晶格产生碰撞,这种碰撞让原本稳定的价键被打破,价电子激发导带,使期间中产生电子-空穴的作用。α与电场E有指数关系:α=Aexp(-Ei/kTe)=Aexp(-B/E)。碰撞电离在满足能量和动量守恒后,产生击穿现象,从而产生失效表现。见图1。

图1

3.2 负偏压温度不稳定性

负偏置温度不稳定性即NBTI,这是一种影响半导体,尤其是金属氧化物半导体效应管使用状态的可靠性的原因,受到负偏置温度不稳定的影响,电子器件的阈值电压容易发生偏移。这种失效机理一般发生在PMOS器件中。反应-扩散模型认为,负偏压温度不稳定的发生是受到负棚压和高温度的共同作用,造成继承电路中的沟道空穴的Si-H键断裂,这种断裂现象在NMOS中很少发生,在NMOS中沟道的空穴较少因此很少受到NBTI的影响,但PMOS器件中,沟道空穴众多,且器件长时间偏置于负偏压状态下,Si-H键一旦断裂H原子将会脱离并随着界面电场分散游走在界面中,形成带正电子的陷阱。当负偏压解除后,H原子再次扩散回到界面处,形成恢复过程。见图2。种氧化层缺失现象,由于氧化层的缺陷进一步积累,集成电路出现导电通路。与时间相关的介质层击穿表现为渗滤模型,这一模型指出,与实践相关的介质层击穿往往发生在期间最薄弱的环节发生断裂,如果器件中一个链条是由n个环状结构构成,那么这些环状结构之间的强度应该是相互独立且性质相似的,但如果出现了链条的断裂,一定是这些结构中有一环出现了强度的变化,且这种强度变化只能是减弱,成为最弱的一环。见图3。

图2

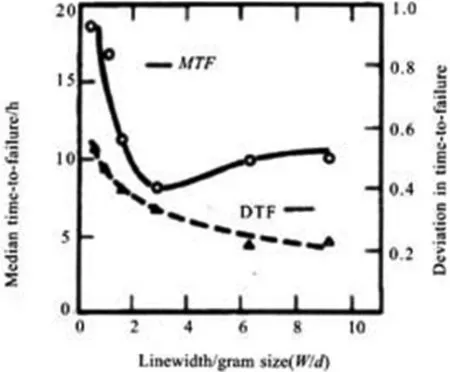

3.4 电迁移

电迁移通常是集成电路的器件在受到电场影响下,器件内的导电离子发生运动,造成了电路的整体失效。电迁移又简称EM,在集成电路中,当有电流在导体中流动时,会有大量的电子定向移动,造成集成电路中形成一种推力,推动着晶格原子向着电流的反方向流动。在集成电路中,如果导体的空洞不断增大容易造成导体截断,使电子器件失效。在集成电路中,电迁移能产生的区域很多,互连线的窄颈以及拐弯和层与层之间的接触孔等多部位产生失效现象。如果MOS器件中的数量为N,则会有2N个接触孔,也就会发生EM失效的情况。电迁移的物理机理模型表现为寿命模型。见图4。

图4 MTF和DTF(σ)与W/d的关系

3.3 与时间相关的介质层击穿

与时间相关的介质层击穿其实是在微电子技术中的一种电击穿特性,主要发生在氧化层较薄的位置,这种与时间相关的介质层击穿出现时,击穿与陷阱会造成穿越氧化层的相关电荷停留,造成氧化层的进一步损伤,缩短氧化层的寿命。而这种现象的发生也直接的表现在氧化层寿命的长短。与时间相关的介质层击穿简称为TDDB,与普通的过应力击穿不一样的是,与时间相关的介质层击穿是一

4 集成电路的失效分布

随着我国集成电路的器件制造和原理发展越来越深入,对集成电路的失效分布研究也越来越深入。从理论研究和实践发展来看,现今的集成电路失效机理已经不仅仅是某一个失效机理的影响产生的,而受到了两个或多个失效机理的共同影响产生的。尤其是为了能够保证器件功能的有效发挥,一个集成电路中的MOS器件数量也越来越多,这就造成失效机理发生的概率越高,且失效机理的共同作用越明显。但是在一个电路中,失效机理往往是相互不影响,只要一种失效机理出现,整个集成电路就会总体失效。在我国工业制作的过程中,往往更希望能够在产品的使用周期内检测到一个失效率值,从而帮助使用者或者设计者比较不同的继承电路产品之间的优劣。

在生产和使用过程中,每一个集成电路的晶体管应力时间为t/2,在整个工作时间t内,NMOS与PMOS的实际工作时间则应该是总应力时间的一半。因此可靠性的物理预计方法开始逐渐的替代“预计手册”,成为集成电路检测的有效手段。但是物理预计方式在集成电路的时效性和失效分布上存在一定的缺失,如何通过失效物理机制提高物理预计方法的检测集成电路,直接关系到集成电路的运用。

[1]陈云霞,谢汶姝,曾声奎.功能分析与失效物理结合的可靠性预计方法[J].《航空学报》,2008年05期.

[2]雷瑾亮,张剑,马晓辉.集成电路产业形态的演变和发展机遇[J].《中国科技论坛》2013年07期.

[3]杨道虹.我国集成电路产业自主创新生态系统研究[J].电子工业专用设备,2008年09期.

[4]2007年中国集成电路产业发展研讨会暨第10届中国半导体行业协会集成电路分会年会征文参考题[J].半导体行业;2007年01期.

[5]2007年中国集成电路产业发展研讨会暨第10届中国半导体行业协会集成电路分会年会征文参考题[J].半导体行业;2007年04期.

[6]关白玉.中国集成电路行业现状与发展[A].第二届高新技术用石英制品及相关材料技术与市场研讨会论文集[C].2004年.

TN406 【文献标识码】A 【文章编号】1009-5624(2018)02-0091-03