一种面向Video Over IP系统的锁相式同步技术*

周江燕,陈 鑫,张 颖

(南京航空航天大学电子信息工程学院,南京 210000)

一种面向VideoOverIP系统的锁相式同步技术*

周江燕,陈 鑫*,张 颖

(南京航空航天大学电子信息工程学院,南京 210000)

提出了一种锁相式同步技术,以解决Video Over IP大屏拼接系统中多节点同步问题。整个同步系统采用主从式结构,主节点通过广播包方式发出全局网络同步帧信号,各分布式节点通过基于锁相环原理的闭环控制系统将各自的上屏帧信号与网络同步帧信号进行锁相处理。提出的锁相式同步技术,锁相范围为-π ~+π,并采用多模式跟踪方式兼顾了锁相速度和锁定后稳定度。通过FPGA硬件平台验证及示波器实际测试,同步精度达±1 μs,相位最大锁定时间约为34 s。

大屏拼接系统;锁相式同步技术;闭环控制系统;多模式跟踪方式

由于超大规模尺寸的显示器价格居高不下,且显示器的边框越来越窄直至肉眼难以察觉,大屏拼接显示系统在指挥控制中心、大型会议室、大型商场等众多场所得到了广泛运用。传统大屏拼接显示系统主要基于显卡将视频信息拆分和缩放,然后通过视频线向各个节点传送视频流。但是受限于显卡性能,传统大屏拼接显示系统传送距离近[1],大屏节点数目少,以Nvidia的NVS810专业多屏显示卡为例,单卡最大只能支持8个节点。

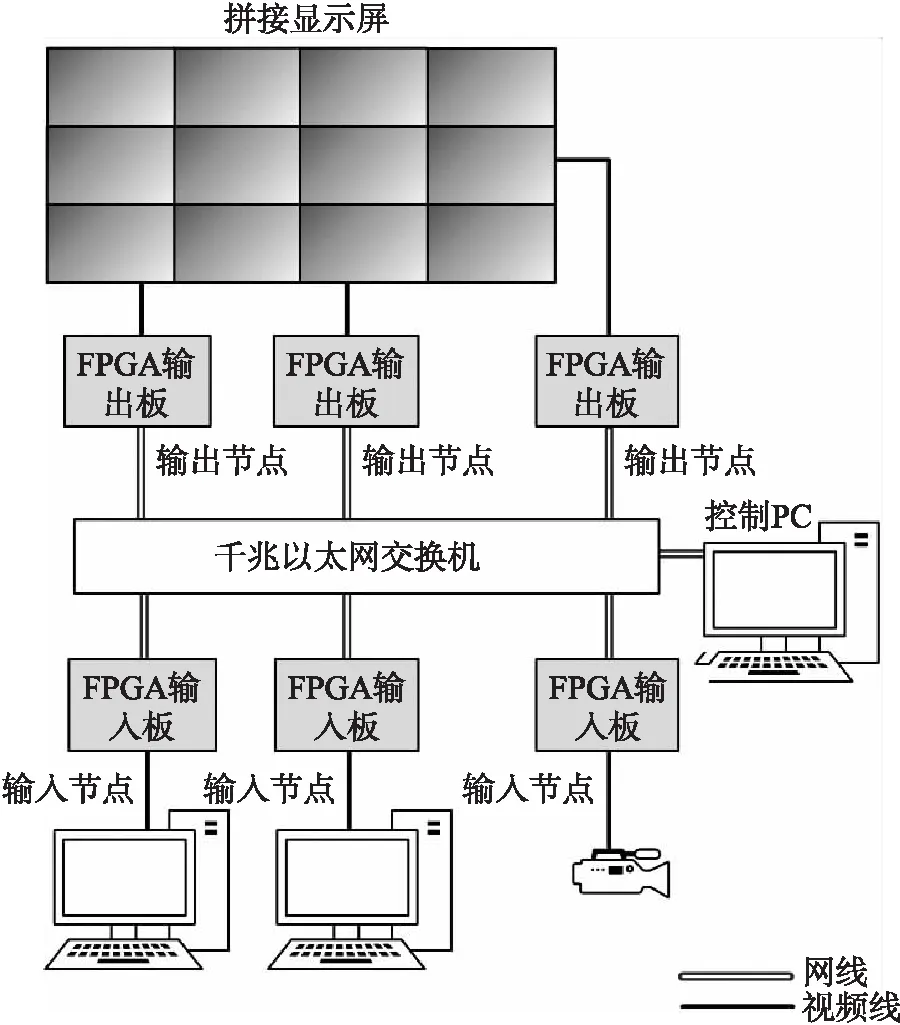

为了解决传送距离近和节点数目少的问题,基于Video Over IP的大屏拼接系统解决方案应运而生,其结构图如图1所示。整个系统包括视频源、输入节点、输出节点、以太网交换机和分布式显示器。输入节点和输出节点均通过视频线分别连接视频源和显示器,均通过网线与交换机相连。输入节点接收上位机软件所发的指令,将用户需要显示的视频经由交换机发送至指定输出节点,以任意拼接或缩放方式送到指定分布式显示器屏幕上。

图1 基于Video Over IP的大屏拼接系统结构

从上述介绍可知,基于Video Over IP的大屏拼接系统能以较低的成本和系统复杂度,实现长距离多节点的大屏拼接系统。但是,由于大屏拼接显示系统的各个节点电路都是彼此独立的,基于Video Over IP的大屏拼接系统引入了分布式系统中无法规避的同步性问题。例如:

(1)各个节点上电不同时造成的不同步。各硬件上电时刻不同,造成初始相位差。

(2)晶振独立造成的不同步。各板晶振相互独立,晶振受电路性能、温度等因素的影响,任意两个晶振都会有独立的频率和相位,经过长时间的积累,各分布式节点会形成很大的相位差异[2-4]。

(3)网络中断造成的不同步。在系统运行过程中,由于交换机或者网线等硬件故障引起网络中断,导致各节点失去了同步基准,引起不同步问题。

各个节点电路的不同步现象会直接反映为大屏显示系统中显示图像的同步性效果,直接决定了大屏拼接显示系统的观感和显示效果。

传统大屏拼接显示系统的同步方案主要围绕显卡实施,具体有硬件和软件两种实施方案:

(1)硬件同步的典型代表是NVidia的Quadro系列显卡。其同步方案可以精确到扫描线以下水平,即在刷新率120Hz且显示分辨率1080P的条件下精确度可达±10 μs[5]。尽管专用硬件同步解决方案精确度高,但其硬件价格昂贵,且采用菊花链的连接方式,一个从设备出错后,则会导致整个同步系统失效[5]。

(2)软件实现方法只需使用普通消费级显卡,采用计算机软件实现多个显示器同步,例如Linux下的GenLock软件或Windows下的WinSGL软件[5-7]。以WinSGL为例,时钟主节点采用外部专用硬件设备,从节点通过调整垂直前端扫描(Vertical Front Porch)的时间调整显卡Video Timing(视频时序)以实现多个显示器之间的帧同步。WinSGL软件同步精度可达±30 μs[5-7]。

对于基于Video Over IP的大屏拼接系统,由于缺乏一个管理整个系统的显卡硬件,所以无法采用上述两种实施方式来实现节点同步。为了解决这个问题,最近工程师提出了时间戳同步方案。该方案常采用NTP或IEEE1588(简称PTP)协议算出主从时间偏差,再由各节点处的电路通过调整本地信号或时间以保持与主节点时钟的同步性[8-10]。该方案同步精度高,缺点是需要视频流中加入时间戳,增加了系统实施复杂度。

针对上述问题,本文基于FPGA硬件,提出一种适用于Video Over IP大屏拼接系统的锁相式同步技术。本方案中,由于各从节点接收网络同步帧信号经过了相同的路径,因此,可忽略网络延时造成的误差,无需加入时间戳。主从式结构与菊花链连接方式相比,抗干扰能力强。晶振调节方式与调整垂直前端扫描时间的方式相比,不会引起多达数秒的黑屏现象。

1 锁相式同步技术的工作原理

锁相式同步技术的工作原理如图2所示。

图2 基于锁相同步技术的闭环控制系统结构框图

整个系统结构包括快速数字鉴相器、PWM同步控制器、RC低通滤波电路以及时钟模块。网络同步帧信号由主节点发出,从节点将接收到的网络同步帧信号与本地上屏帧信号经过快速数字鉴相器后,获得两者的相位关系,PWM控制器根据相位关系调整PWM的占空比。PWM为脉宽调制信号,经过RC低通滤波电路后,高频分量被滤除,留下直流分量,作为压控晶振的控制电压[11]。压控晶振输出时钟经过FPGA的pll IP核倍频后,以此为基准时钟产生上屏时序。其中V_sync信号作为反馈信号送回快速数字鉴相器模块。上屏帧信号的相位决定了显示画面的切换时刻,因此,实现各节点同步的关键是实现上屏帧信号的同步。

2 基于锁相同步技术的闭环控制系统结构

2.1 快速数字鉴相器

快速数字鉴相器主要功能是鉴别网络同步帧(Frm_sync)与本地上屏帧信号(V_sync)的相位关系[12]。

具体实现过程如下:

由于网络同步帧和上屏帧信号都是低频周期信号,以本地高频时钟(Local_clk)对以上两信号进行周期计数,可得到一周期内的时钟数,分别为Frm_sync_cnt以及V_sync_cnt。由于网络同步帧长期稳定度高,可计算其多个周期的平均值,得到稳定的周期时钟数Frm_sync_period[2]。比较V_sync_cnt与Frm_sync_period,可得到当前帧频率差值以及当前晶振频率偏高或偏低情况。

具体获取相位差以及通过比较获得相位超前落后信息的过程如图3所示。Pha_error表示相位差信号,Pha_error_cnt表示由本地高频时钟Local_clk对相位差信号的计数值,Pha_result表示鉴相结果。

图3 鉴相过程时序图

上屏帧信号频率一般为60 Hz,网络同步帧信号频率与之同频或为上屏帧信号频率的一半。图3以网络同步帧60 Hz为例,给出了鉴相过程以及获取相位超前落后信息的波形图。Frm_sync上升沿使Pha_error置“1”,V_sync上升沿使Pha_error置“0”,得到高电平宽度与相位误差成正比的信号。以本地高频时钟Local_clk对相位误差高电平进行计数,计数结果Pha_error_cnt维持至下一个鉴相周期,在Frm_sync的上升沿清零,进行新一轮计数。

相位判断时机为V_sync信号脉冲到来后,若相位差计数值Pha_error_cnt小于网络同步帧平均计数值Frm_sync_period的一半,则相位落后;反之,则相位超前。网络同步帧为60 Hz情况下相位结果Pha_result的值判定按式(1),“0”表示相位落后,“1”表示相位超前。网络同步帧为30 Hz情况下相位结果判定按照式(2)。

(1)

(2)

以上鉴相方法的鉴相范围为-π~π。能将V_sync向距离最接近的Frm_sync方向同步,更节省同步时间。

实际应用中,上屏帧信号V_sync需要稳定落后于网络同步帧信号Frm_sync,因此,可延迟相位误差信号Pha_error置“1”一定时间Tdelay,即可在同步过程稳定后,使得V_sync相位落后于Frm_sync,且保持稳定的相位差。

2.2 PWM同步控制器模块

压控晶体振荡器的输出频率可通过改变输入电压来调整,输入电压与输出频率基本呈线性关系[13-14]。通过PWM及低通滤波电路可以实现对压控晶体振荡器输入电压的控制[11]。本小节主要研究如何调节PWM以控制压控晶振以达到快速锁相的目的。

PWM同步控制器模块主要功能是根据前级所获取的相位信息,控制FPGA所输出的PWM波的占空比。快速数字鉴相器的结果有以下4种情况:

(1)本地相位超前,上屏帧频率低于网络同步帧频率。偏低的频率拉长了帧周期,则相位超前问题会在下个周期得到改善。

(2)本地相位超前,上屏帧频率高于网络同步帧频率。偏高的频率缩短了帧周期,会加剧相位超前问题,因此需要降低PWM波占空比以降低压控晶振频率。

(3)本地相位落后,上屏帧频率低于网络同步帧频率。偏低的频率拉长了帧周期,会加剧相位落后问题,因此需要提高PWM波占空比以提高压控晶振频率。

(4)本地相位落后,上屏帧频率高于网络同步帧频率。偏高的频率缩短了帧周期,则相位落后问题会在下个周期得到改善。

第1种和第4种情况下,不需要调整PWM占空比,便可经过多个周期积累,去除相位差;第2种和第3种情况需要调节PWM占空比以达到第1种或第4种情况。

为提高锁相速率,本文采用多模式跟踪方式:当相位差很大时,需要调整成快速跟踪模式,即调节PWM占空比以使本地上屏帧信号与网络同步帧信号的频率差值最大,以使快速锁相;当相位差很小时,需要调整成精准跟踪模式,即调节PWM占空比以使本地上屏帧信号与网络同步帧信号的频率差值最小,以保证上屏帧信号稳定性和高同步精度。

PWM占空比越高,对应的上屏帧信号频率越大。当PWM占空比为1时,对应的上屏帧信号率最大,当PWM占空比为0时,对应的上屏帧信号频率最小。通过调整PWM高电平数,可得到最接近网络同步帧频率的本地上屏帧率,对应的高电平数分别为Mhign和Mlow。

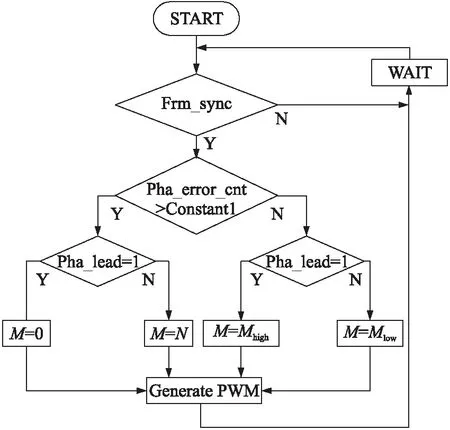

图4 基本控制流程图

图4给出了基本流程图,其中,N代表PWM波周期总时钟数,M代表周期高电平时钟数。当相位差很大时,即相位差大于参数Constant1,调节PWM高电平数,使得高电平数分别为0或者N;当相位差很小时,即相位差小于或等于参数Constant1,调节PWM高电平数为Mhign和Mlow,以进行微调。调整周期为每个网络同步帧调整一次。

2.3 PWM到电压输出电路实现

从PWM(脉宽调制信号)到电压输出的电路实现了DA转换功能,即将控制模块的调节信息转化为电压量[11]。

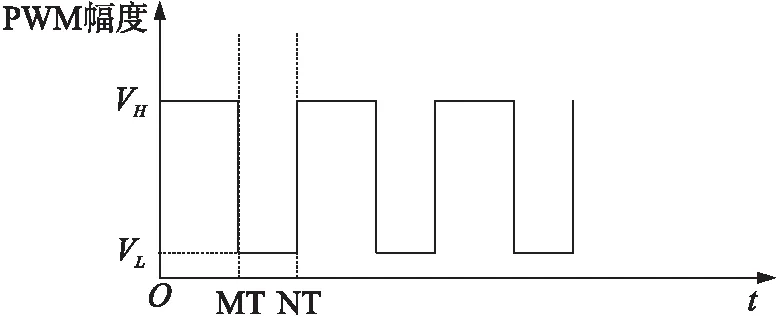

PWM是周期一定且占空比可调的方波信号[11]。本设计中PWM通过对本地高频时钟进行周期计数得到,通过调节高电平时钟数改变PWM占空比。图5中参数T表示本地高频时钟周期,M表示高电平时钟数,N表示PWM波周期总时钟数。VH和VL分别是PWM波高低电平的电压值。

图5 PWM波形

PWM信号经过RC低通滤波器后,可滤除高次谐波,留下直流分量,作为压控晶体振荡器的电压控制信号[11]。直流分量与M成线性关系,随着M从0到N,直流分量从VL到VH之间变化。当M为N/2时,即占空比为50%,输出电压为(VL+VH)/2,此时的电压为中心控制电压[11]。

周期时钟数计算公式如式(3)所示:

(3)

式中:Flocal_clk表示本地高频时钟频率,FPWM表示PWM波频率,Flocal_clk一定时,FPWM越低,N越大,则可调节范围越大;反之,可调节范围越小。可调节范围越大,PWM控制器在精准跟踪模式下调节精度越高。

假设本地时钟频率为125 MHz,若PWM波频率为2.5 MHz,则周期时钟数为50,控制输出电压的高电平时钟数可调节范围为0~50。

图6给出了PSPICE软件模拟出的从PWM到电压输出电路的实验结果,实验中设置的VH为3.3 V,VL为0 V。图为PWM波在占空比为50%时的一段截取的波形,横轴表示时间,纵轴表示输出电压值。由图6(a)和图6(b)可知,相同电路环境下,频率低易导致RC低通电路滤波效果差,输出电压纹波大。频率越高,输出电压效果越好。

因此,在选择PWM频率时,需要根据实际电路情况综合可调节范围以及滤波效果两点选择合适频率。

3 实验结果

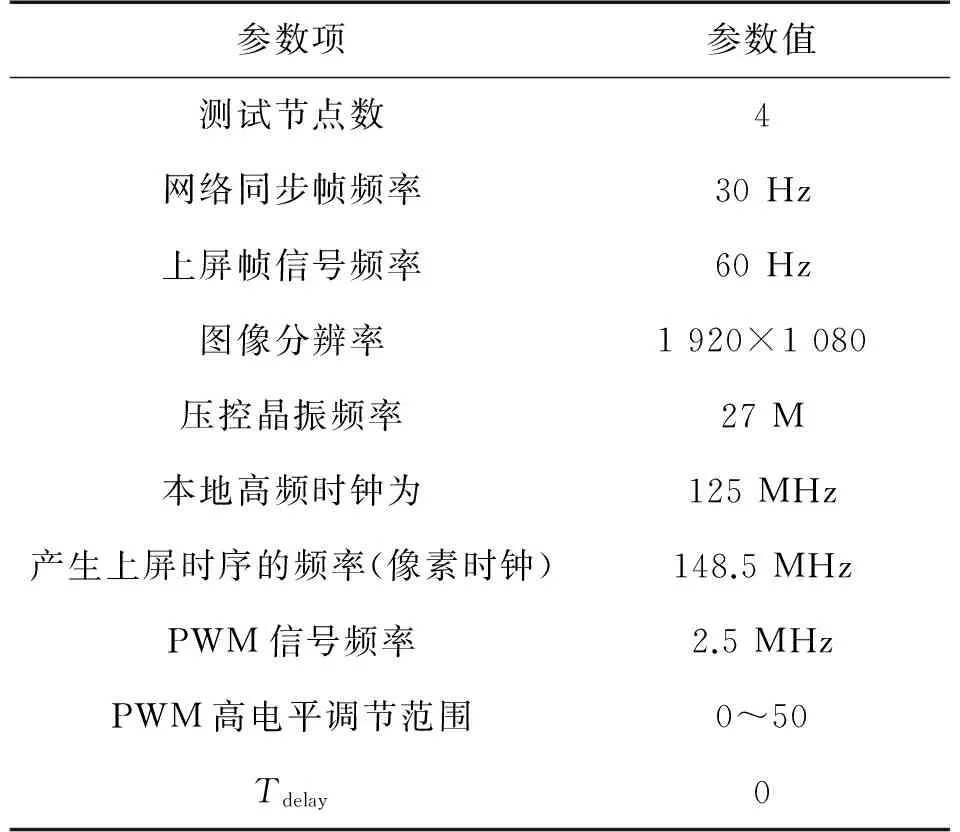

本次实验中相关参数的设置如表1所示。为方便观察,上屏帧信号稳定落后于网络同步帧的时间Tdelay设为0。

表1 实验中相关参数的设置

图7(a)是通过示波器检测到的4个输出节点上屏帧信号同步前(左)与同步后(右)的波形图。图7(b)为4个输出节点同步后,上屏帧信号上升沿的波形图。图7(c)为网络同步帧信号(上)与上屏帧信号(下)的上升沿波形图。

图7 4个节点与网络帧的输出

经过实测,相位最大锁定时间约为34 s,相位锁定后稳定度可达±500 ns,节点间同步精度可达±1 μs以内。锁定时间长短主要由相位差和晶振最大调节范围决定,由于本文所述的锁相式同步技术鉴相范围为±π,相位差最大为1/2周期,相比单向锁相方法,平均锁相时间节省了一倍。又采用了多模式跟踪方式以达到快速锁定的目的。因此,相比普通晶振调节方式,大大节省了时间。稳定度表示相位锁定后,上屏帧信号在跟踪网络同步帧时的相位抖动范围,该稳定性由精准跟踪模式下的PWM变化范围决定,变化范围越小,稳定性越好。

表2给出了该同步系统同步方式与同应用领域其他同步方式的性能比对。本方案所述同步技术相比显卡级同步技术,虽然锁相速度慢,但精度更高,且在锁定过程中不容易引起黑屏问题。在面向Video Over IP的大屏拼接显示系统中,采用IEEE1588协议同步方法,由于其考虑了网络延时在内,同步精度最高,但其实现方式复杂,在可忽略网络延时的系统中,本方案更具优势。

表2 本实验方案与其他方案的性能比较

4 结语

本文针对一套基于FPGA的以太网分布式显示系统提出一种多节点同步电路设计方案。该方案采用主从式结构,通过主节点以广播包方式发送网络同步帧信号,从节点通过一种锁相式同步技术将本地上屏帧信号同步于该网络同步帧信号。锁相式同步技术为一个闭环控制系统,通过调节本地压控晶振的方式来改变本地上屏帧信号的相位,以使得各节点上屏帧信号均同步于一个网络同步帧。本文详述了闭环控制系统的各个模块,并给出了实验结果。根据实际测试,该方案切实可行。目前的闭环控制算法基本解决了上屏同步问题,但是关于快速锁相问题还有待研究及改善。

[1] 余思琛,秦晅,成春晟,等. 基于多媒体通信的视频墙系统设计[J]. 指挥信息系统与技术,2013(6):75-79.

[2] 曾祥君,尹项根,林干,等. 晶振信号同步GPS信号产生高精度时钟的方法及实现[J]. 电力系统自动化,2003,27(8):49-53.

[3] 张华龙,叶媲舟. 调整时钟晶振的频率的方法及装置、晶振模块、芯片[P]. 中国专利,CN102510283A. 2012.

[4] 王军. 基于FPGA的压控晶振同步频率控制系统研究[J]. 电子测量技术,2012(11):83-85.

[5] Julian M. Active-Stereo Synchronization of Multiple Displays via Ethernet[D]. Saarland University,2012.

[6] Allard J,Gouranton V,Lamarque G,et al. SoftGenLock:Active Stereo and Genlock for PC cluster[C]//The Workshop on Virtual Environments. ACM,2003:255-260.

[7] Cotting D,Waschb&#,Sch M,et al. WinSGL:Synchronizing Displays in Parallel Graphics Using Cost-Effective Software Genlocking[J]. Parallel Computing,2007,33(6):420-437.

[8] 林赞. 分布式网络视频显示同步时钟的设计与实现[D]. 广州:华南理工大学,2015.

[9] 关松青. 工业以太网中IEEE 1588时钟同步技术研究[D]. 湖南:湖南大学,2010.

[10] 张艳,韩雁,霍明旭,等. 基于EPA协议的精确时钟同步方法[J]. 传感技术学报,2009,22(7):978-982.

[11] 秦健. 一种基于PWM的电压输出DAC电路设计[J]. 现代电子技术,2004,27(14):81-83.

[12] 陈鑫. 快速锁定数控锁相环的研究和设计[D]. 南京:东南大学,2010.

[13] 郑义. 分布式运动控制系统中时钟同步技术的研究[D]. 湖北:湖北工业大学,2012.

[14] 王军. 基于FPGA的压控晶振同步频率控制系统研究[J]. 电子测量技术,2012(11):83-85.

APhase-LockedSynchronizationTechnologyforVideoOverIPSystem*

ZHOUJiangyan,CHENXin*,ZHANGYing

(College of Electronic and Information Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210000,China)

To solve the problem of synchronization among multiple nodes in the Video Over IP splicing system,a phase-locked synchronization technology has been proposed. With the master-slave structure,the master node sends network frame synchronization signal,and the slave nodes make phase-locked process based on the principle of phase-locked loop(PLL). The proposed phase-locked synchronization technology provides phase-locked range from -π to +π,and implements multi-mode tracking method,which makes a good balance between phase-locked speed and phase-locked stability. Based on FPGA platform and oscilloscope test,the synchronization accuracy reaches ±1 μs,and the maximum phase lock time is about 34 s.

large screen splicing system;phase-locked synchronization technology;closed-loop control system;multi-mode tracking method

10.3969/j.issn.1005-9490.2017.06.026

项目来源:航空科学基金项目(20152052025,20140652008);超级动态电压调节技术下的信号完整性关键技术研究;国家自然科学基金(61404087)

2016-11-17修改日期2017-01-07

TN47

A

1005-9490(2017)06-1459-07

周江燕(1991-),女,汉族,江苏海门人,南京航空航天大学电子信息工程学院,硕士研究生,研究方向为数字集成电路设计,jiangyan_zhou@sina.com;

陈鑫(1982-),男,汉族,江苏句容人,南京航空航天大学电子信息工程学院,副教授,主要研究方向为集成电路设计,xin_chen@nuaa.edu.cn。