一种3层无芯基板制造过程及翘曲变形模拟和机理分析

李茂源,刁思勉,刘家欢,邓天正雄,李 阳

(1.华中科技大学材料科学与技术学院,武汉 430074;

2.深圳市烨嘉为技术有限公司,广东 深圳 518000)

一种3层无芯基板制造过程及翘曲变形模拟和机理分析

李茂源1,刁思勉2,刘家欢1,邓天正雄1,李 阳1

(1.华中科技大学材料科学与技术学院,武汉 430074;

2.深圳市烨嘉为技术有限公司,广东 深圳 518000)

制造与装配过程的翘曲问题是应用无芯基板最大的挑战之一,其主要原因是不同材料间热机械性能不匹配所造成的。介绍了一种3层无芯基板的制造过程,并利用有限元软件ABAQUS6.10对该过程进行了模拟。通过对模拟结果与实验测试结果的对比,再对翘曲变形的机理进行分析,对比了不同因素对翘曲变形大小的影响,对减少翘曲变形给出了有效的工艺设计建议。

无芯基板;翘曲;ABAQUS

1 引言

当前电子封装技术的发展趋势是集中追求更高的电气性能与更小的三维尺寸。手持电子产品的薄型化趋势对基板也要求越来越薄,无芯基板是具有广泛应用前景的下一代封装基板技术[1,2]。无芯基板也叫无核基板,是去除了芯板的封装基板,它仅保留如树脂、半固化片等的绝缘层和铜层,通过半加成积层工艺实现高密度布线[3]。目前应用无芯基板面临的最大挑战之一就是翘曲问题[4]。翘曲和残余应力的数值大小取决于材料间热机械性能不匹配度、基板的三维尺寸与结构、固化条件、层压结构的非对称性、电路图案等[5]。

有效减小翘曲会有助于改善无芯基板在生产过程中的稳定性与使用过程中的可靠性。在减小翘曲方面,研究者们做了许多工作。Kim[6]等提出了通过优化基板结构设计、在回流过程中加入导热夹具、降低积层绝缘材料与铜材料之间的CTE差值等措施来减少翘曲,并对此进行了模拟与实验验证。Mamoru Kurashina等人[7]对比了由2种积层材料组成的无芯基板结构,4种不同排布结构在热循环实验条件的翘曲变形,并通过有限元模拟,结果表明可以通过优化积层与铜层排布序列降低翘曲变形。本文针对一种对称的3层无芯基板制造工艺,利用有限元软件ABAQUS6.10进行建模仿真,模拟计算出在每一个工艺步骤后的翘曲值,再通过对翘曲变形机理与模拟结果的分析,对无芯基板的三维尺寸与铜层残铜率大小进行研究,利用模拟对比两种因素对翘曲变形的影响。

2 无芯基板制造工艺流程

图1描述了一种制造3层无芯基板简易的工艺流程。首先,由2层金属铜材料与1层半固化片材料热压形成载板,接着绝缘层与铜层对称地进行热压堆积。多层可以根据对基板层数的要求重复层压过程。工艺最后一步是去除载板的过程,由于工艺是对称进行的,因此一次可以得到相同的2块无芯基板,再对无芯基板进一步进行钻孔、蚀刻、增厚等步骤以完成加工。

图1 一种3层无芯基板制作流程示意图

3 无芯基板制造工艺的数值模拟

3.1 无芯基板翘曲机制分析

无芯基板发生翘曲的根本原因是由于板的内应力大于板的结构强度而造成的,其主要原因包括[6]:(1)没有芯板的支撑,无芯基板刚性不足;(2)基板各层的绝缘层材料为半固化片,层压后需要固化,同时与铜层的CTE值不匹配,在冷却过程中产生较大的热应力,在冷却室温时作为残余应力储存在基板中;(3)在分层固化、去除载板、电路蚀刻等过程中也可能使基板内部应力重新分配。在去除载板前,由于结构的对称性模型变形小,在去除载板后对称性被破坏,应力释放导致回弹,发生翘曲变形。对于多层基板的翘曲机制,可以将多层板结构简化成双层结构进行理解。如图2所示,由于上下层材料的CTE值不匹配,在升温、降温时膨胀或者收缩程度不一样,导致整体结构会向上或向下弯曲变形。S.TIMOSHENKO[8]对双层异种材料板结构在加热或者冷却过程中的翘曲变形进行了理论推导,结果表明其翘曲变形的大小与双层材料的CTE值、刚度、厚度等因素有关。同时,实际无芯基板每层材料、结构有所不同,厚度也不一致,在升温或者降温过程中的翘曲变形情况也更为复杂多变。

图2 不同CTE值的多层基板翘曲变形机制

3.2 有限模拟的基本假设

本文中有限元模拟的基本假设如下:

(1)假设各层半固化片固化完全,不考虑固化收缩所产生的应力对翘曲的影响;

(2)为增加计算效率,取原模型的1/4进行建模;(3)层与层之间完全粘结,不会发生相对移动。

3.3 材料属性设置

本次模拟包括铜层和两种不同类型的积层绝缘材料——半固化片,主要由环氧树脂加上玻璃纤维布组成。半固化片被定义为正交各向异性粘弹性材料,铜则被定义为各向同性弹性材料。表1中所示为材料的物性参数,表1中铜的热机械性能在温度变化时无明显变化,半固化片的热机械性能在相应温度范围内取平均值进行计算。如图3所示,本文采用的有限元结构模型主要包括了载板层(2层铜加1层半固化片PP1)、3层无芯基板(3层铜层加2层半固化片PP2)。

表1 材料物性参数

图3 3层无芯基板有限元模型简化结构

3.4 模型的网格划分与分析步骤

本文采用的单元类型是C3D8R,即三维八节点六面体单元。采用以5 mm的全局近似尺寸划分网络,每层被分成2091个单元,15层共31365个单元。由于原模型具有对称性,模拟采用1/4模型建模,图4显示为整体模型在x方向、y方向、z方向上的几何约束。

无芯基板的工艺模拟可以分为5个分析步骤:

第一步,载板层的热压过程,室温下完成堆叠,再将模型升温至180℃;

第二步,载板层从180℃冷却至室温,在室温下完成内层层压结构(一层半固化片与一层铜箔)的叠合,再将整体模型升温至250℃;

第三步,将整体模型从250℃冷却至室温;

第四步,在室温下完成外层层压结构(1层半固化片与1层铜箔)的叠合,再将整体模型从室温升至250℃;

第五步,将整体模型从250℃冷却至室温,在室温下去除载板,得到2块相同的3层无芯基板。

图4 整体结构的约束设置

4 结果与讨论

4.1 模拟结果分析

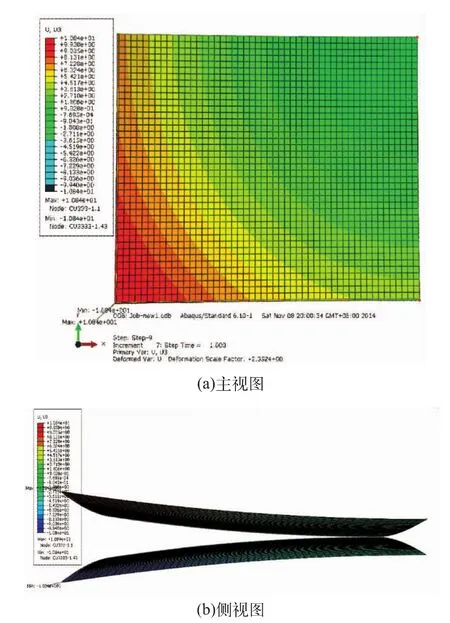

通过模拟发现,模拟结果与分析基本一致,在第五步后,即去除载板后,基板翘曲变形程度最大。在之前步骤中,虽然模型经历了从室温到高温、再从高温到室温的变化过程,但由于在层压过程中模型是上下对称的结构,绝缘层与铜层材料之间CTE不匹配产生的热应力上下相互抵消,使得整体变形很小。在第五步去载板后,整体对称的结构被破坏,无芯基板与载板接触面上的残余热应力释放,从而导致无芯基板发生较大的翘曲变形。表2为模拟中各个分步骤结束后模型的翘曲变形结果与试验相对应过程中记录的翘曲结果,实验中基板尺寸为500 mm×400 mm×296 μm,热循环过程与模拟设置基本一致。图5为第五步后无芯基板在z方向上的位移,即翘曲变形值,其中正负值表示翘曲的方向。根据表2中的结果可以看出,在第一步至第四步,翘曲变形在0.00001 mm量级,而测量值在0 mm,主要原因包括:(1)实验测量基板翘曲采用的是平板测量法,将基板水平放置在平台,采用千分尺测量样品与平台的最大垂直位移,本身的测量精度在0.01 mm,在载板去除前整体结构刚度大,在受热或冷却过程中变形程度小;(2)模拟中基板的整体尺寸为 250 mm×200 mm×296 μm(包括载板),其中 3层无芯基板厚度为71 μm,其在厚度方向上的相对变化在1.7%左右,在可接受的误差范围内(<5%);同时实际实验条件更为复杂,如材料物性参数的变化、翘曲的测量误差等,在实际测量中每个案例都有所不同。

表2 每个分析步骤结束后模型的翘曲变形模拟结果与试验测量结果对比单位/mm

4.2 模拟结果讨论

对无芯基板翘曲变形大小有重要影响的因素包括材料间CTE匹配度、基板的三维尺寸、铜层残铜率等[4]。其中对于CTE匹配度的研究文献较多[5,6],改善翘曲变形的建议是使用CTE相近的绝缘层与铜层材料,可以有效降低无芯基板的翘曲值。本文主要研究各绝缘层、铜层的厚度及铜层残铜率对无芯基板制造工艺过程中翘曲变形大小的影响。

图5 无芯基板在z方向上的变形值

4.2.1 铜层残铜率设计

考虑到电路本身图案过于复杂,如果进行一比一对应建模,建模过程复杂繁琐,同时对网格划分要求高,计算时间长。因上层绝缘层即半固化片材料在压合时会填入到第2层线路的空隙中,造成中间层为Cu与半固化片材料交错的复合材料。这部分材料的属性可以由复合材料的混合法则求出:

其中,E为杨氏模量,v为泊松比,a为热膨胀系数,V表示体积,f、m分别代表铜、半固化片。铜层图案决定了残铜率的大小。模拟中发现残铜率的大小对翘曲变形的大小有重要影响。试验条件下实际铜层残铜率的取值范围为58.48%~87.72%。图6中所示为无芯基板尺寸保持不变的情况下,随着残铜率变化时无芯基板的翘曲变形。结果表明随着残铜率的变化,翘曲变形的结果有先减小后增大的趋势,残铜率过高或者过低都会增大翘曲,因此合理地设计残铜率大小能有效减小翘曲,同时设计中应该尽量保证两侧基板中Cu电路图案的一致性,残铜的分布也对翘曲变形有重要影响。

图6 无芯基板翘曲变形大小随残铜率变化

4.2.2 绝缘层与铜层厚度设计

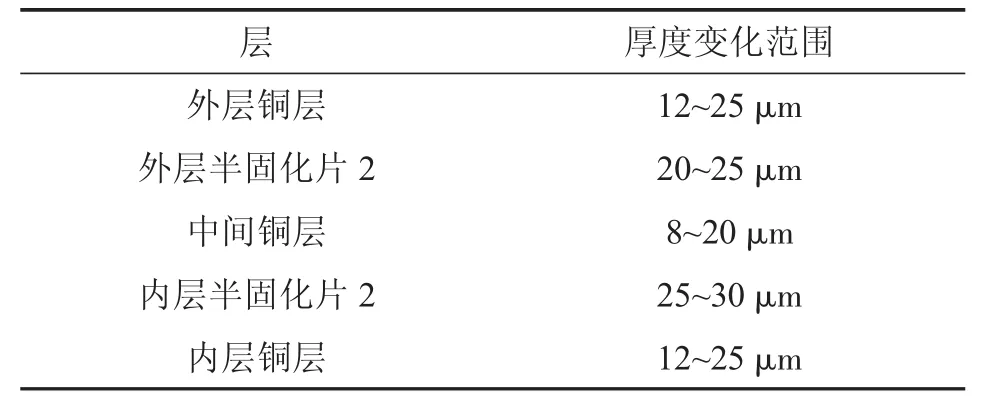

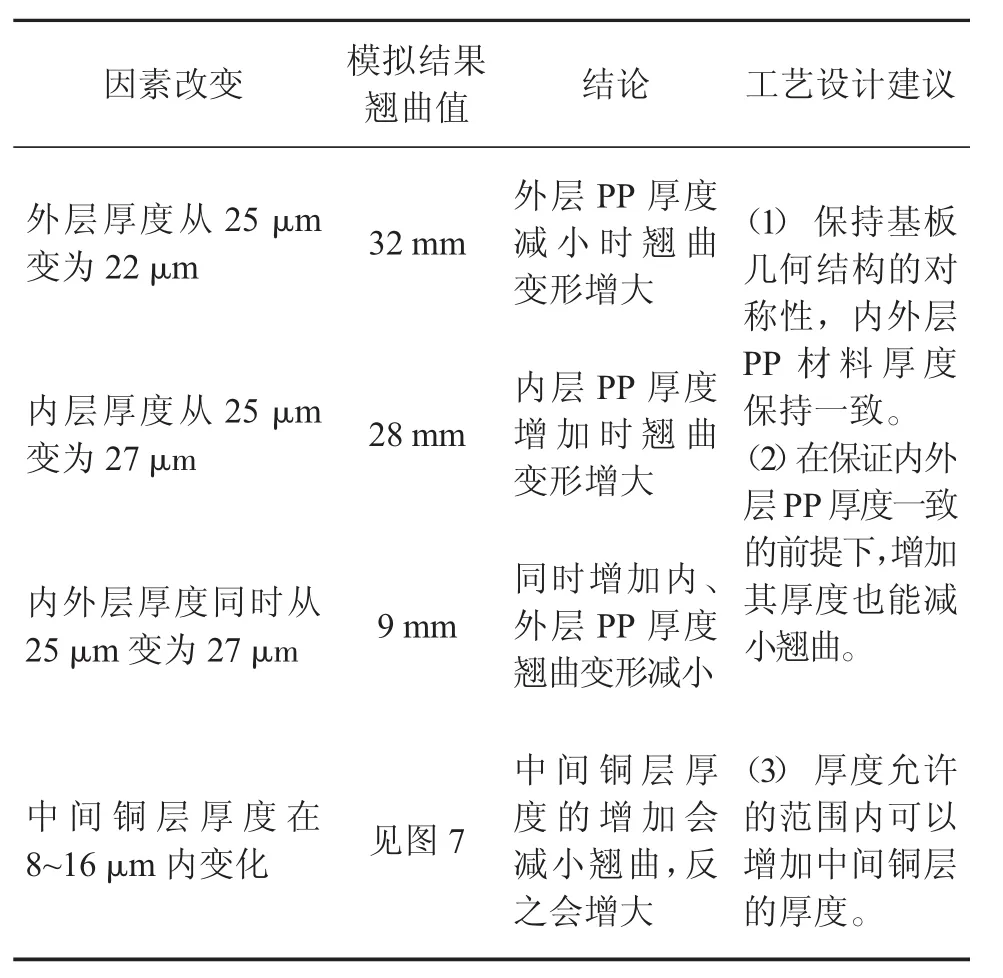

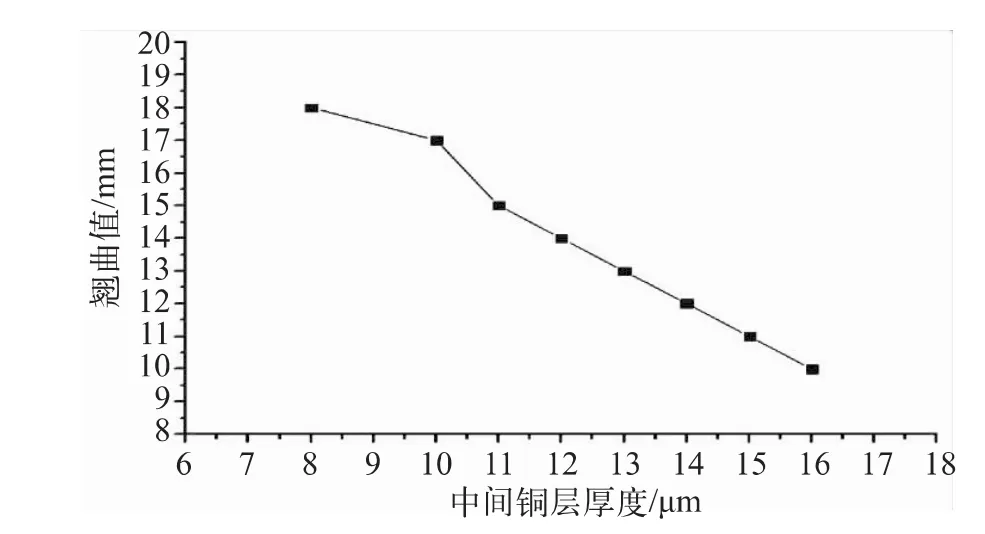

无芯基板中绝缘层与铜层的三维尺寸中,主要是厚度对整个基板翘曲变形的大小有重要影响。表3中所示为各层厚度的变化范围。模拟主要对其中外层、内层半固化片、中间铜层的厚度进行改变,对比各模拟结果,总结如表4所示。

表3 无芯基板各层厚度变化范围

表4 各层厚度变化对翘曲的影响

图7 中间铜层厚度变化与翘曲变形之间的关系

5 总结

本文介绍了一种对称进行的3层无芯基板制造工艺,并对该过程利用有限元软件ABAQUS6.10进行了模拟仿真,模拟计算基板的翘曲变形。文章以无芯基板的三维尺寸与铜层残铜率为研究对象,介绍了对残铜率的模拟方法,通过模拟对比探究这两种因素对翘曲变形大小的影响,并得出以下结论及工艺设计建议:

(1)影响翘曲变形的主要因素包括各层材料CTE不匹配度、无芯基板的三维尺寸和铜层残铜率等;

(2)大小适当的残铜率会有效减小翘曲,过高与过低的残铜率都会增大翘曲值,同时也需要尽量保证两侧铜图案走线一致;

(3)无芯基板的整体厚度增加能够有效抑制翘曲值,但增加厚度的同时不能破坏无芯基板整体结构的几何对称性,对称性的保证是降低翘曲的重要条件。

[1]Shuto T.Next genereation high density build-up package substrate[C].ECWC10,2010.

[2]Cho S,Chang T-E,Lee J Y,et al.New dummy design and stiffener on warpage reduction in Ball Grid Array Printed Circuit Board[J].Microelectronics Reliability,2010,50(2):242-250.

[3]侯朝昭,邵远城,李茂源,等.IC封装无芯基板的发展与制造研究[J].电子工艺技术,2014,(4):187-189.

[4]Raghavan S,Klein K,Yoon S,et al.Methodology to predict substrate warpage and different techniques to achieve substrate warpage targets[J].IEEE Transactions on components,packaging and manufacturing technology,2011,1(7):1064-1074.

[5]Cho S,Cho S,Lee J Y.Estimation of warpage and thermal stress of IVHs in flip-chip ball grid arrays package by FEM[J].Microelectronics Reliability,2008,48(2):300-309.

[6]Kim J,Lee S,Lee J,et al.Warpage issues and assembly challenges using coreless package substrate[C].IPC APEX EXPO,2012.

[7]Kurashina M,Mizutani D,Koide M,et al.Low warpage coreless substrate for large-size LSI packages[C].Electronic Components and Technology Conference(ECTC),2012 IEEE 62nd,2012:1378-1383.

[8]Timoshenko S.Analysis of bi-metal thermostats[J].JOSA,1925,11(3):233-255.

A Manufacturing Process and Warpage Simulation of Three-layers Coreless Substrate

LI Maoyuan1,DIAO Simian2,LIU Jiahuan1,DENG Tianzhengxiong1,LI Yang1

(1.School of Material Science and Engineering Huazhong University of Science and Technology,Wuhan 430074,China;2.Shenzhen Yejiawei Technology Limited Company,Shenzhen 518000,China)

Due to the fact that the thermomechanical properties of the different materials do not match,the warpage during the manufacturing and assembly process is one of the biggest challenges in applying the coreless substrate.In the paper,a manufacturing process of a coreless substrate is introduced.The process is simulated by the finite element software ABAQUS6.10.The influence of different factors on the warpage is analyzed by analyzing the simulation results and the mechanism of warping deformation,and the helpful suggestionhasbeengiventoreduce the warpage.

corelesssubstrate;warpage;ABAQUS

TN405.97

A

1681-1070(2017)12-0009-05

2017-09-16

李茂源(1992—),男,湖北监利人,在读博士,研究方向为电子封装可靠性的有限元模拟、高分子多尺度模拟。