一种改进型盲过采样时钟数据恢复电路

高 宁,桂江华,吴 江

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

一种改进型盲过采样时钟数据恢复电路

高 宁,桂江华,吴 江

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

设计一种改进型盲过采样时钟数据恢复电路。电路主要由并行过采样、滤波整形、鉴相编码和数据选择等模块组成。提出的滤波整形电路可以有效改善采样数据流,让电路拥有更高的抑制噪声和干扰的能力。与鉴相编码电路组合工作,可以使整个时钟数据恢复电路的误码率更低,相位锁定时间更短。

盲过采样;时钟数据恢复;鉴相编码电路

1 引言

许多高速有线数据传输系统中都会用到时钟数据恢复电路,如光通信系统、背板数据链路和芯片到芯片互连。CDR的作用是从接收到的畸变信号中提取传输的串行数据,并恢复相关时钟的定时信息[1]。接收端接收到的串行数据叠加了外界噪声和干扰,接收端在恢复串行信号时,若要正确恢复出数据,必须选择最佳的采样和判决时刻,从而保证最小的误码率。针对这种情况,时钟数据恢复电路必须具备抑制噪声、干扰的能力。

盲过采样时钟数据恢复的技术差别主要体现在数据恢复逻辑的实现方式上。而数据恢复逻辑主要有两种技术:多数判决(Majority Decision Rule)[2~6]和鉴相编码[7~9]。多数判决方式需要消耗一定的数据位用于相位统计,以便选择正确的采样数据作为恢复数据,需要消耗一定的时间用于锁定;鉴相编码方式不同于多数判决,有更大的计算量,数字实现也更加复杂,但是锁定迅速。多数判决方式要求输入数据率与本地采样频率一致才可以保证正确地恢复数据;而鉴相编码方式则允许两者之间存在一定的频率偏差,所以适用范围更广。鉴相编码电路也存在着一些重要问题,如采样数据流里面的不平滑会严重影响数据恢复。

本文对鉴相编码电路进行改进,配合滤波整形电路,让时钟数据电路拥有更好的抑制噪声和干扰的能力。

2 电路设计

如图1所示,盲过采样数据恢复电路主要分为接收器电路和数据恢复电路两个部分。接收器电路采用空间过采样[4]可以减少对本地时钟频率的要求,实现方法基于锁相环(PLL)[1],这里的过采样倍数N选择为5。

图1 盲过采样数据恢复电路结构

时钟数据恢复电路采用改进型的鉴相编码方式实现数据的恢复,同时加入滤波整形电路。

3 主要电路模块

3.1 滤波整形电路

多路平行过采样模块对输入信号Din进行5倍过采样,PLL提供等相差的5个采样时钟采样,产生5位的采样数据流 Bit1、Bit2……Bit5,PBit1、PBit2、……PBit5表示前一采样数据流,LBit1、LBit2、……LBit5表示下一采样数据流。

采样数据流不经过整形直接传入后级进行边沿检测会有很大的问题,一些信号因为噪声和干扰的影响,使得原本的低电平叠加噪声和干扰变成了高电平,有些高电平因为传输的衰减被判决为低电平,所以采样数据流必须经过滤波整形之后再送到后级,才能较好地实现时钟数据恢复。

通过上面的表述也可以看到,采样数据由高电平判决为低电平,低电平误判为高电平之后,往往都与周围至少1个采样数据是相异的,将判决错误的情况做一个统计,这里只考虑5倍过采样的采样数据中有1个数据出现错误的可能性,出现2个误码的可能性极低,这里不作考虑。

按图2所示,将3组采样数据相加,得到HxLx(x为1、2……5),如果当前整形的数据为突变数据,假设为1,那么左右数据都为0,此时HxLx为01,那么Hx即为整形数据应该输出的数据0;如果当前整形数据为突变数据0,那么左右数据都为1,此时HxLx为10,那么Hx仍为整形数据应该输出的数据1。下面的加权判决电路即为一个数据选择模块,将整形后的5 bit采样数据输出到寄存器中。

图2 滤波整形电路实现原理图

通过这个电路对采样数据流的滤波整形,消除了其中的畸变采样数据,使得整个采样数据流变得更加平滑,之后再加上边沿检测电路对整形之后的采样数据流进行跳变沿的检测,并将每位采样数据进行编码,完成对采样数据流的重定时,最终加上数据恢复电路,根据所得编码选择合适的采样时钟作为最佳采样恢复点,进而恢复出有效数据。

3.2 改进型鉴相编码电路

该电路采用鉴相编码的方式来实现时钟数据恢复。

经过滤波整形之后的采样数据流送至鉴相编码电路,如图3所示,采样数据流先进行边沿检测(鉴相),如果采样数据A与采样数据B不同,则将采样数据B标记为1,否则标记为0,这样就完成了边沿检测(鉴相),对每个采样数据进行标记。之后根据对采样数据的标记进行编码,当标记为1时,编码为10000,当标记为0,依次移位,当移位到00001时,如果下一个采样数据标记为1时,编码为10000,如果下一个采样数据依旧标记为0时,则继续移位为10000。在数据选择阶段,选择两个10000编码之间的位置作为最佳采样点,减少错误发生的可能。

最佳采样点都会有一个编号,在理想情况下,应该一直为固定的00100,因为噪声的干扰,在去除噪声的过程中,采样数据流会进行相应的调整,最佳采样点会发生变化;如果输入数据的数据率与CDR采样时钟的频率不一致时,也会导致最佳采样点的变化。这个时候可以对采样点进行统计,记录实际采样点与理想采样点的偏离程度与趋势,对于噪声引起的采样点变化,在整形过程中将去除噪声的位置做标记,在采样点统计时不做统计。

如果采样点规律性偏向01000,则说明输入数据的数据率高于CDR采样时钟的频率,反之,则说明输入数据的数据率不高于CDR采样时钟的频率。

在对采样点做监测时,只有采样位置为00100、01000时,电路才做采样,而采样位置为10000则为异常,不做采样操作。

当输入数据由于频率抖动或者噪声叠加时,从图3中可以看出,在不理想的情况下依旧可以正确地恢复出数据。

图3 鉴相编码

4 仿真结果

本文将采用伪随机序列对盲过采样时钟数据恢复电路进行测试,这里的伪随机序列由线性反馈移位寄存器(LinearFeedbackShiftRegisters,LFSR)结构实现。

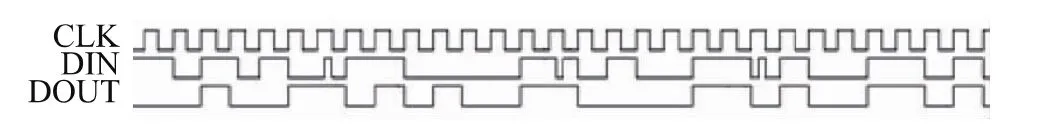

从图4可以看到,在串行输入的数据DIN中存在着一些畸变,这些畸变信号在过采样之后如果不经过处理会严重影响后级的边沿检测(鉴相)。经过设计的电路处理之后可以看到,输出的波形平滑,恢复的数据也完全正确。

经过上述仿真,盲过采样时钟数据恢复电路功能完备,性能可靠,将电路在Altera公司的FPGA内用逻辑分析仪进行验证。经过FPGA验证(见图6),当输入信号的数据率达到100 Mbps时,数据恢复完全正确。

图4 伪随机序列仿真结果

图5 时钟数据恢复仿真

图6 FPGA原型验证结果

5 总结

本文设计的改进型盲过采样时钟数据恢复电路,其鉴相编码电路具备相位偏移监测功能,配合滤波整形电路,使得这样的时钟数据恢复具有更广的适用范围,对于连续字有很高的容忍度,能够很快地锁定并恢复出数据,同时还具有很高的抗噪性能,大大降低数据恢复的误码率(BER),完成突发模式下的数据恢复。

[1]Ming ta Hsieh,Gerald E Sobelman.Architectures for Multi-Gigabit Wire-Linked Clock and Data Recovery[J].IEEE Circuits And Systems Magazine,2008:45-57.

[2]Henning Braunisch,Raj Nair.On the Techniques of Clock Extraction and Oversampling[J].Hot Interconnects 9,2001:139-143.

[3]Jaeha Kim,Deog-Kyoon Jeong.Multi Gigabit Rate Clock and Data Recovery Based on Blind Oversampling[J].IEEE Communications Magazine,2003:68-74.

[4]尹勇生,胡永华,高明伦.过采样技术CDR分析及应用[J].应用科学学报,2006,24(3):240-244.

[5]李嘉洁,陈非凡.基于加权表决的POF信号时钟数据恢复方法[J].光通信技术,2012,14(2):47-50.

[6]韩刚,谭顺乐.BLVDS总线控制系统中CDR及SerDes电路的设计与实现[J].微电机,2012,45(4):67-69.

[7]Sanad Bushnaq,Toru Nakura,Makoto Ikeda.All Digital Baseband 50 Mbps Data Recovery Using 5x Oversampling With 0.9 Data Unit Interval Clock Jitter Tolerance[J].Design and Diagnostics of Electronic Circuits&Systems,2009:206-209.

[8]王宇磊.基于FPGA的光接收机数据恢复电路的设计与实现[D].成都:电子科技大学,2008.

[9]李浩亮.基于USB2.0的高速串行通信接口电路设计技术研究[D].杭州:浙江大学,2005.

[10]谢明璞,武杰,张杰.利用FPGA延时链实现鉴相器时钟数据恢复[J].核技术,2009:477-480.

A Improved Blind Oversampling Clock and Data Recovery Circuit

GAO Ning,GUI Jianghua,WU Jiang

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

This is a improved blind oversampling clock and data recovery circuit.The circuit mainly contains parallel oversampling module,filtering and shaping circuit,phase detector and encoding circuit,data selection module.The filtering and shaping circuit can effectively improve the mutations in the sampling data stream,so that the circuit has a higher abilityto suppress noise and disturbing,combined with phase detector and encoding circuit,the clockanddata recoverycircuitcangeta lower BERandshorter phase-lockingtime.

blindoversampling;clockanddata recovery(CDR);phase detector andencodingcircuit

TN402

A

1681-1070(2017)12-0023-03

2017-08-30

高 宁(1989—),男,江苏无锡人,硕士学历,现在中国电子科技集团公司第五十八研究所从事集成电路开发工作。