基于FPGA仿真模拟技术的智能电能表软件可靠性测试系统设计*

杜蜀薇,赵兵,孔令达,岑炜

(1.国家电网公司,北京100031;2.中国电力科学研究院,北京100192)

0 引 言

随着用电信息采集系统的全面建设,大量智能电能表已投入到现场应用中。截至2016年末,全国范围内已累计安装智能电能表4亿多只,每年新增智能电能表安装数量达6 000万只,智能电能表的安全可靠管理问题一直是电力部门深切关注的问题[1-4]。目前,智能电能表供应商数量已经达到100多个,规模有大有小,设计能力参差不齐,智能电能表投入运行的数量又极其庞大。如此大规模的智能电能表投运后,其运行可靠性对电力企业的经营效益和社会形象影响非常大。

智能电能表现场运行数据表明,依据已有技术标准进行的常规功能性检测虽然在一定程度上确保了智能电能表的供货质量,但无法排除其在典型环境下的潜在软件隐性故障。这些故障一旦发生,就是同一软件批次的所有智能电能表的批量故障,所引发的后果将不堪设想,在给电力公司带来经济损失的同时,也损害了用户的切身利益。因此,亟需深入研究智能电能表软件可靠性测试技术,提高智能电能表软件成熟度和可靠性,减少智能电能表运行故障[5]。

FPGA技术具有使用灵活、高数据处理能力、高运行速度和高可靠性等技术优势,已广泛应用于航空航天[6]、军事[7-8]、通信和交通[9]等领域中。目前,智能电能表主要由MCU、计量单元、存储单元、安全单元等部件组成,大多数功能都是通过嵌入式软件来实现的[10-11]。为了验证智能电能表嵌入式软件的可靠性,设计了一种基于FPGA仿真模拟技术的智能电能表软件测试系统。该系统采用FPGA技术,通过模拟智能电能表各功能芯片的运行工况,通过观察MCU对模拟板的操作实现智能电能表的软件可靠性测试。

1 FPGA在智能电能表软件测试中的技术优势

FPGA是一种新型的半定制逻辑电路,其功能由内部规则排列的逻辑单元阵列(Logic Cell Array)实现。逻辑单元阵列内部主要由可配置逻辑模块(Configurable Logic Block)、输入输出模块(Input Output Block)和内部连接模块(Interconnect Block)3部分组成。FPGA最大的优点在于它具有可重复编程、逻辑功能模块和I/O模块配置比较方便灵活等特性,能够进行系统重构,有效实现用户需要的功能[12]。

FPGA支持不同的编程方式,用户可以根据不同的配置模式,通过存放在片内RAM中的程序来设置工作状态。因此,FPGA应用比较方便灵活,并且与ARM相比,具有较强的数据处理能力和较高的运行速度[13]。

在智能电能表软件测试过程中,需要上位机测试软件通过ARM对智能电能表外围模拟芯片进行信息配置并写入故障。但是,如果ARM在和上位机测试软件进行信息交互的同时,也与被测智能电能表MCU进行信息交互,其处理速度的实时性将会严重降低,甚至引起测试失效。FPGA具有使用灵活、高数据处理能力、高运行速度和高可靠性的技术优势,因此,可采用FPGA的硬件逻辑来实现外围器件的仿真需求,是可行性较高的方案[14]。

2 基于FPGA仿真模拟技术的软件测试系统设计

2.1 测试系统设计

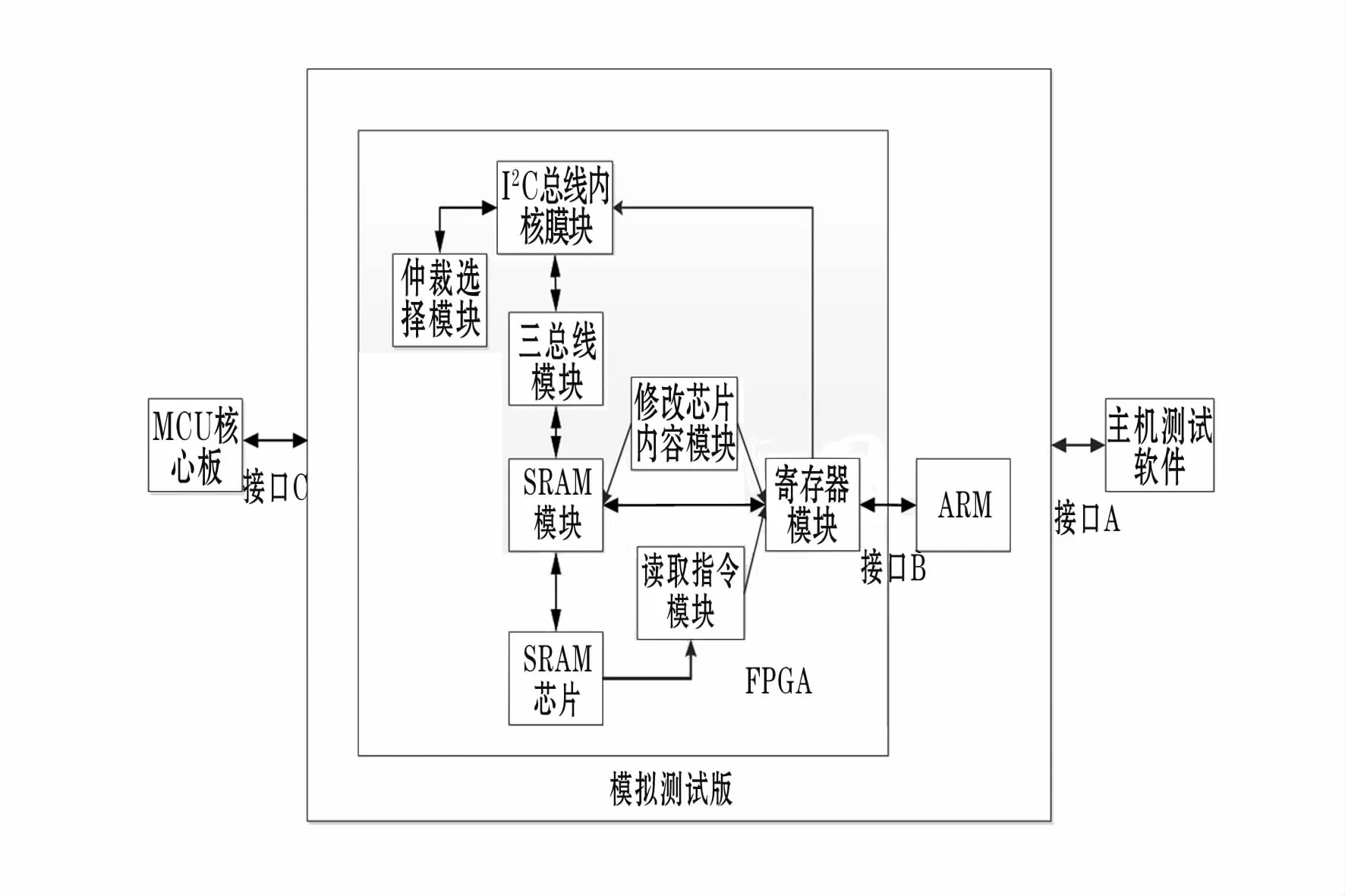

智能电能表软件可靠性测试系统主要由主机测试软件、模拟测试板和MCU核心板组成。智能电能表软件可靠性测试系统逻辑结构如图1所示。

2.2 主机测试软件设计

图1 智能电能表软件可靠性测试系统逻辑结构Fig.1 Logical structure of smartmeter software reliability testing system

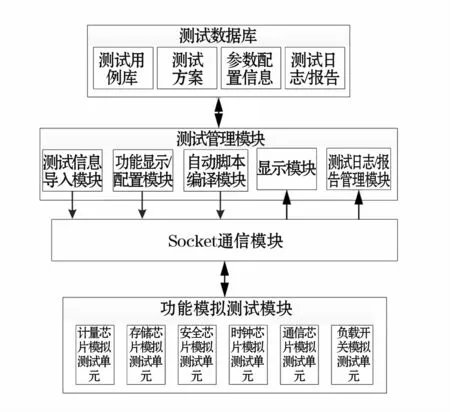

智能电能表软件测试系统主机测试软件在设计时尽量保持各个模块的独立性,在设计模式上采用MVC(Model View Controller,模型-视图-控制器模式)框架,将用户界面与数据层分离,使用控制层连接用户界面和数据层,这样使得系统易于维护,开发效率相对更高。主要包括软件测试数据库、软件测试管理、Socket通信和功能模拟测试等模块,其逻辑架构如图2所示。

图2 上位机测试软件逻辑结构Fig.2 Logical structure of host computer testing software

其中,软件测试数据库主要用于存储测试用例和参数配置信息等。测试管理模块主要包括测试信息导入、功能显示/配置、自动脚本编译、测试状态及结果显示和测试日志/报告管理等模块,主要完成各类测试信息配置、测试脚本编译及管理功能,如芯片的选择、测试方案的选择与配置、各通信接口的选择等。Socket通信模块主要用于完成测试软件与模拟测试板的通信。功能模拟测试模块主要根据实际测试需求,通过FPGA模拟各类型芯片功能,完成实际软件测试[15]。

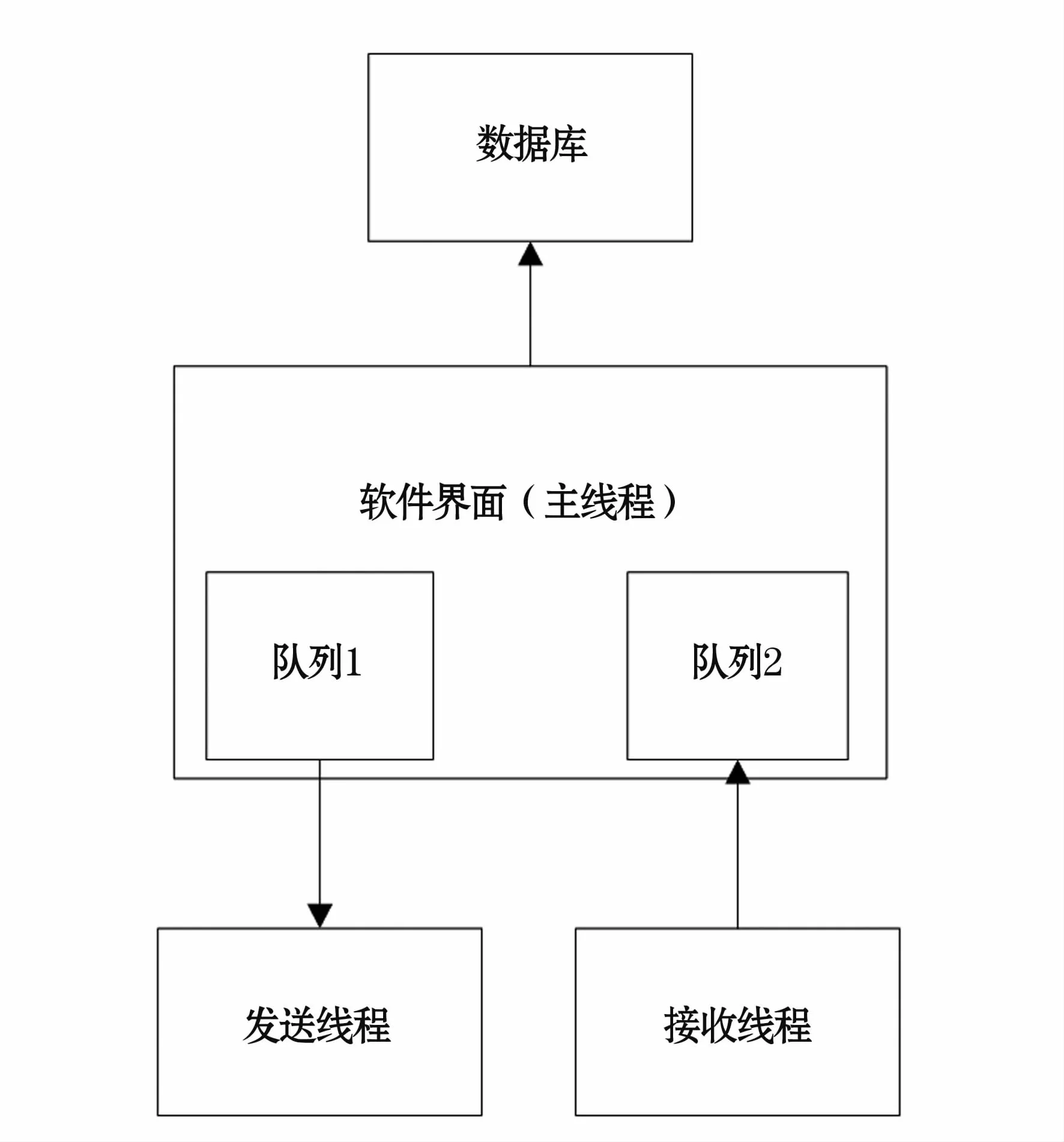

以Socket通信模块为例,智能电能表软件测试系统主机测试软件通信过程设计思路如下:

在测试软件架构中,界面操作是主线程,通过功能按钮触发数据管理线程,数据管理线程判断应与哪个端口进行通信,收发的是哪种类型的数据。建立收/发两个线程,与各个测试板建立连接(循环),将建立连接的通信套接字的服务器端IP端口保存到通信列表里,之后所有向服务器端发送的Socket信息都从这个列表中取出发送,如图3所示。

图3 Socket通信模块工作原理Fig.3 Working principle of socket communication module

在多线程通信过程中,主线程建立消息管理队列实现线程管理,与数据库连接实现数据的存取和数据分页显示。界面设计运用C#中的winforms控件完成,界面主题采用页签(tabpage)的形式来展示不同的测试模块,分别为:总体配置页、计量芯片单元、存储芯片单元、时钟芯片单元、安全芯片单元、红外/485单元、负载开关单元、电流电压检测单元、通信连接页。

2.3 MCU核心板设计

MCU核心板和模拟测试板是智能电能表软件可靠性测试系统的核心器件。MCU核心板相当于被测对象,由被测试厂家按照规范要求加工制作并注入实际运行的智能电能表程序。

2.4 模拟测试板设计

模拟测试板包括模拟监控板ARM和芯片模拟板FPGA,使用可编程语言分别模拟仿真计量芯片、存储芯片、时钟芯片等,实现智能电能表的软件测试。模拟仿真过程采用双端口方式,其中一个端口模拟实现芯片的原有功能,另一个端口将芯片的状态信息和响应信息实时传送给控制单元进行软件测试与分析。接口A是主机测试软件和模拟测试板之间的接口,采用以太网接口,模拟测试板为服务端;接口B是模拟测试板内部模拟监控板ARM与芯片模拟板FPGA之间的接口;接口C是模拟测试板与MCU核心板之间的接口[16-17]。

芯片模拟板FPGA主要包括I2C总线内核、仲裁选择、三总线、SRAM存储控制、SRAM芯片、修改芯片内容、读取操作指令和寄存器等功能模块。仲裁选择模块与I2C总线内核、三总线模块、SRAM存储控制模块和SRAM芯片依次进行信息交互;修改芯片内容模块分别与SRAM存储控制模块和寄存器模块连接;读取操作指令模块分别与SRAM芯片和寄存器模块连接,并与SRAM存储控制模块和寄存器模块进行信息交互。

3 测试系统功能实现

3.1 系统实现原理

在软件测试过程中,模拟监控板ARM通过接口A接收主机测试软件发送的指令,同时通过接口B与测试模拟板FPGA进行信息交换,完成测试软件要求的操作。MCU核心板通过接口C对芯片模拟板FPGA进行信息交互,模拟智能电能表对芯片的功能操作。智能电能表软件测试系统工作原理如下:

(1)模拟电能表对EEPROM的读写操作

通过I2C总线内核接收MCU核心板发送的串行时钟信号、串行数据信号及写保护信号,I2C总线内核根据I2C协议将接收的数据信号解析为通信地址、传输数据及读写控制信号;仲裁选择模块接收I2C总线内核发送的请求信号,进行片选,使对应的I2C总线内核将通信地址、传输数据及读写控制信号发送至三总线模块;三总线模块通过SRAM存储控制模块实现对SRAM的读写操作。

(2)读取操作指令

读取操作指令模块由操作指令控制子模块和操作指令FIFO(First Input First Output,先入先出)子模块两部分组成,操作指令控制子模块读取SRAM存储器控制模块内的数据、地址、读写控制等信息,并按照一定的协议组合成一条完整的操作指令,发送至操作指令FIFO子模块。由于FIFO满足先入先出的排序方式,因此操作指令可按执行操作的先后顺序存入操作指令FIFO子模块。当寄存器模块接收到模拟监控板ARM发送的读取操作指令信号后,读取相应的操作指令,再发送至模拟监控板ARM,实现读取操作指令功能。

(3)芯片故障模拟

芯片故障模拟的主要思路是通过改变芯片内特定地址的数据来模拟现场复杂工况引发的现象。测试系统通过ARM发送修改芯片内容指令至寄存器模块,寄存器模块按协议解析接收的指令,将数据、地址、写控制等信息经过修改芯片内容模块发送至三总线模块,再通过SRAM存储控制模块将修改的数据写入对应的地址。在执行芯片故障写入过程中,需屏蔽由I2C内核写入该地址的功能,以免ARM修改的数据被MCU核心板写入的数据覆盖。同时,ARM可通过寄存器模块将数据、地址、读控制信息发送至三总线模块,经过SRAM存储控制模块读取SRAM对应地址的数据,以检验故障是否成功写入。

(4)芯片信息配置

寄存器模块按协议对ARM发送的配置芯片信息指令进行解析,再发送至I2C内核中,然后由I2C配置芯片数量,修改芯片地址位数并配置芯片的存储容量。

3.2 系统测试流程

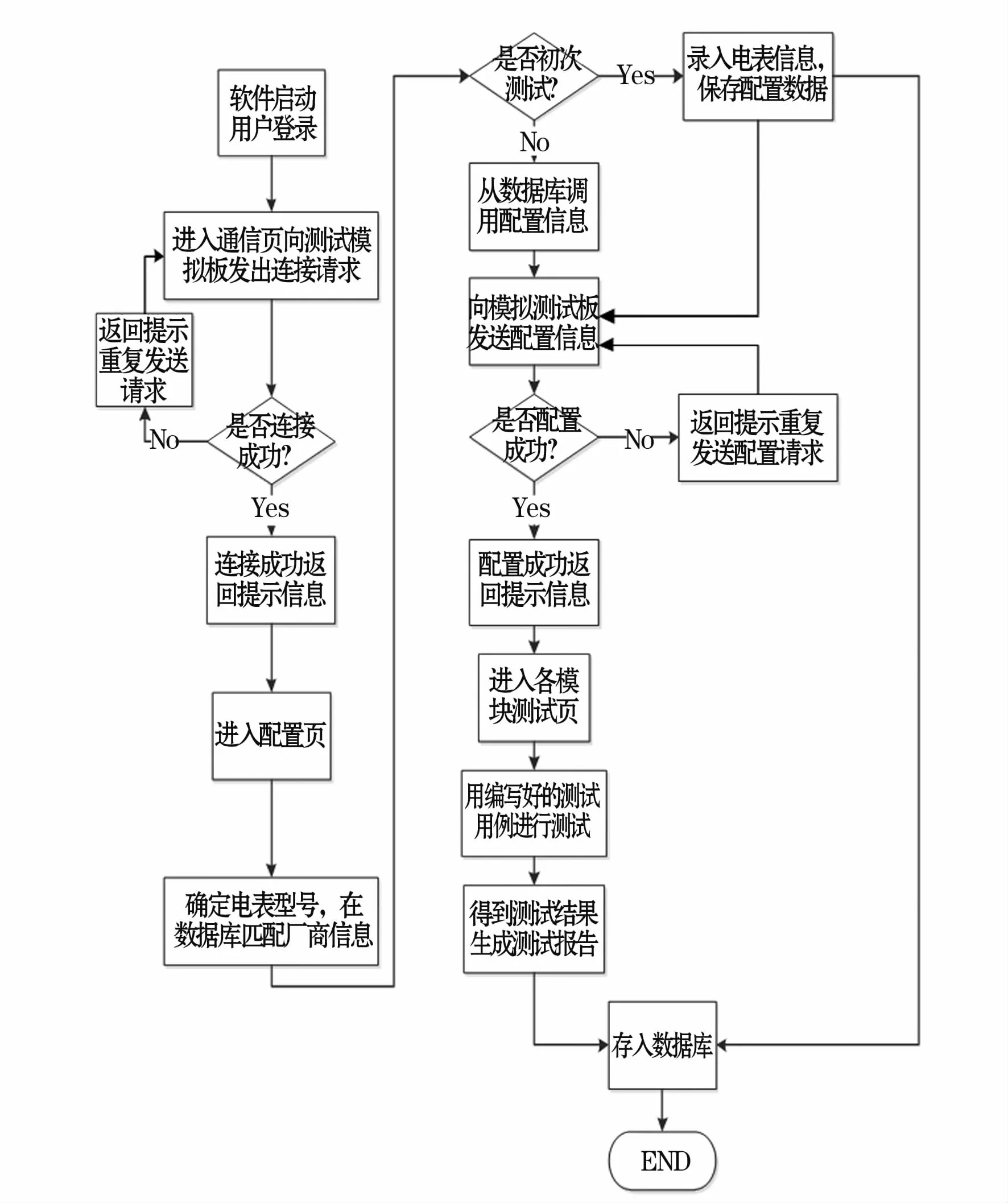

在智能电能表软件可靠性测试过程中,首先要对被测的智能电能表嵌入式系统进行信息配置,由于不同的电能表厂家、同厂家不同型号的电能表都有不同的测试需求,因此需要有个性化的测试策略来配合。主机测试软件作为服务端通过以太网将配置信息下发到模拟测试板,模拟测试板收到信息并配置成功后开始软件测试。软件测试过程如图4所示。

智能电能表软件可靠性测试过程描述如下:

(1)启动测试软件,用户登陆测试系统;

(2)主机测试软件向模拟测试板发送通信连接请求,若连接成功,系统进入配置页面,若失败,重新发起连接请求;

(3)检测人员确定送检样表型号,在数据库中匹配厂商信息(若是初次测试,录入电能表信息,将配置信息保存至数据库中;若不是初次测试,直接调用数据库中的电能表配置信息);

(4)向模拟测试板发送配置信息,模拟测试板判断是否配置成功,若成功,返回“配置成功”提示信息,若失败,返回“重新发送配置信息”提示;

(5)信息配置成功后,进入各功能模块测试页面,用编写好的测试用例进行软件测试;

(6)测试完成后,生成测试报告并将相关信息存入系统数据库中。

图4 软件测试流程Fig.4 Software testing process

4 测试系统性能验证

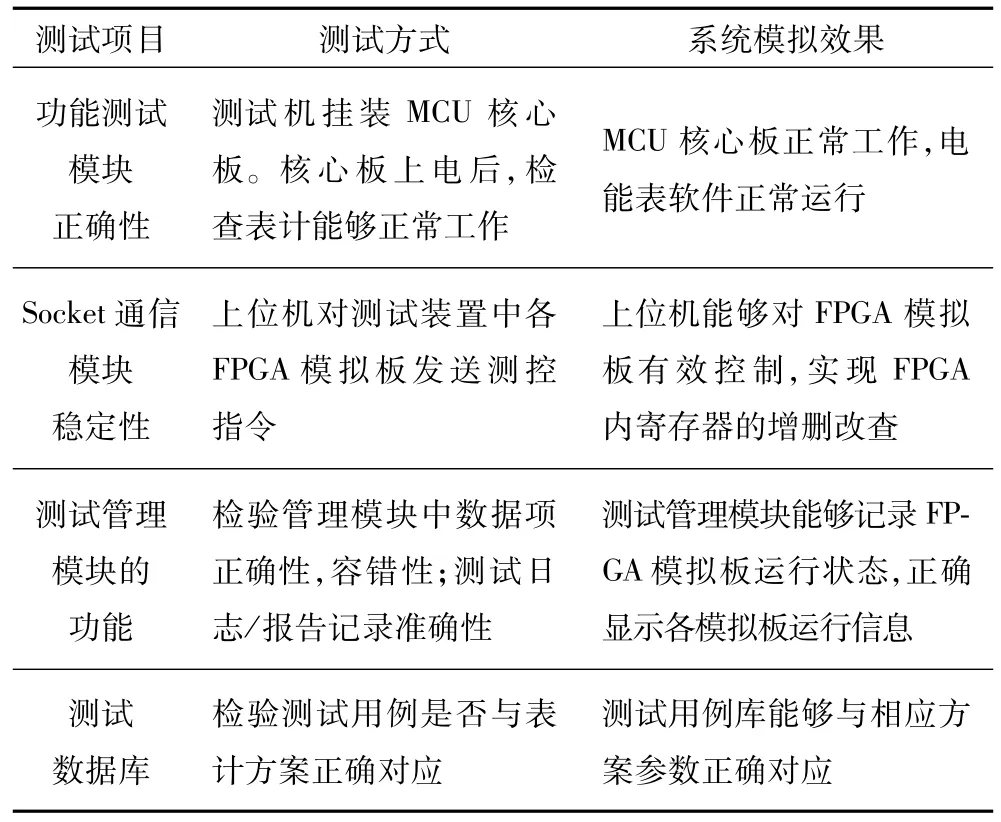

为了验证智能电能表软件测试系统的性能,分别选择24家智能电能表生产厂商的26块单、三相智能电能表分别开展测试系统性能验证试验和智能电能表软件可靠性验证试验。其中,测试系统核心功能测试结果如表1所示。

表1 测试系统验证试验结果Tab.1 Test result of software reliability testing system

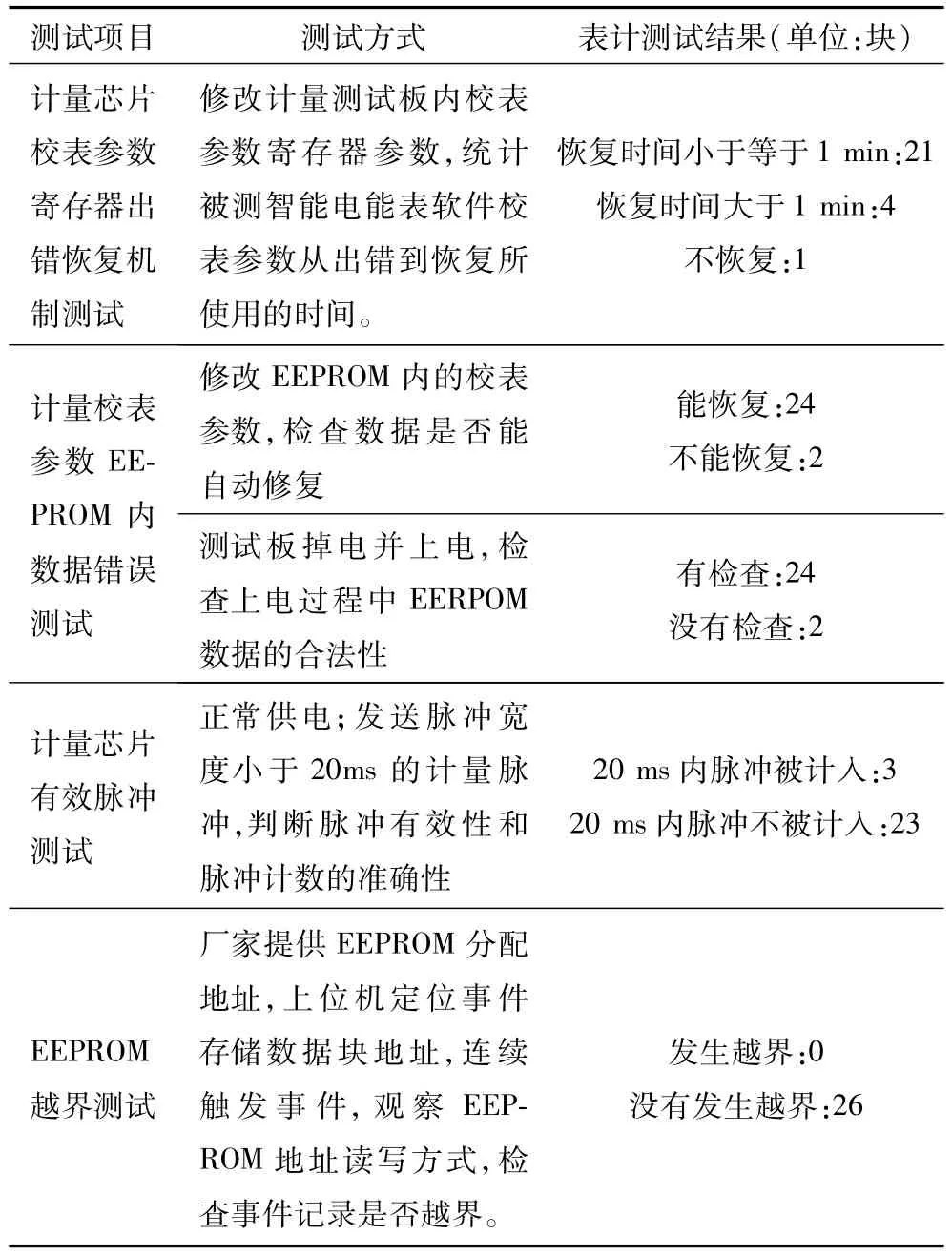

选用计量参数出错恢复机制测试、计量校表参数EEPROM内数据错误测试、计量芯片有效脉冲测试、扣费机制测试、时钟同步测试、EEPROM越界测试等测试用例进行了10次软件可靠性测试。测试结果如表2所示。

表2 智能电能表软件测试结果Tab.2 Test result of smartmeter software

通过测试结果分析,基于FPGA仿真模拟技术的智能电能表测试系统可测试出不同厂家的智能电能表在极限情况下出现的如电能表参数错误未修复;修复时间过长;少计量或计量偏差、掉电脉冲尾数丢失、事件记录EEPROM越界等深度软件可靠性问题。

这些问题在常规测试中,缺陷是触发不出来的。若这些缺陷未测出,在现场几年或更长时间的运行过程中,可能出现因异常事故的发生或现场各种环境的干扰导致智能电能表软件运行故障发生,这些故障将会给智能电能表正常计量、结算或运行带来隐患,产生电费纠纷等事件。

5 结束语

为了有效验证智能电能表的软件可靠性,防止大批量智能电能表故障发生,文章首先分析了FPGA技术在智能电能表软件测试中的应用需求,从软、硬件两方面设计了一种基于FPGA仿真模拟技术的智能电能表软件可靠性测试系统。在该测试系统中应用FPGA模拟各类型芯片,实现了智能电能表软件的快速准确可靠性测试。之后,选取不同的测试样本对基于FPGA仿真模拟技术的智能电能表软件可靠性测试系统进行了性能验证。验证结果表明:基于FPGA仿真模拟技术的智能电能表测试系统可测试出不同厂家的智能电能表在极限情况下存在电能表参数错误未修复或修复时间过长、少计量或计量不准确、掉电脉冲尾数丢失、事件记录EEPROM越界等深度软件可靠性问题,有效提高了智能电能表软件的成熟度和可靠性,减少了其批量运行故障隐患。