高频薄膜微电感建模与耦合度分析

,

(福州大学电气工程与自动化学院,福建 福州 350116)

高频薄膜微电感建模与耦合度分析

陈义祥,董纪清

(福州大学电气工程与自动化学院,福建 福州 350116)

分析高频下薄膜微电感磁路磁阻的非线性,根据磁通分布情况建立了两相耦合跑道型薄膜微电感的磁路模型,结合磁路模型研究了跑道型薄膜微电感的磁芯中柱气隙大小、磁芯分层情况、工作频率大小、两相绕组间距大小以及边柱气隙大小对耦合度的影响,并运用Maxwell软件的仿真结果验证了理论分析的准确性。

跑道型薄膜微电感;磁路模型;耦合系数

1 引言

当前CPU处理器的工作频率越来越高,工作电流越来越大,如果为CPU供电的电压调节模块(VRM)不是很靠近负载,从VRM输出端口到CPU的引线上将存在较大的寄生参数,在高频下会严重造成供电质量下降。为了减小引线上的寄生参数对供电质量的影响,人们试图在微处理器集成电路上直接供电,实现供电电源芯片化[1]。其中电感是制约供电电源芯片化的主要原因,而如今薄膜微电感技术是实现片上供电的突破点[2],所以对薄膜微电感技术的研究具有重大意义。

薄膜微电感的出现为电感器的小型化、高频化开辟了有效的途径,显示出强大的生命力。薄膜微电感采用反耦合方案运用于多相交错VRM中,可以通过改变其耦合度调节支路电流纹波大小和响应速度[3],成为协调VRM动态和稳态性能的重要手段。因此对多相薄膜微电感耦合度的影响因素进行相应的研究分析具有重要意义。但目前国内外上对于薄膜微电感的研究主要集中于磁芯材料的制备,结构参数的优化,高频下感量的提升等方面,而并未系统地对多相薄膜微电感的耦合度进行分析。所以本文建立了两相耦合跑道型薄膜微电感的磁路模型,结合磁路模型研究了跑道型薄膜微电感的结构参数设计和某些特定工作情况对于耦合度的影响,且运用Maxwell软件的仿真数据验证了分析结果的正确性。

2 磁阻分析与磁路模型建立

在多种结构的薄膜微电感中,跑道型薄膜微电感由于能够很好地利用磁膜的各向异性,即减小磁芯在高频下的磁滞损耗,又有助于改善电感的饱和特性,具有很好的研究前景[4-6]。因此本章节分析了其在高频下磁路磁阻的非线性,然后根据高频下的磁场分布情况建立了磁路模型。跑道型薄膜微电感具有结构上的对称性,其左半部分的尺寸标注如图1所示。

图1 跑道型薄膜微电感尺寸标注

2.1 高频下磁路磁阻的分析

(1)

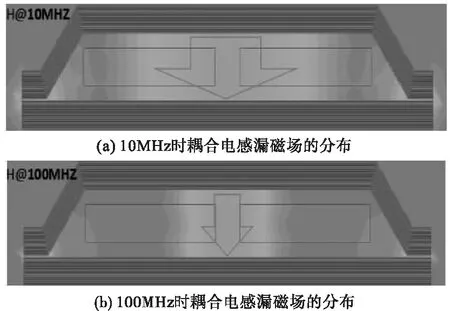

图2 不同频率下耦合电感漏磁场的分布

耦合电感漏磁通的磁路磁阻也受激励的频率大小影响[7]。高频下绕组中感生出涡流,对外部的磁场有去磁作用。如图2(a)所示,在10MHz时,绕组涡流相对小,使得漏磁通可以穿透过绕组的面积较大,相当于穿透过绕组的漏磁通的磁路面积较大,从而此部分的磁路磁阻较小。相反地,如图2(b)所示,在100MHz时,绕组涡流大,使得漏磁通可以穿透过绕组的面积变小,漏磁通的磁路面积减小,从而此部分的磁路磁阻上升。特别当频率大到一定值时,漏磁通不再穿透过绕组,可以认为耦合电感的漏磁通磁路宽度仅为两绕组之间的间距W2。所以漏磁通的磁路磁阻在频域上也显示出非线性。

2.2 跑道型耦合薄膜微电感磁路模型的建立

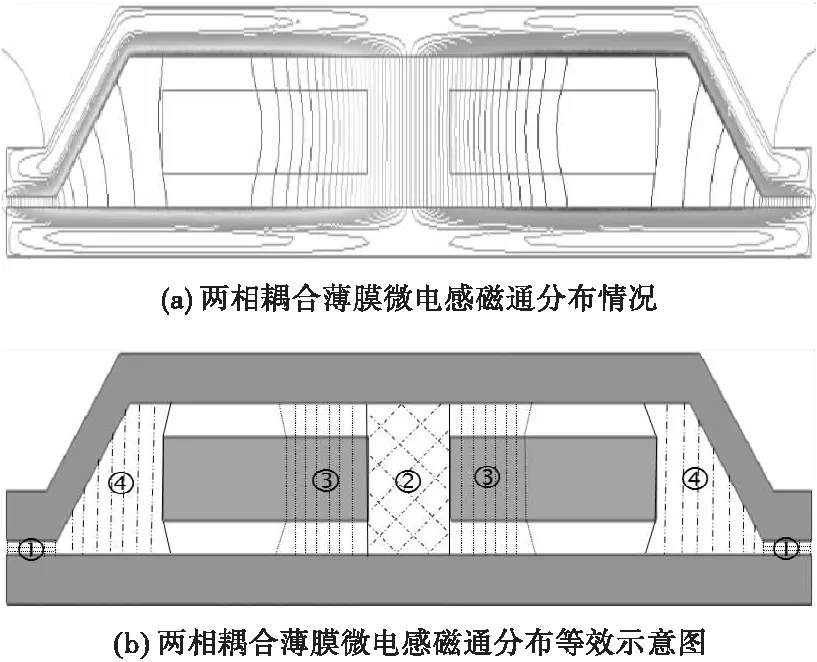

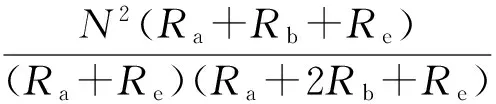

对于两路绕组匝数均为1的跑道型耦合薄膜微电感,当两路绕组通以反向电流时,通过有限元仿真得其磁通分布情况,如图3(a)所示。分析此情况下的磁通分布,可忽略磁芯外部扩散磁通。如图3(b)所示为两路耦合薄膜微电感磁通分布等效示意图,除磁芯内部的主磁通外,部分磁通经区域④形成内部旁路漏磁通,区域①为跑道型薄膜微电感边柱磁芯的气隙,其分布有电感的主磁通;区域②为磁芯中柱气隙,其与区域③一起分布有耦合电感漏磁通。

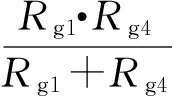

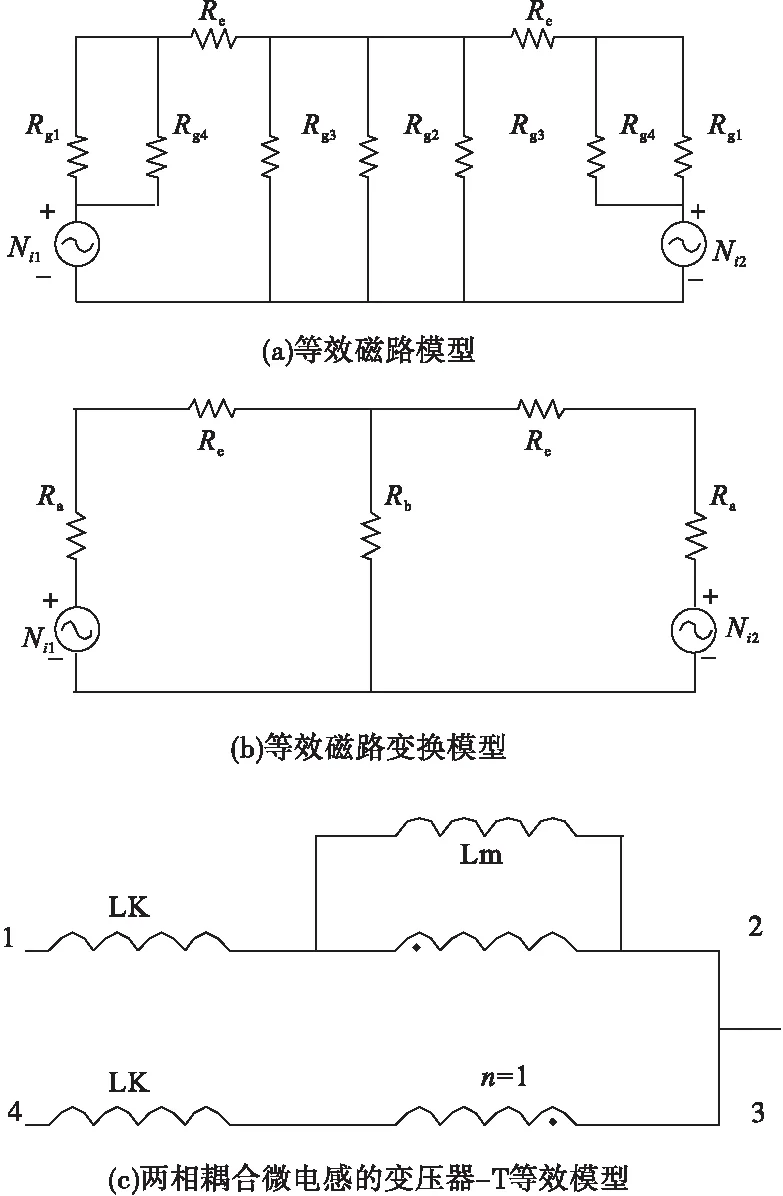

根据图3(b)和薄膜电感结构的对称性,可以列出图4(a)所示的9磁阻等效磁路。其中Re为等效磁芯磁阻;Rg1为区域①的磁芯边柱气隙磁阻;Rg2为区域②漏磁通通过两绕组间距的气隙磁阻,其大小可用式子(2)估算;Rg3为区域③漏磁通穿透过绕组的磁路磁阻;Rg4为区域④旁路漏磁通的磁阻。为了使后续推导具有通用性,假设两路耦合电感的绕组匝数均为N,绕组上的电流分别为i1和i2,形成的磁动势分别为Ni1和Ni2。

(2)

图3 两相耦合薄膜微电感磁通分布情况

由于图4(a)中磁路包含9个磁阻,结构复杂而不利于后续的分析。为了分析简便,对4(a)的磁路进行阻抗等效变换,从而得到图4(b)中的等效磁路变换模型,其中Ra和Rb分别由式子(3)和式子(4)表示。

(3)

(4)

如图4(c)所示,根据磁路-电路对偶变换法可得两路耦合薄膜微电感的变压器-T等效模型[8],则由图4(b)的等效变换磁路可得自感L、激磁电感Lm、漏感Lk以及耦合系数k与磁路磁阻之间的关系式为:

(5)

(6)

(7)

(8)

根据以上推导出来的公式,可分析各个磁阻的变化对自感L、激磁电感Lm、漏感Lk以及耦合系数k的影响,从理论上指导跑道型耦合薄膜微电感尺寸规格的设计和分析。

图4 两相耦合微电感磁路模型

3 耦合系数的影响因素分析

跑道型薄膜微电感耦合度的影响因素主要有中柱气隙的大小、磁芯分层的情况、工作频率的大小、两相绕组间的间距大小以及边柱气隙的大小。本章节运用所建立的磁路模型从理论上对这些影响因素进行分析。

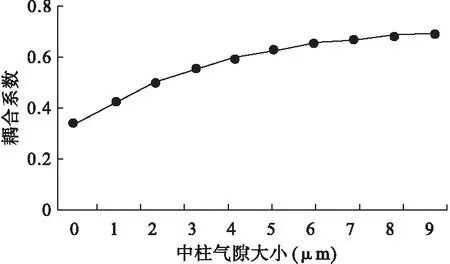

(1)薄膜电感中柱气隙大小对耦合系数的影响。如图5所示,在电感其他结构尺寸不变的情况下改变磁芯中柱的气隙h2的大小。当h2变大,由式(2)、(4)与(8)可得Rg2变大,Rb也随之变大,漏磁通磁路磁阻增大,所以耦合系数k将变大。

图5 两相耦合跑道型薄膜微电感截面图

(3)工作频率对耦合系数的影响。磁芯分层使得每层磁芯厚度小于趋肤深度后,尽管激励的频率上升,磁芯的涡流增加不明显,但绕组的涡流依旧是增加的,对于漏磁通有去磁作用。如图2、图3所示,频率上升使得漏磁通穿透过的区域③的面积变小,Rg3增大,由式(4)与式(8)可知耦合系数k将会有所上升。

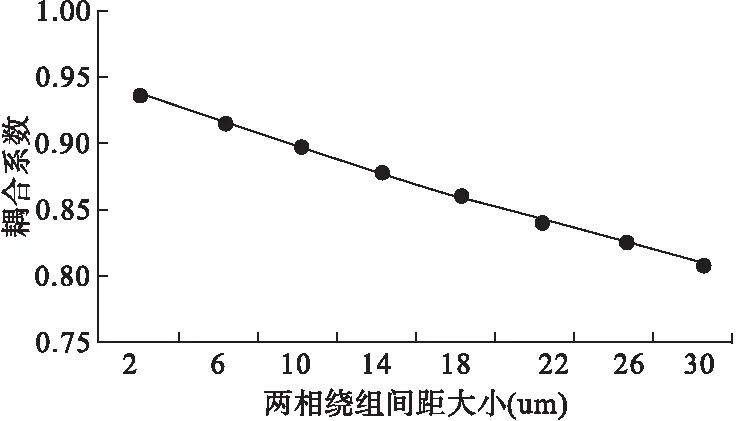

(4)两相绕组的间距大小对耦合系数的影响。如图1所示,W2为两绕组间距的大小,通过调节W2的大小可以调节跑道型耦合薄膜微电感的耦合系数。由式(2)可知,随着W2的增大,Rg2会变小。根据模型中的式(4)与式(8)可知耦合系数会随着W2的增大而下降。

(5)边柱气隙大小对耦合系数的影响。如图3所示,区域①为边柱的气隙,其所对应的磁阻为Rg1,Rg1随着气隙高度h1的增大而增大。根据磁路模型推导出来的式(3)与式(8)得耦合系数会随着Rg1的增大而下降。

4 仿真验证

本章节运用Maxwell仿真软件对上章节的理论分析进行验证。其中仿真模型的磁芯为Ni80Fe20,其相对磁导率为1000,电阻率为20uΩ*cm;两相绕组在保证磁芯不饱和的前提下加激励,且两相激励的幅值相同方向相反。

4.1 中柱气隙对耦合系数的影响

在Maxwell中建立图5中的模型,所加激励频率为100MHz,只改变磁芯中柱的气隙h2的大小进行相应的仿真,得出图6的结果,耦合系数随中柱气隙的变大而变大,可以看出上章节中的理论分析与仿真结果相吻合。因此得出结论:通过调节磁芯中柱的气隙h2的大小可以调节耦合系数k的大小,且耦合系数k随着中柱气隙h2的增大而上升。

图6 耦合系数随中柱气隙的变化情况

4.2 高频下磁芯分层对耦合系数的影响

在仿真模型中,保持磁芯总厚度为3μm的前提下对磁芯进行分层,且磁芯层之间的介质层厚度固定为5nm,激励频率为100MHz,仿真后的数据结果如图7所示。

图7 耦合系数随磁芯分层层数的变化情况

4.3 工作频率对耦合系数的影响

磁芯合理分层,且在不改变仿真模型尺寸参数的情况下,改变所加激励的频率,Maxwell仿真出来的不同频率下的耦合系数如图8所示:耦合系数随着频率的增大而升高,其变化趋势与上章节的理论分析结果相吻合,证明了理论分析的正确性。

图8 耦合系数与激励频率的关系

4.4 两相绕组间距对耦合系数的影响

图9为激励频率100MHz下,只改变两相绕组的间距大小得到的薄膜微电感耦合系数。从图9得耦合系数随着两绕组间距的增大而下降,此趋势证明了理论分析是正确的。可得结论:在其他参数不变的情况下,可通过改变两相绕组之间的间距来调节耦合系数,且耦合系数随着间距的增大而下降。

图9 耦合系数与两相绕组间距的关系

4.5 边柱气隙对耦合系数的影响

在仿真模型中只改变边柱气隙的大小,得到的仿真结果如图10所示,耦合系数随着边柱气隙的增大而下降。此变化趋势与磁路模型的理论分析相一致,证明了理论分析结果。

图10 耦合系数与边柱气隙的关系

5 结论

薄膜微电感采用反耦合方案运用于多相交错并联VRM中,能提高VRM的稳态性能和动态响应性能,并为片上供电技术的实现提供了可能。本文分析了磁路磁阻在频域上的非线性,并通过建立两相耦合跑道型薄膜微电感的磁路模型来分析耦合度的影响因素。跑道型薄膜微电感耦合度的影响因数主要有中柱气隙的大小、磁芯分层情况、工作频率大小、两相绕组间距的大小以及边柱气隙的大小。且运用Maxwell仿真软件验证了分析结果的准确性。

[1] G.Schrom,G.P.Hazucha,J.-H.Hahn,V.Kursun,D.Gardner,S.Narendra,T.Karnik,and T.V.De,“Feasibility of monolithic and 3D-stacked DC-DC converters for microprocessors in 90 nm technology generation,” in Proc.2004 Int.Symp.Low Power Electronics and Design,2004,pp.263-268.

[2] Patrick R.Morrow,Chang-Min Park,Henry W.Koertzen,and J.Ted DiBene,Design and Fabrication of On-Chip Coupled Inductors Integrated With Magnetic Material for Voltage Regulators[J].IEEE Transactions on Magnetics,2012,48(11):1678-1686.

[3] 韩占岭,杨玉岗,冯本成.无气隙可变耦合度的耦合电感研究[J].电源学报,2011,47(6):77-80.

[4] N.Wang,T.O′Donnell,S.Roy,M.Brunet,P.McCloskey,and S.C.O′Mathuna,High frequency micromachined power inductors[J].J.Magn.Magn.Mater,2005(290):1347-1350.

[5] R.Meere,T.O′Donnell,N.Wang,S.Kulkarni,and C.O′Mathuna,Size and performance trade-off in micro-inductors for high frequency dc-dc conver-sion[J].IEEE Trans.Magn,2009,45(10):4243-4237.

[6] N.Wang,T.O′Donnell,S.Roy,P.McCloskey,and C.O′Mathuna,Micro-inductors integrated on silicon for power supply on chip[J].J.Magn.Magn.Mater,2007,316(2):e233-e237.

[7] Adel Elsherbini,Henning Braunisch,Kevin O′Brien,and Michael J.Hill,Circuit Modeling of Nonlinear Lossy Frequency-Dependent Thin-Film Magnetic Inductors[J].IEEE Transactions on Magnetics,2014,4(1):145-152.

[8] 王凯.磁耦合技术对电压调节模块(VRM)性能改善的分析与应用[D].福州:福州大学,2008:22-23.

ModelandCouplingDegreeAnalysisforHigh-frequencyThin-filmMicroinductors

CHENYi-xiang,DONGJi-qing

(College of Electrical Engineering and Automation of Fuzhou University,Fuzhou,350116,China)

Nonlinear frequency-dependent magnetic resistances for thin-film microinductors are analyzed in the paper.The magnetic circuit model for two-phase coupled racetrack-shaped thin-film microinductors is designed on the basis of distribution of magnetic flux.According to the magnetic circuit model,this paper analyses the effects of air gap of magnetic core middle column,magnetic core lamination,working frequency,the distance between the two phase windings and air gap of magnetic core side column for coupling degree.Then the effects for coupling degree is simulated by Maxwell software.The theoretical analysis results based on magnetic circuit model are well consistent with the simulation.

racetrack-shaped thin-film microinductor;magnetic circuit model;coupling coefficient

1004-289X(2017)03-0047-05

TM15

B

2016-03-29

陈义祥(1991-),男,福建省泉州市人,硕士研究生,主要从事电力电子高频磁技术的研究。