高脉冲密度雷达信号处理系统设计*

王鸿超,耿常青,王 龙,童文锋

(1.中国人民解放军空军航空大学 信息对抗系,吉林 长春 130022; 2.中国人民解放军94691部队,福建 龙岩 366200)

高脉冲密度雷达信号处理系统设计*

王鸿超1,耿常青1,王 龙1,童文锋2

(1.中国人民解放军空军航空大学 信息对抗系,吉林 长春130022;2.中国人民解放军94691部队,福建 龙岩366200)

随着雷达系统的不断升级,电磁空间当中的信号密度也在不断增加。为了不断适应电磁环境,满足对高脉冲密度雷达信号处理的要求,设计了一套基于TITMS320C6678芯片和Xilinx的XC7VX485T芯片的多DSP+FPGA架构的信号处理系统。本系统的核心在于设计实现了较为合理的数据预处理流程,并通过具体的硬件电路实现。该信号处理板是一种符合VPX标准,可工作于机载、车载或其他恶劣条件下的特种设备,通过预处理设计,有效提高了系统的处理能力。

高脉冲密度;预处理;现场可编程门阵列;到达角

0 引言

随着雷达系统的不断升级,对信号处理系统的运算处理速度、数据带宽和传输速率等要求也不断提高[1-2]。已有的信号处理系统由多个功能模块组合而成,集成度普遍不高,而且数据处理能力相对较弱,设备体积庞大,不能够满足现代信号处理的需求。而基于VPX标准的信号处理平台能够集高密度计算与高速数据传输于一体,实现强大的信号处理及数据交换能力[3],同时明显缩小了设备体积,能够满足特种设备需求。

针对此,本文结合某信号处理系统科研项目,设计了符合VPX标准的信号处理系统。本系统以多核DSP芯片TMS320C6678为核心处理器,利用多核DSP与FPGA构建的串行高速数据接口(Serial Rapid Input/Output, SRIO)完成大数据量交换。在DSP芯片内完成信号处理后将计算结果经由SRIO与PCIE (Periph-eral Component Interconnect Express)转换模块直接上传到上位机,在上位机端进行结果的实时显示。上位机端通过PCIE监控各模块运行状态,进行健康管理以及计算资源动态调整。本系统是一个通用的数字信号处理平台,系统集成度高,运算能力强,结构灵活。其中,预处理模块和控制模块的设计,进一步提升了系统的处理能力。

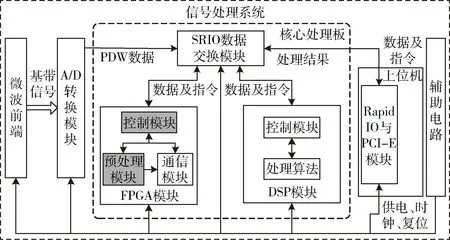

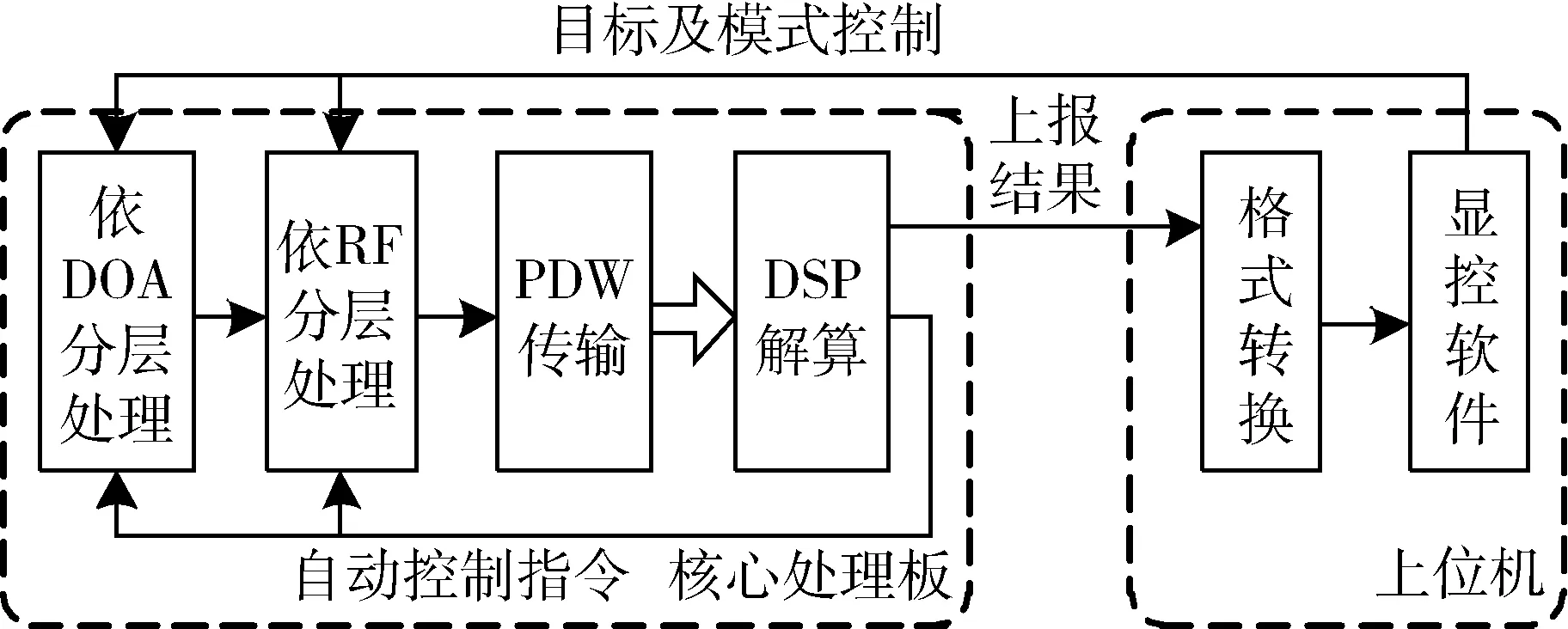

1 系统总体设计

信号处理系统的电路总体设计基于多DSP+FPGA架构,系统总体设计框图如图1所示。从功能上看,系统可分为DSP模块、FPGA模块、SRIO数据交换模块、PCIE模块、AD转换模块以及包括各电平转换模块、电源、时钟和控制逻辑等在内的辅助电路,在必要的驱动程序和板内控制逻辑配合下,形成一个完整的、一体化的数字系统硬件平台。其中,DSP模块、FPGA模块、SRIO数据交换模块构成了系统的核心处理板。本系统中,DSP采用主从模式工作,采用Hyperlink进行通信。DSP之间形成JTAG(Joint Test Action Group)菊花链,连接到J30J-31调试接口上[4]。核心处理板内部设计有大吞吐量的SRIO通信机制。通过在上位机中设计的SRIO与PCIE转换模块,可实现上位机对多块核心处理板的控制以及二者的数据通信。

图1 系统总体设计框图

2 实现方案

2.1器件选型

图2 预处理过程

本系统中,SRIO交换芯片选用Tsi578,其支持80 Gb/s的聚合带宽。Tsi578系列交换机具有极强的伸缩性,使其在联网、无线与视频基础架构领域得到了广泛的应用[5-6]。Tsi578可灵活地支援多达8个4x模式或者16个1x模式的埠,交换机的埠与埠之间相互独立,可支持多种速度、宽度配置,这也就意味着可用较低的成本开发出功能强大、性能卓越的系统。DSP选用德州仪器(TI) 最新推出的TMS320C6678[7]数字信号处理器。C66xx系列数字信号处理器是目前具有最高定/浮点运算能力的新一代数字信号处理器。TI C66xx系列多核DSP结合了之前C64xx与C67xx的优点,单核最高主频可达1.4 GHz[8]。FPGA芯片选用Xilinx公司的Virtex-7 XC7VX485T[9]。Virtex7系列芯片是Xilinx公司2014年初推出的新一代可编程器件产品,是Xilinx在通用28 nm架构上构建的三大系列之一,与前代产品相比,能够以低于一半的功耗实现两倍左右的性价比,Kintex7 XC7VX485T的主要性能指标见表1。

表1 Virtex7 XC7VX485T的主要性能指标

2.2预处理设计

现有的信号处理算法对信号的样本存在着诸如信号完整性高、信号可进行周期积累等需求,而且工程化实现难度较大。但是,复杂的战场电磁环境又对信号处理提出了实时性、准确性的要求。基于此,本系统重点对信号处理系统的预处理过程进行了设计。预处理过程如图2所示。

2.2.1依DOA分层处理

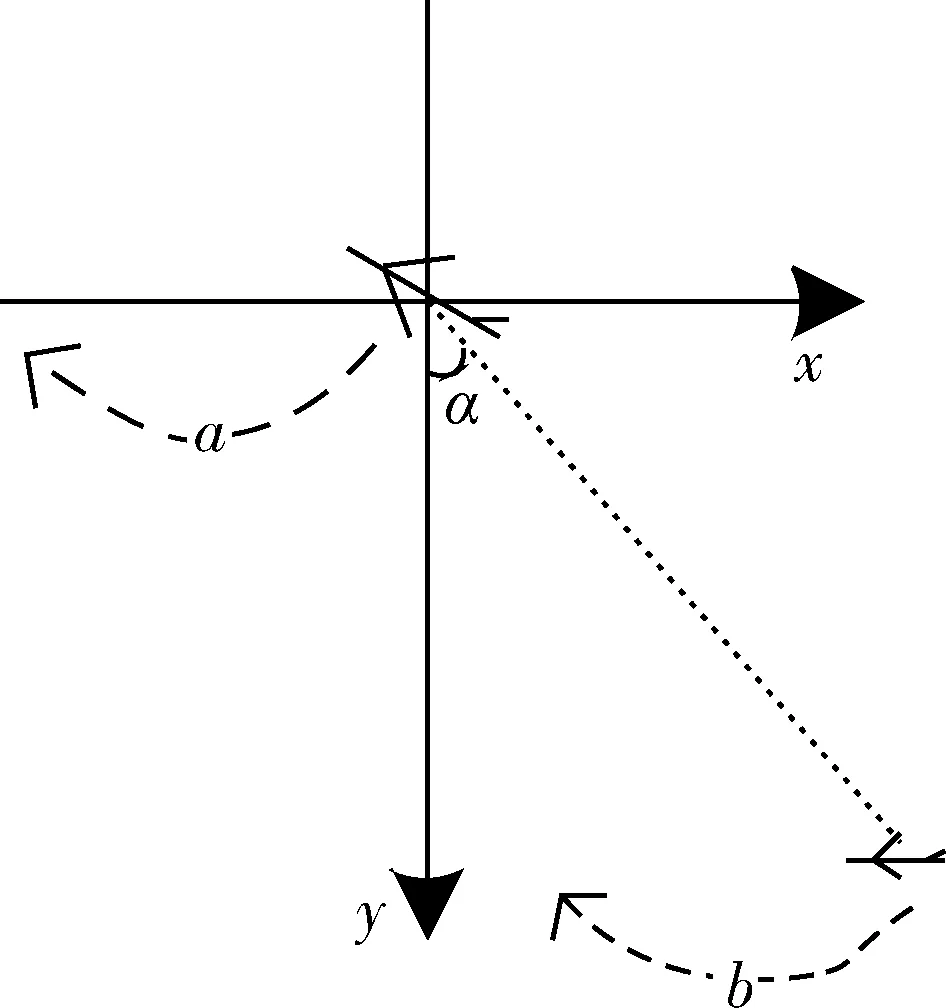

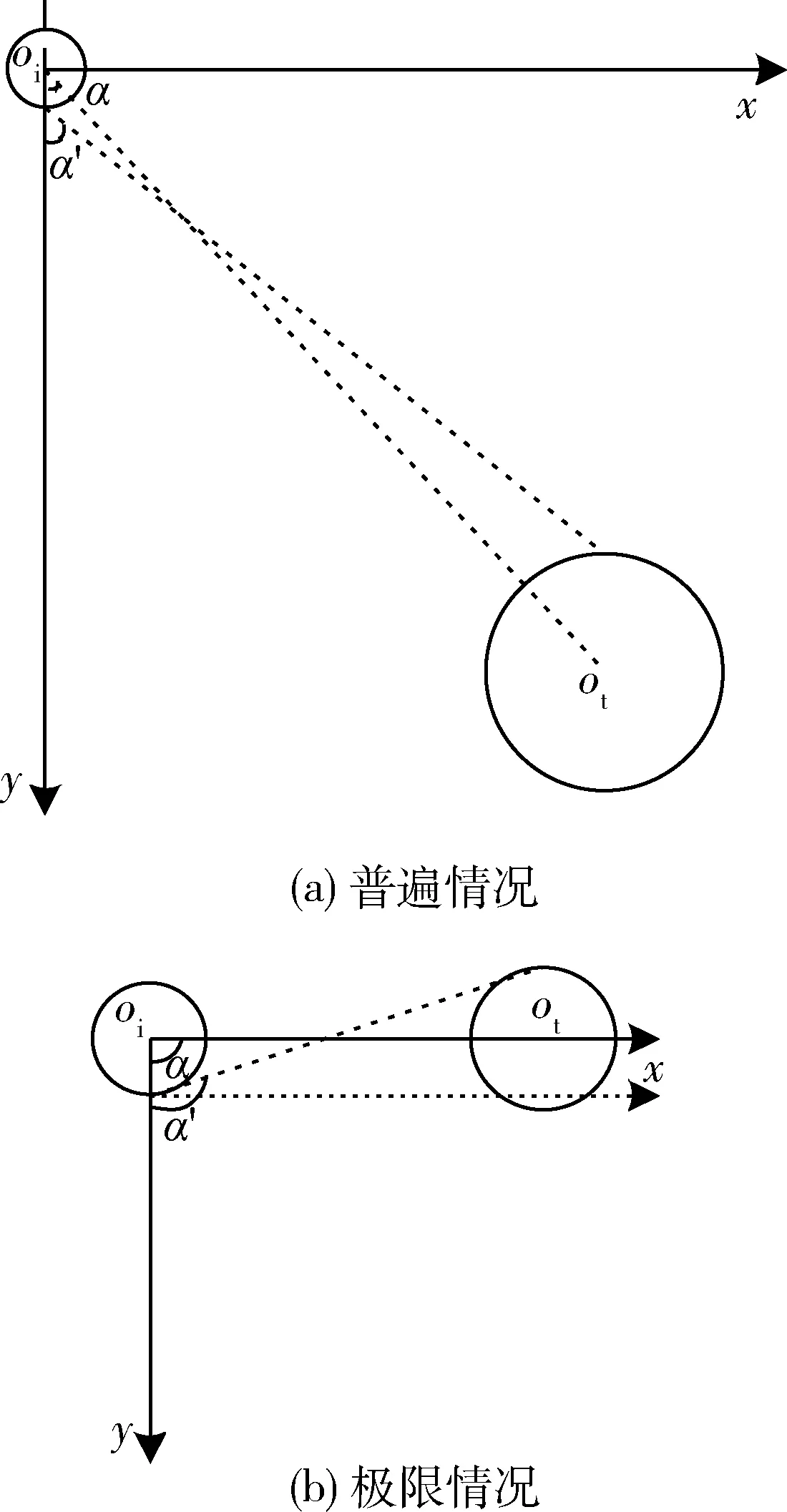

在战场电磁环境中,敌我双方作战平台一般情况下不会处于同一高度,DOA的测量是基于方位分量进行解算的,其测量示意图如图3所示。α即为DOA,a,b两条曲线示意其可能的运动路径。

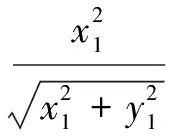

考虑一种普遍情况:t0时刻,以我方侦察平台为原点建立直角坐标系,确保敌方作战平台处于第一象限内,由于在第一象限内,sinα的单调性与α相一致,便于思考和讨论。此时刻DOA的大小α可以用sin(α)来表示:

(1)

式中,(x1,y1)表示此时刻敌方作战平台的所在位置。考虑此时刻以我方侦察平台建立参考系,可得在任何时刻都可以建立如式(1)的表征关系。对式(11)分别求一次偏导数可得:

图3 DOA示意图

(2)

从式(2)可以得出,在(x1,y1)均为0时,两个偏导数为0,此时,不符合其物理意义。设敌方作战平台再次照射的时刻为t1,此时敌我双方的战场态势如图4所示。在实际的战场电磁空间中,我方侦察平台会尽可能远离敌方作战平台。那么t1时刻有以下方程成立:

(3)

Δαmax=α′-α=

(4)

而对反正弦函数的特性进行分析可知,反正弦函数是一个单调递增的函数,且随着自变量的增大,函数增长越缓慢。图4所示的极限情况是DOA变化最大的情况。

(5)

无论是机械雷达还是电扫描雷达,其信号的重访时间都小于1 s[10-11]。远距离侦察平台的防御能力差,飞行速度低,故一般情况下,侦察平台的侦收距离应位于敌方的中远程防空导弹射程外。以典型的中程空空导弹射程及歼击机巡航速度为参考,此时DOA的最大变化仅约为0.77°。但考虑到侦察平台的测角误差δs,也为了保证尽可能覆盖住侦测目标,同时节约系统资源消耗,在本信号处理系统设计中确定DOA的初始划分间隔为20°。

图4 敌我双方战场态势

2.2.2依RF分层处理

在战场电磁环境中,多种用频设备共存,电磁信号相互交织,各种频率成分的信号共同组成了现代战场电磁环境。正是由于信号多样化,才对现代信号处理系统提出了更为严峻的挑战。考虑到一种作战平台上不止一种用频设备或者集群编队的情况,对DOA分层处理后的数据依照RF进行二次分层。

雷达的工作波段基本是以现行的雷达波段划分的。为此,本级预处理的初始阈值均按照各雷达波段范围展宽1 GHz进行设计,覆盖了50 MHz~40 GHz的频率范围。预处理完成后的PDW流按照不同的阈值分配不同的逻辑通道,发送给DSP进行后续处理。

2.3控制设计

预处理过程参照了信道化的思路进行设计,虽然达到了稀释脉冲的目的,但是由于各个逻辑通道的数据相互交叠,给后续的处理结果上报增加了一定的处理难度。为此,待信号处理完成后,需要调整各个逻辑通道的输入数据调整,以获取最高的运行效率。控制流程如图5所示。

图5 控制流程

控制模式分为人工和自动两种。在人工模式下,可以人为地筛选关注目标,从而调整两级分层处理阈值,优化计算资源分配,进行详细观察和管理,同时可以剔除部分无关频率信号,进一步提升系统效率。在自动模式下,系统根据初步分选结果对两级分层处理阈值进行调整,依据威胁度等级对运算资源加以调度,提高对未知信号的关注度,兼顾系统的实时性与准确性。在两种模式下,系统都会实时监测DSP的运行状态,协调DSP的运算资源使用。

3 测试与分析

本系统的FPGA程序在Xilinx公司提供的FPGA开发环境Vivado 2016.3下使用Verilog 语言进行编程,将关键的预处理模块进行了封装,将预处理模块的内部工作时钟约束到250 MHz ,进行综合实现,布局布线的结果表明系统能够满足250 MHz时钟的时序要求,但是预处理模块需要对数据进行整理,消耗了大量的存储资源,具体资源消耗见表2。

表2 资源消耗情况

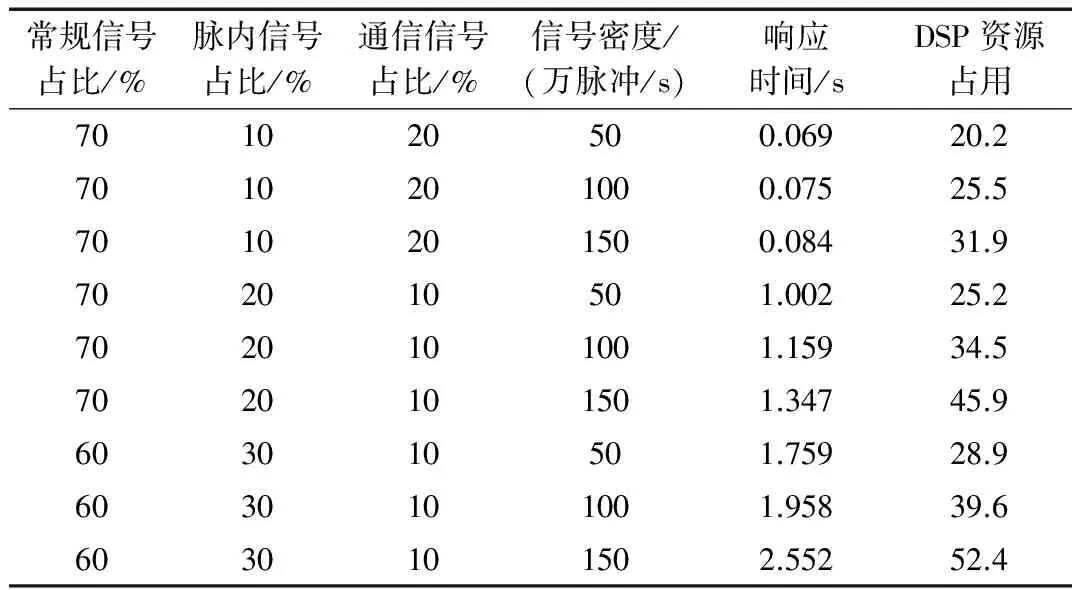

本文使用模拟雷达信号对系统进行了性能测试,测试信号包含常规信号和脉内调制信号以及通信信号。测试结果如表3所示。

表3 性能测试结果

从表2和表3可知,系统对高脉冲密度的雷达信号具有较强的处理能力,实时性较高。相对来说,脉内调制信号对系统的响应时间和DSP资源占用影响较大。

4 结论

本文提出的高脉冲密度雷达信号处理系统设计,采用多DSP+FPGA的系统架构,具有高速信号处理能力和高宽带的内部数据通道。该信号处理模块能够适应高达数百万脉冲每秒的脉冲密度,且已经成功应用于某信号处理系统中,系统运行稳定可靠,具备了高性能的数据交换和数据处理能力。

[1] GE Fanuc embedded systems,Inc. VPX: VMEbus for the 21st century[Z].2007.

[2] Mercury computer systems, Inc. Technology overview:VITA 46(VPX)[Z].2006.

[3] 郑东卫,陈矛,罗丁利.VPX总线的技术规范及应用[J].火控雷达技术,2009,38(4): 73-77.

[4] 董选明.基于4DSP+FPGA架构数据处理板设计[J].电子技术应用,2016,42(7):29-33,37.

[5] TUNDRA Inc. Tsi578 serial rapidl0 switch user manual[EB/OL]. (2016-06-06)[2017-04-23].http://www.idt.com.

[6] Tundra Semiconductor Corporation. Tsi578 serial rapidIO Switch hardware manual[EB/OL]. (2016-04-04)[2017-04-23]. http://www .idt.com.

[7] 王韩,孙红胜,陈昌明.基于TS201与FPGA的数字信号处理系统设计[J].现代电子技术,2016,39(5): 78-80.

[8] Texas Instruments. Data Manual:TMS320C6678 multicore fixed and floating-point digital signal processor[EB/OL]. (2014-03-06)[2017-04-23]http://www.ti.com.

[9] 王龙,杨承志,尚卫华,等.基于RF DAC的宽带高斯声源的设计与实现[J].微型机与应用,2016,35(17):26-27.

[10] 中航工业雷达与电子设备研究院.机载雷达手册[M].北京:国防工业出版社,2013.

[11] 赵登平,周万幸,鞠新春.世界海用雷达手册[M].北京:国防工业出版社,2012.

2017-04-23)

王鸿超(1994-),男,在读硕士研究生,主要研究方向:低截获概率雷达信号侦察处理技术。

耿常青(1994-),男,在读硕士研究生,主要研究方向:低截获概率雷达信号侦察处理技术。

王龙(1992-),男,硕士,讲师,主要研究方向:低截获概率雷达信号侦察处理技术。

The radar signal processing system design of high pulse density

Wang Hongchao1, Geng Changqing1, Wang Long1, Tong Wenfeng2

(1. Faculty of Information Countermeasure, The Aviation University of Air Force, Changchun 130022, China; 2. 94691 Troops of PLA, Longyan 366200, China)

With the continuous upgrading of radar system, the signal density of electromagnetic space is also increasing.To constantly adapt to the electromagnetic environment and meet the requirement of high density of pulse radar signal processing, this paper designed a set of signal processing system of DSP+FPGA structure based on TI TMS320C6678 chips and Xilinx XC7VX485T chips.The core of this system is to design and realize the reasonable data pretreatment process, and implemen it through the concrete hardware circuit. The signal processing board is conformed to VPX standard, and can work in airborne, vehicle or other harsh conditions of special equipment. Through the pretreatment design, it effectively improved the processing power of the system.

high pulse density; pretreatment process; FPGA; DOA

TN974

A

10.19358/j.issn.1674- 7720.2017.22.012

王鸿超,耿常青,王龙,等.高脉冲密度雷达信号处理系统设计J.微型机与应用,2017,36(22):41-44.

国家自然科学基金(61571462)