一种脉冲雷达数字AGC的设计与FPGA实现

许彦章,黎文杰,吴 刚

(上海无线电设备研究所,上海 200090)

一种脉冲雷达数字AGC的设计与FPGA实现

许彦章,黎文杰,吴 刚

(上海无线电设备研究所,上海200090)

分析了雷达的自动增益控制的原理,提出了一种适用于脉冲雷达的数字化AGC的设计与实现方案,对于数字AGC的控制模块及电压与功率在不同输入条件下的关系进行了详细的介绍,在FPGA的软件设计及实现算法的基础上,通过线性调频信号雷达系统进行验证,试验结果表明方案具有收敛速度快、控制精度高等特点。

数字增益控制;可编程逻辑器件;排序;线性调频信号

0 引言

自动增益控制(AGC)在雷达系统中用于调整中频接收机的动态范围,当雷达探测位于最远距离的最小目标时,目标回波信号最小;而当探测最近距离的最大目标时,目标回波信号最大。

脉冲雷达自动增益控制(AGC)根据接收信号幅度变化自动对接收机的增益进行调整, 匹配整个接收通路中的动态范围[1]。自动增益控制(AGC)在脉冲雷达中频接收机中的功能:第一,防止信号过大引起接收机失真。中频接收机在不同距离模式下目标回波强度接收机工作在线性动态范围内,不存在较大的失真,保证和差通道的相位差能够稳定对角度进行精确测量。第二,补偿接收机增益的起伏。实际舰船目标测量过程中符合Swinling慢起伏模型,为保证回波信号在帧周期内保证一定稳定回波信号范围。

传统的模拟AGC主要在中频接收机对和通道闭环中实现,模拟AGC受到放大器、检波电路及低通滤波等器件特性影响[2],通常无法适应现代雷达脉冲宽度变化范围大、重频抖动等特点,导致滤波响应慢,控制时常数较大,对抗干扰差。数字AGC基本原理是对归一化通道进行ADC采样后量化处理,估计脉冲雷达距离门内量化后信号的幅度,通过查表对数化输入功率,调整中频接收机增益,控制回波信号幅度在一定时间处于设定的范围内[3]。随着可编程逻辑器件及数字信号处理的快速发展,本文数字AGC逻辑计算及控制部分由高性能信号处理机实现,增益放大及衰减控制由中频接收机高精度DAC实现,具有控制灵活度高、控制精度高、稳健性强等特点[4],同时具有自动数字AGC与手动控制AGC的功能。

1 数字AGC设计与分析

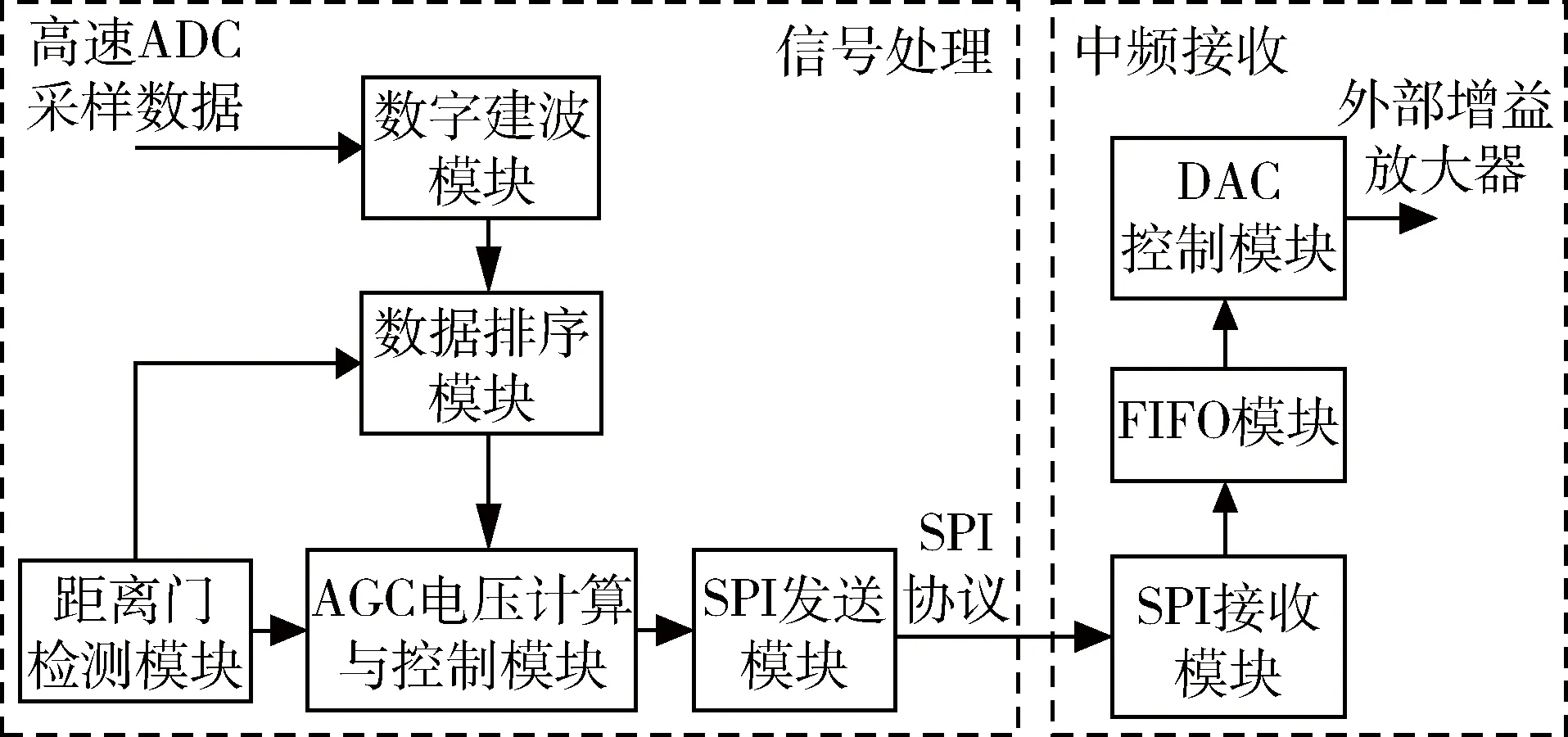

本文数字AGC的设计主要包括两个部分:一部分由信号处理机实现,完成AGC逻辑计算与控制;另一部分由中频接收机实现,完成AGC量化增益控制。两者之间通过串转并接口(SPI)协议通信,实现自动增益控制,如图1所示。

图1 数字AGC模块结构图

1.1数字AGC逻辑计算与控制

假定中频线性调频脉冲信号(LFM)为:

sr(n)=A(n/fs)·cos(2πf0(n/fs)+μπ(n/fs)2)

(1)

其中,A为中频信号,fs为采样量化频率,μ为调频斜率,n为从距离门起始点N0到距离门终止点NM的采样点数。

经过数字ADC直接采样后,量化为N位比特位,用数字检波的方式得到信号的幅度包络C(n)为:

C(n)=A(n/fs)

(2)

当脉冲信号距离门上升沿时,滑窗比较输入信号幅度值,并按照幅度值进行由大到小滑窗排序,设计保留距离门内最大若干个幅度值,实现过程如图2所示。得到距离门内排序后的最大K个信号幅度值为(由大到小):

{C1C2…CK}

(3)

图2 检波排序估计算法

在距离门下降沿到达时,完成回波信号幅度排序,为防止采样信号过冲影响,剔除L个野值,采用均值法估计脉冲信号距离门内数字检波后幅度值为:

(4)

数字检波后的第k个脉冲信号的功率为Pk,要求中频接收机第k+1的脉冲信号和通道归一化功率为P0,则需要控制的增益变化为:

(5)

其中Cest表示第k个脉冲估计的幅度值,C0表示归一化电平值。

工程实现中,对数计算复杂度高,不利于数字可编程逻辑器件(FPGA)实现,可以通过查表法设定若干挡位的增益[5],本文中采用增益变化ΔG的范围为-10 dB~+10 dB,步进1 dB,通过增益步进调整,调整收敛归一化电平门限范围内。

1.2数字AGC电压与功率增益的关系

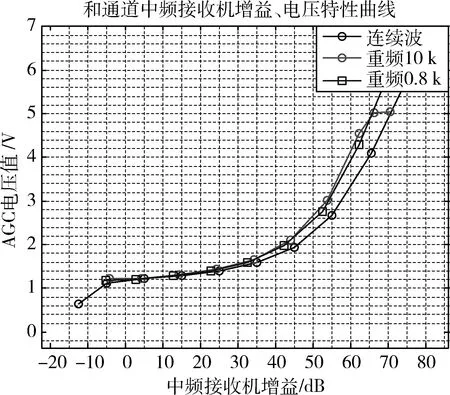

中频接收机的功率增益放大器与AGC电压成对数线性关系,传统脉冲雷达采用的功率增益的动态范围为-10 dB~60 dB,符合线性区,当功率增益超过60 dB,功率放大进入饱和区。图3给出某中频接收机AGC电压与输出增益之间的关系。

图3 不同重频下增益与电压对应关系

从图3中可以看出,数字AGC电压控制范围在1.2 V~5.2 V之间,根据第k个脉冲信号增益及增益变化得到第k+1个信号增益为:

Gk+1=Gk+ΔGk

(6)

根据图3利用中频接收机接收输入的AGC电压值与接收机增益之间的关系,计算第k+1次电压控制值为:

Vk+1=f(Gk+1)

(7)

1.3AGC电压与功率增益的拟合

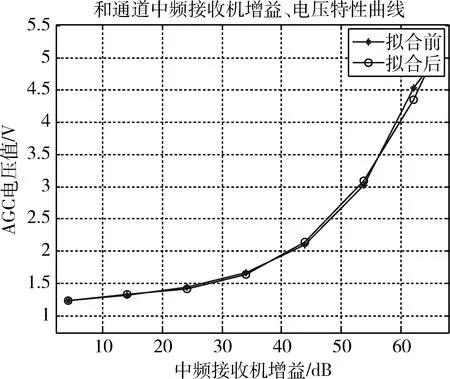

为了便于信号处理的FPGA实现,在保证控制精度的条件下,对中频接收机电压与功率增益在线性区进行拟合,拟合采用三阶拟合函数,图4给出拟合后曲线与拟合前测试曲线之间的关系,拟合后对应关系为:

(8)

为了保证计算的精度,满足一定动态范围,在得到当前增益后,计算AGC电压时,拟合后曲线的系数b2、b1、b0按照多项式扩位后虚位运算,得到AGC电压控制码。

图4 AGC电压与功率增益拟合前后对比

2 数字AGC的实现

本文实现信号处理的AGC逻辑计算与控制在Xlinix公司的FPGA芯片XC5VSX95T实现,归一化模数转换器(ADC)采样芯片为14 bit,实现的逻辑模块包括ADC数字检波模块、排序模块、数字AGC自动控制模块。中频信号放大增益采用数模转换器(DAC)输出模拟电压,控制放大器对信号进行调整到归一化电压范围内。表1给出了实现的数字AGC的硬件参数指标。

表1 数字AGC的参数表

从表1可以看出该数字AGC能够满足大的信号动态范围,在脉冲重复频率以及脉冲宽度、信号带宽有较强的适应性;为减少数据运算、减少占用FPGA的寄存器等逻辑资源,在数字AGC排序阶段,取量化输入的ADC的高八位,计算功率检波电压的值。通过查表对数运算,计算控制电压的增益变化值。通过增益拟合曲线,得到AGC控制电压值。

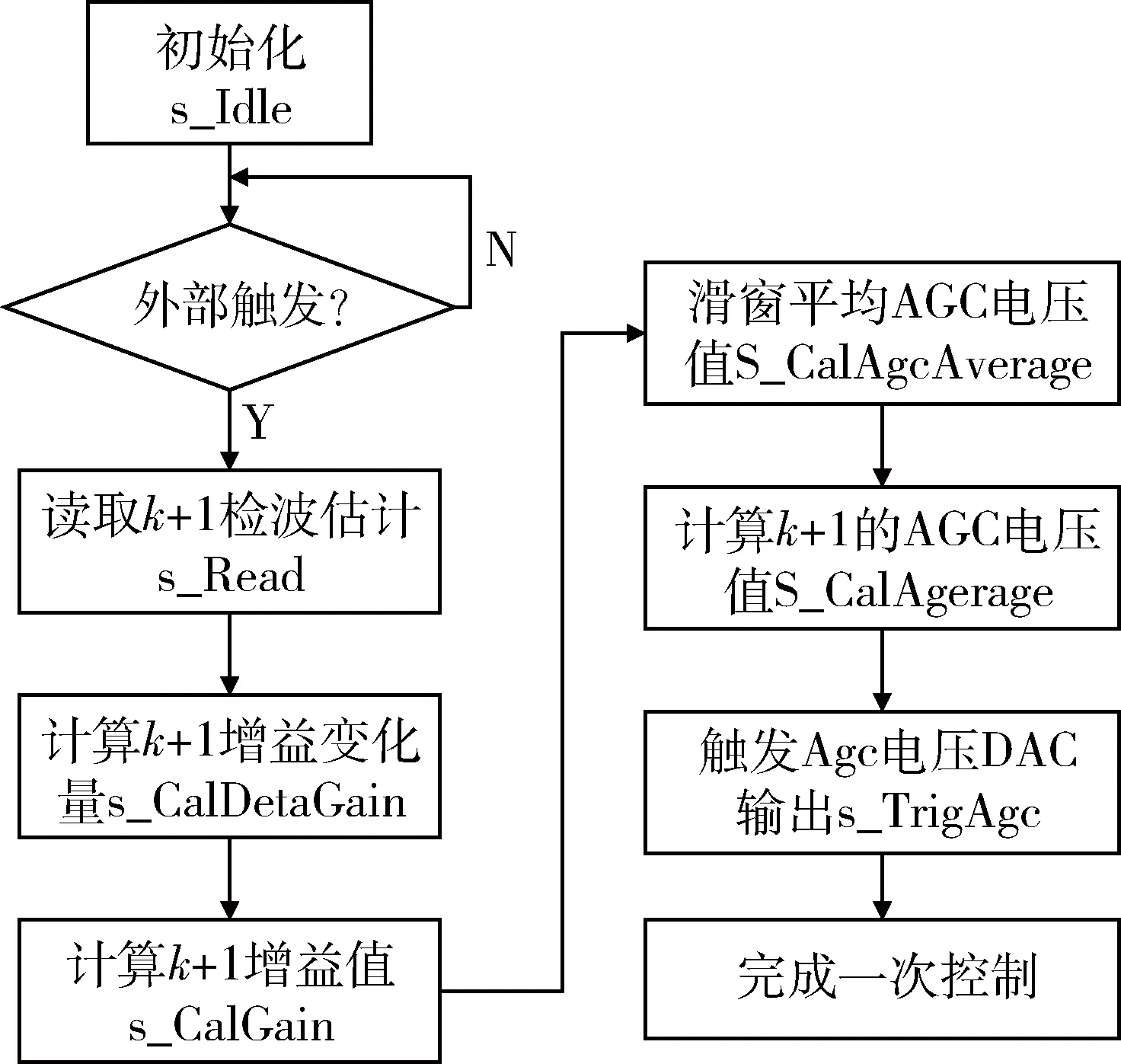

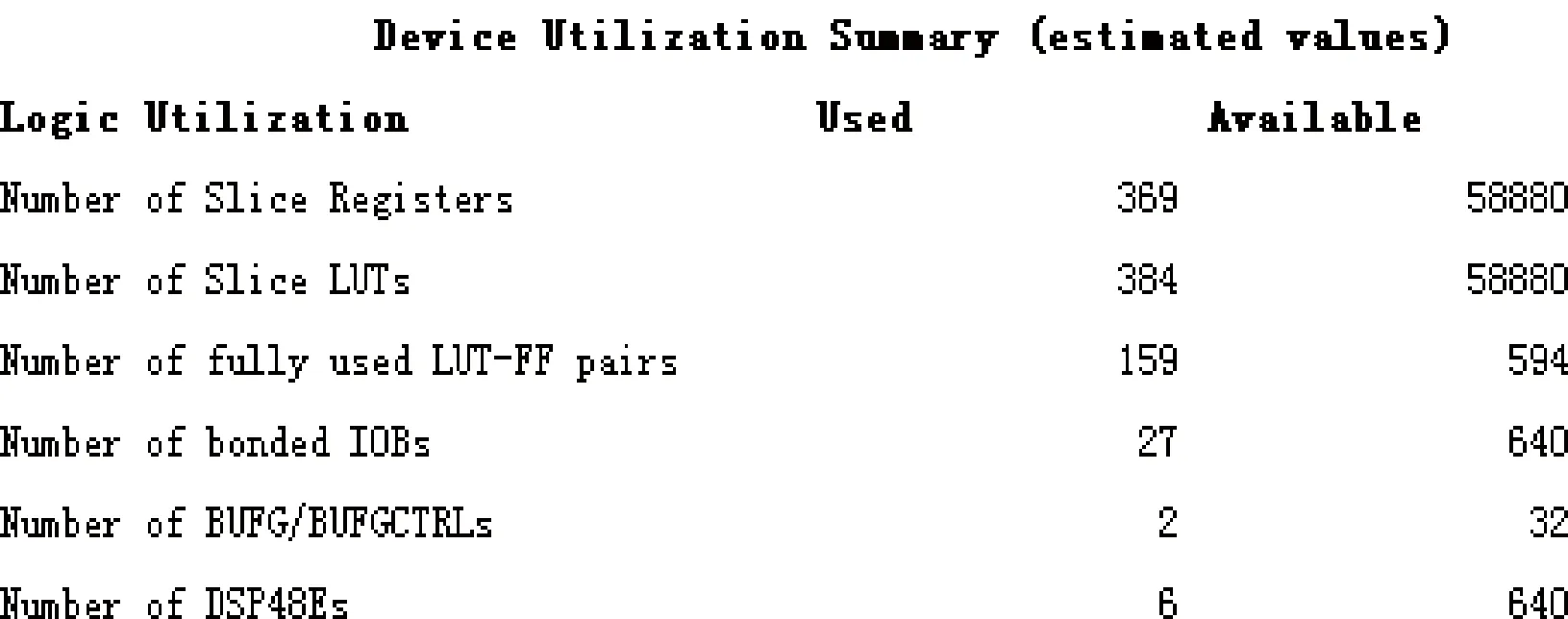

图5给出AGC增益控制实现的状态机,由于脉冲雷达信号通常是缓变信号,通过多个脉冲的滑窗平均估算下一个脉冲控制电压,为保证AGC电压控制在一定范围内,不出现信号振荡,设置增益变化率门限小于T时,输出增益变化率为0 dB,不进行电压控制。图6给出实现数字AGC控制的FPGA资源使用情况,最大系统工作时钟为100 MHz,满足工作时序要求。

图5 AGC增益控制状态机

图6 数字AGC控制FPGA资源利用

3 实验结果及分析

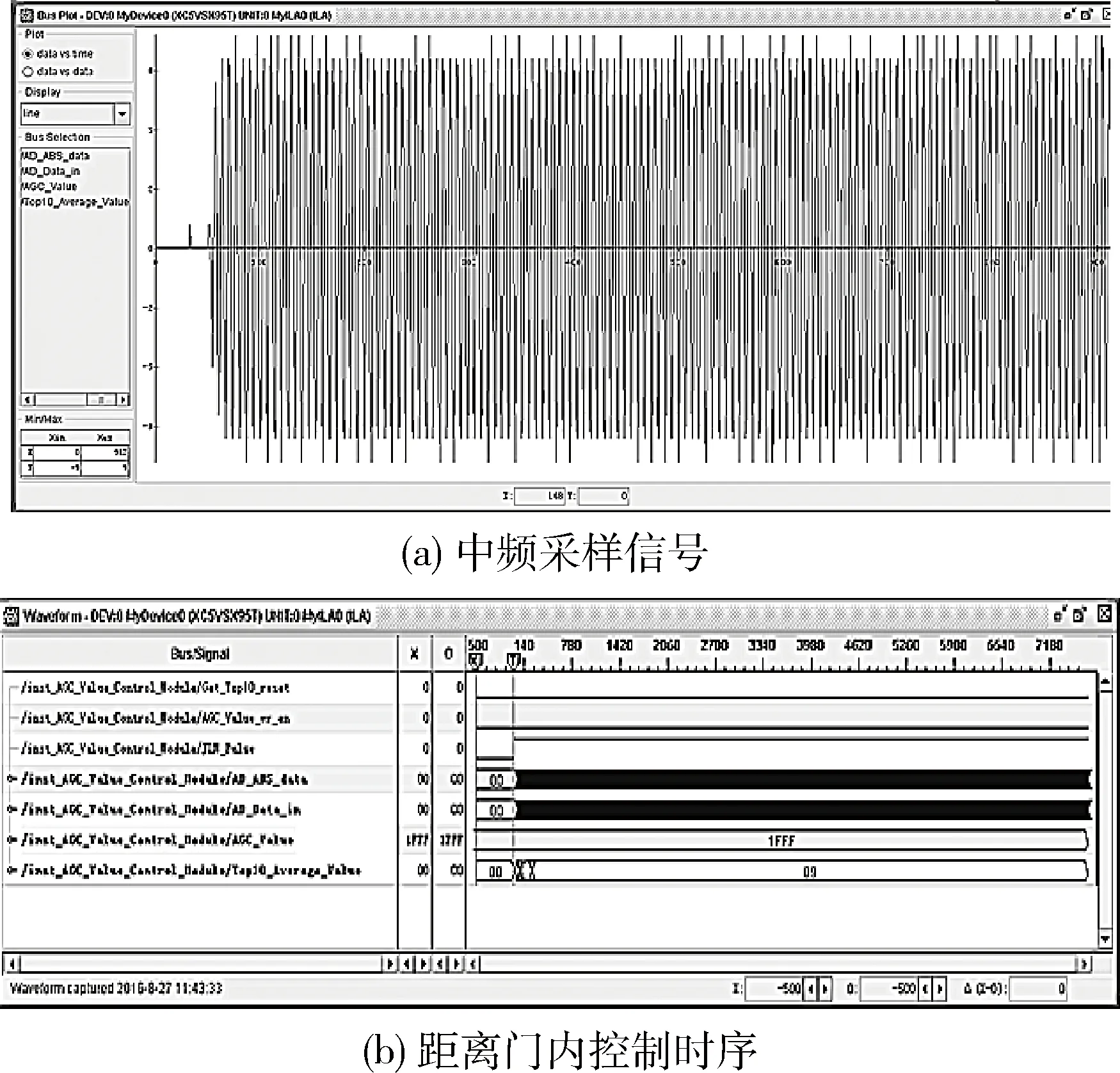

本文实验采用Xlinix公司的Vertix-5芯片 XC5VSX95T实现FPGA的主要软件算法[6],采样频率为200 MHz、输入中频信号为250 MHz、带宽为40 MHz的线性调频信号(LFM),脉冲宽度采用100 μs。

AGC初始值采用手动模式设置,通过模拟DAC输出,控制AGC电压到50 mV(截取ADC高8位)。图7给出使用FPGA在线调试工具ChipScope捕获的信号,图7(a)表示控制前AGC输出后的数字采样信号,图7(b)表示控制前的AGC控制码时序。

图7 手动数字AGC控制前信号

图8给出自动数字AGC控制后模拟DAC输出,控制AGC电压到500mV(截取ADC高8位)。其中图8(a)表示控制后AGC输出后的数字采样信号,图8(b)表示控制后的AGC控制码时序。

图8 自动数字AGC控制后信号

4 结论

为了满足雷达信号处理中频接收机对脉冲信号的自动增益控制的需求[7],本文提出一种应用于脉冲雷达的数字化中频接收机自动增益控制的FPGA实现方法,并对系统实现的功能进行了测试。测试结果表明,该设计实现可有效满足中频接收机对脉冲信号快速性、灵活性的需求,具有广泛的应用前景。

[1] 胡俊杰,叶永杰,帅明.数字中频接收机中数字AGC的设计与实现 [J] .通信对抗,2015,34(1):29-33.

[2] 张松柏,李红虎.数字AGC技术在跟踪雷达上的应用[J] . 舰船电子对抗, 2014,37(1):53-56

[3] 任建,黄海生.一种GPS 接收机中自动增益控制的设计[J] 电子设计工程, 2015,23(12):58-60.

[4] 童智勇,陈佳民,等.用于星载SAR数字AGC增益控制的双门限步进法[J] .遥感技术与应用,2007,22(1):83-87.

[5] 朱璐,邹波,江利中. 脉冲雷达自适应步进数字AGC设计与仿真[J].制导与引信,2014,35(2):22-27.

[6] 贲德,韦传安,林幼权.机载雷达技术[M].北京:电子工业出版社机,2006.

[7] 王银铃,李华春. 基于FPGA的多通道并行高速采样研究[J].微型机与应用,2015,34(9):37-39.

2017-04-25)

许彦章(1983-),通信作者,男,硕士研究生,工程师,主要研究方向:雷达信号处理。E-mail:xuyanzhang209@163.com。

黎文杰(1983-),男,硕士研究生,工程师,主要研究方向:雷达接收机。

吴刚(1987-),男,硕士研究生,工程师,主要研究方向:信号处理机。

Design and implementation of digital automatic gain control with pulse radar on FPGA

Xu Yanzhang, Li Wenjie, Wu Gang

(Shanghai Radio Equipment Research Institute, Shanghai 200090, China)

A kind of design and implementation of digital automatic gain control(DAGC) with pulse radar is proposed after researching the principle of AGC,digital automatic gain control module, and the relationship between voltage and power under different input conditions are mainly introduced. On the basis of FPGA software design and implementation of algorithms, validation of algorithms is verified based on radar system of linear frequency modulated (LFM) signal. The results indicate this digital automatic gain control is fast-convergence and high-precision.

DAGC; FPGA; sort; LFM

TP952

A

10.19358/j.issn.1674- 7720.2017.22.007

许彦章,黎文杰,吴刚.一种脉冲雷达数字AGC的设计与FPGA实现J.微型机与应用,2017,36(22):23-25,29.