基于XC6SLX45T平台的PCIe数据卡设计

,,,

(南京南瑞集团公司,南京 211100)

基于XC6SLX45T平台的PCIe数据卡设计

朱孟江,王元强,聂云杰,洪昊

(南京南瑞集团公司,南京 211100)

为提升数据传输速率、提高数据处理灵活性,提出一种基于FPGA的的PCIe数据卡设计方法。该方案选用Xilinx公司的XC6SLX45T平台,采用IP核的方式设计了一款PCIe数据卡。该卡采用DMA传输模式,通过DMA读写提高传输速率,其数据传输速率可达到400 Mbps。

FPGA;IP核;PCIe;DMA

引 言

PCI-Express(简称PCIe)总线的出现,完全地改变了原本的PCI总线的并行技术,PCIe采用的是新型的串行点对点技术,改善了PCI总线传输速度以及系统带宽方面的本质问题。PCIe总线的提出,弥补了PCI总线的不足之处,PCIe总线将发展成为取代PCI总线的新型数据总线[1]。

目前电力行业业务复杂、数据繁多,根据电监会5号令《电力二次系统安全防护规定》的要求,各发电企业、电网企业、供电企业内部基于计算机和网络技术的业务系统在安全区I和安全区II之间以密文的方式进行通信。软件密码算法不仅消耗硬件CPU资源,且存在较大安全隐患,速度也受硬件资源的限制,这就需要设计一款高效、快速的硬件数据加密卡。目前市场上数据对称加解密速度均在400 Mbps左右, SPI、UART等串行接口性能远远不够,USB和以太网又不方便集成到服务器,因此选用Xilinx PCIe解决方案,同时FPGA在数据处理方面也具有很大的灵活性。

本文将以Xilinx公司的Spartan-6为平台,阐述PCIe IP Core的方案及其优化策略,并着重描述其DMA和传统终端模式,配合上位机测试程序进行相关数据测试。该方案具有方便、可集成性、速度快等优点,已在电力调度系统中得到广泛的应用。系统集成示意图如图1所示。

图1 系统集成示意图

1 PCIe原理

1.1 PCIe简介

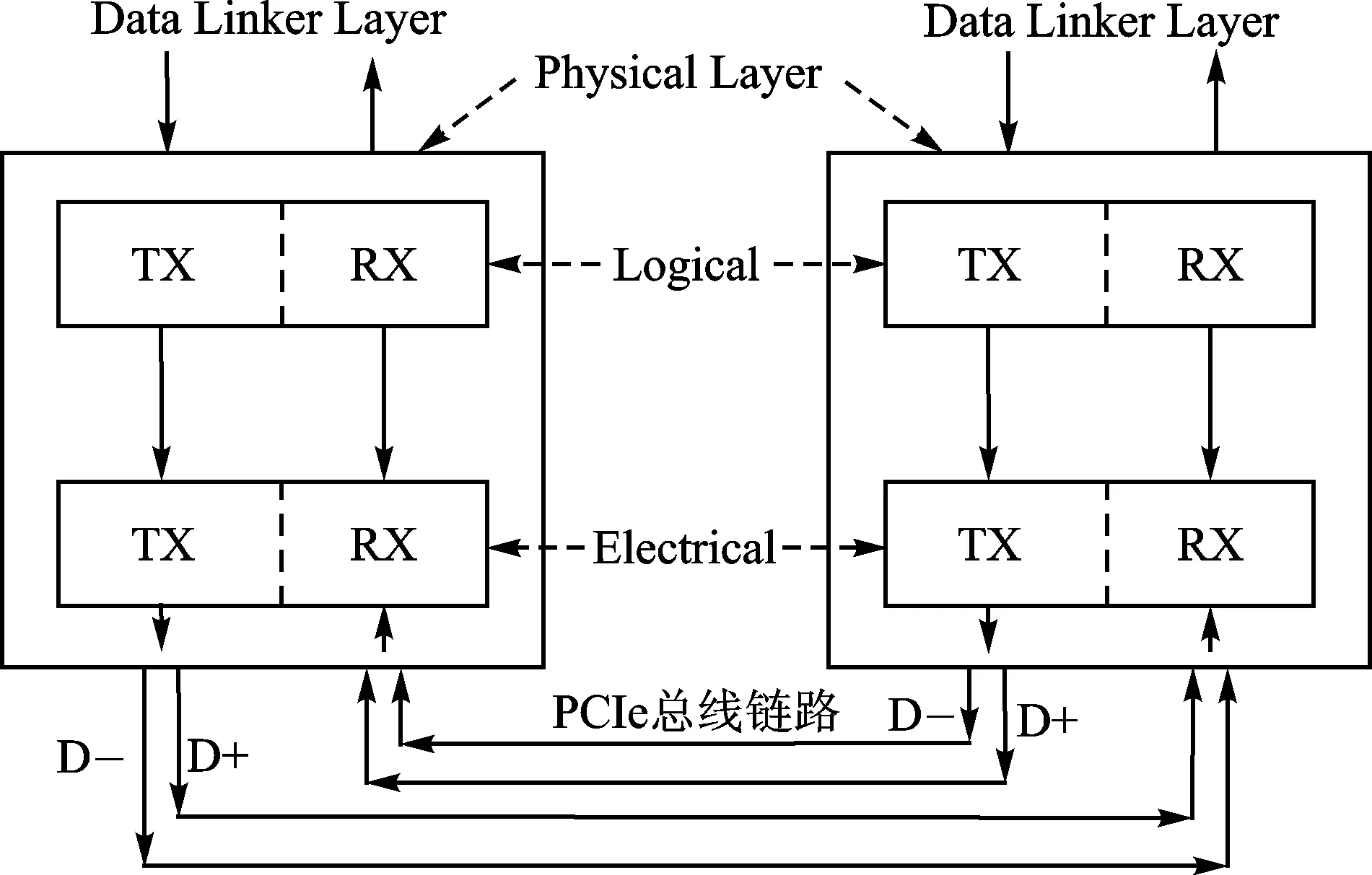

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而总线接收端接收数据时也使用这些层次。PCIe总线使用的层次结构与网络协议栈较为类似,由事物层、数据链路层和物理层组成。PCIe发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图2 所示。

图2 PCIe总线物理链路

1.2 PCIe IP核

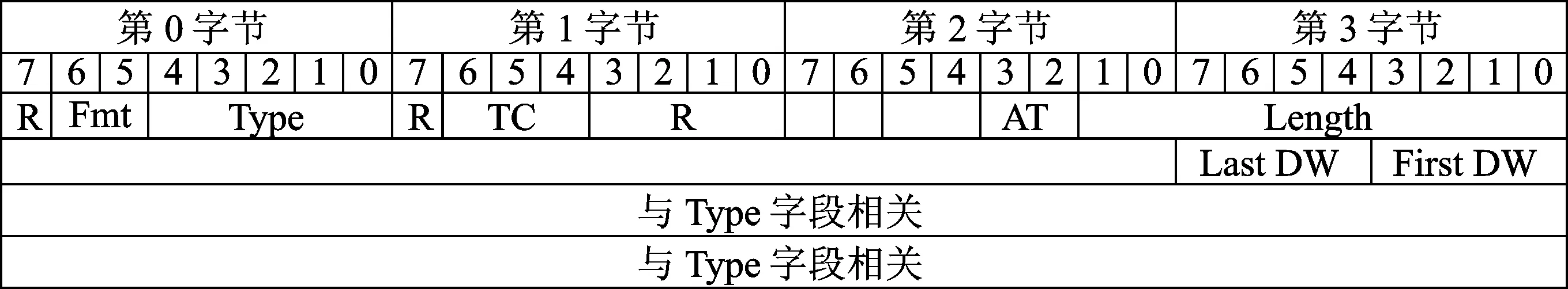

用FPGA实现PCIe功能,简单地说就是完成TLP包的处理,即事物层数据协议的处理。TLP由三部分组成:帧头、数据、Digest段。

TLP帧头长为3或者4个DW,格式和内容随事物类型变化。数据段为TLP 帧头定义下的数据段,如果该TLP不携带数据,则该段为空。Digest段(Optional)是基于帧头、数据字段计算出来的CRC,又称为ECRC,一般Digest段由IP 核填充,所以PCIe的处理在用户层表现为处理TLP中帧头和数据段。TLP包中各个字段含义不再一一解释,可参照《PCI Express体系结构导读》一书。TLP格式如图3所示。

图3 TLP格式

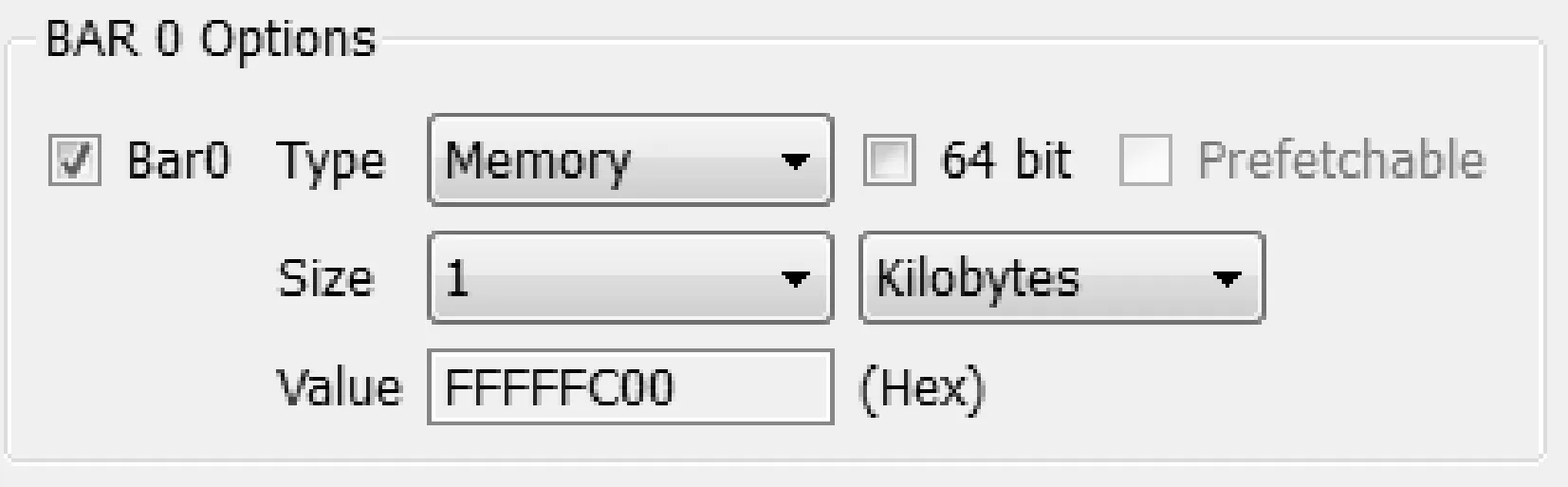

1.3 PCIe接口空间配置

PCIe通信是靠发送TLP包完成的,读写包里都有地址信息。如果板卡向PC发送TLP包,例如MWr包,那很好理解,地址信息就是PC的物理地址;如果是MRd包,则PC收到后回复一个完成包,板卡从完成包分析出数据即得到MRd读取地址的数据。那PC如何读写板卡的数据呢? PC启动时BIOS探测所有的外设。对PCIe设备来说,BIOS检测到板卡有多少个BAR(Base Address Register)空间,每个空间有多大,然后对应为这些BAR空间的分配地址。对PC设备来说,它能“看”到PCIe板卡的空间只有BAR空间,只能访问这些BAR空间。板卡可以发送合法的PCIe TLP包,并得到PC端的响应,但是PC端访问板卡被局限在BAR空间。本方案PCIe BAR空间仅设置为BAR0空间,配置如图4所示。

图4 BAR0空间设置

2 程序设计

2.1 PCIe设备驱动

PCIe设备驱动与PCI一样,与普通设备驱动没有太大差别,具备open、close、ioctl、read、write等接口函数,实现方式大同小异。与普通字符设备驱动的区别主要在probe函数上,PCIe设备驱动比普通字符设备驱动多了一个probe探测函数,该函数主要有如下功能:

◆ 驱动加载时,将PCIe的BAR0空间映射到主机并为DMA申请内存空间;

◆ 为PCIe设备申请中断,并分配中断号;

◆ 初始化驱动读写队列。

PCIe设备驱动代码如下:

static int __devinit fpga_probe(struct pci_dev *pdev, const struct pci_device_id *id){

……

pci_enable_device(pdev);//enable PCIe

pci_set_master(pdev); //设置成总线主DMA模式

……

PhysicalBase0Addr=pci_resource_start(pdev,BAR_0);

PhysicalBase0len=pci_resource_len(pdev,BAR_0); //将PCIe内存空间映射到主机

fpga_priv.PCI_Base0_Addr=ioremap( PhysicalBase0Addr, PhysicalBase0len);

fpga_priv.dma_buf = pci_alloc_consistent(pdev,PKT_LEN,&fpga_priv.dma_buf_t);

if(fpga_priv.dma_buf==NULL)

return ERROR;

init_waitqueue_head(&fpga_priv.read_wait);//初始化读队列

init_waitqueue_head(&fpga_priv.write_wait); //初始化写队列

fpga_priv.irq = pdev->irq;//为PCIe设备申请中断号

request_irq(fpga_priv.irq, fpga_interrupt,IRQF_SHARED,"FPGA",& fpga_priv);

……

}

2.2 DMA驱动程序

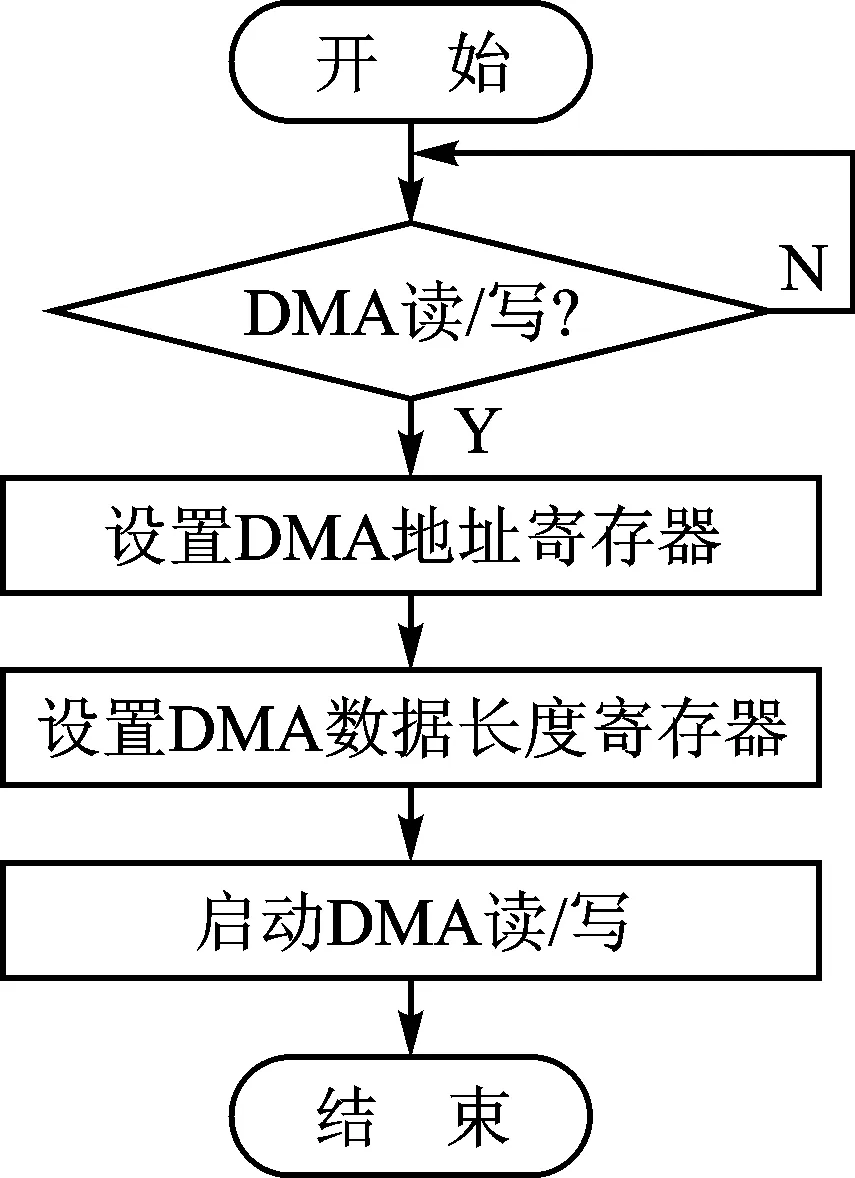

图5 DMA操作流程

DMA(Direct Memory Access,直接内存访问)不需要处理器的干预,处理器只需将读/写数据首地址和数据长度告诉DMA控制器,启动DMA读/写即可[2]。本设计在FPGA内部设置了DMA读写寄存器和DMA地址寄存器,其操作过程如图5所示。

DMA程序实现如下[3]:

int DMA_operation (int len, int i){

int val;

PCIe_InitiatorReset();

//对FPGA软复位

TLP_cnt = (len%TLP_SIZE) ? (len/TLP_SIZE+1) : len/TLP_SIZE;

TLP_cnt += 1;

//计算PCIe传输TLP包大小

PCIe_WriteReg(DMA_LEN_REG, len);

//设置DMA数据长度,地址为默认地址

PCIe_WriteReg(RDMATLPC, TLP_cnt);

//设置TLP传输包数

PCIe_WriteReg(BUFCONTROL1, 0x101);

//使能DMA读/写操作

PCIe_WriteReg(DMACR, 0x10000);

do {

val = PCIe_ReadReg(BUFSTATE1);

} while(val==0x0);

//等待DMA完成

PCIe_WriteReg(BUFCONTROL1, 0);

//disable读/写操作

return 0;

}

2.3 FPGA中断状态机设计

PCIe可以发出两种中断,一种是虚拟INTx信号线的,另一种是MSI的。过去PCI板卡发送中断通过拉低INTx(INTA#、INTB#、INTC#、INTD#)来申请中断,PC检测到INTx的中断,就跳转执行INTx对应的中断驱动程序。MSI是基于消息机制的,PC启动后为PCIe板卡分配一个或多个消息地址,板卡发送中断只需要向对应的地址内发送消息,消息内容中包含消息号,每个消息号对应在PC 端的某一地址。需要注意的是,Windows XP是不支持MSI的,到了WinNT和Win7才支持,因此本方案采取INTx传统中断方式。

中断程序采用状态机控制,正常情况下处于等待状态,当用户应用程序提交中断申请时,将request信号传递给状态机,触发中断;当PC收到PCIe中断时,必须在中断服务程序给FPGA一个确认信号,并在读/写完成之后清除该确认信号,以便FPGA可以进入下一次中断请求。

用户中断请求信号intr_req,当读/写完成时,提交中断请求,如下:

assign intr_req = ((rd_done=1'b1) || (wr_done==1'b1)) ? 1'b1 : 1'b0;

intr_req信号传递到中断程序状态机,如下:

always @(posedge clk ) begin

case (crypt_intr_state)/*状态机状态*/

`BMD_INTR_CRYPT_RST : begin

if(intr_req )//用户应用的中断请求

next_crypt_intr_state = `BMD_INTR_CRYPT_ACT0;

end

`BMD_INTR_CRYPT_ACT0 : begin

……

end

`BMD_INTR_CRYPT_ACT1 : begin

if (cfg_interrupt_ack)//等待PC确认收到中断请求

next_crypt_intr_state = `BMD_INTR_CRYPT_ACT2;

end

`BMD_INTR_CRYPT_ACT2 : begin

……

end

`BMD_INTR_CRYPT_DUN : begin

//等待PC清除确认标志,否则不能进入下一中断

if((!cfg_interrupt_ack)||(timeout_cnt == TIMEOUT))

next_crypt_intr_state = `BMD_INTR_CRYPT_RST;

end

default:

next_crypt_intr_state = `BMD_INTR_CRYPT_RST;

endcase

end

整个状态机操作如下:

① 在BMD_INTR_CRYPT_ACT0状态下,用户应用将cfg_interrupt_n和cfg_interrupt_assert_n置为有效,从而将中断置为有效。

② 然后,核将cfg_interrupt_rdy_n置为有效,表示已接受中断请求。在BMD_INTR_CRYPT_ACT1状态,用户应用将cfg_interrupt_n置为无效;此时如果PCI命令寄存器中的中断禁用位设置为 0,则核发出将中断置为有效的消息。

③ 在BMD_INTR_CRYPT_ACT2状态,用户应用一旦确定中断请求已被接收,就会将cfg_interrupt_n置为有效,同时将 cfg_interrupt_assert_n置为无效,从而将中断置为无效。必须通过 cfg_interrupt_di[7:0]来指示相应的中断。

④ 核将cfg_interrupt_rdy_n置为有效,表示已接收中断的无效置位。在BMD_INTR_CRYPT_DUN,用户应用将cfg_interrupt_n置为无效,而核发出将中断置为无效的消息。

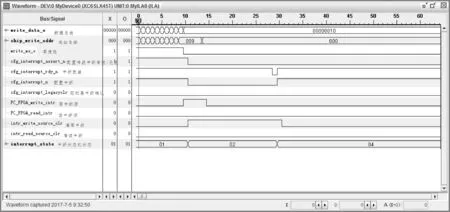

以一次数据写为例,其信号时序仿真如图6所示。

图6 传统中断时序图

通过对IP Core的中断配置接口操作,PC就会接到相关中断信息,使主机进入中断服务程序进行处理。本设计采用状态机的方式产生中断信号,在FPGA内部设计中断寄存器,正常情况下FPGA中断处于等待状态,当FPGA处理完数据后将中断寄存器置位,要求PC去读数据,此时状态机处于中断程序状态,当PC接收到中断并进入到中断服务程序时,清除该中断寄存器,状态机再次恢复到等待状态,可以进行下一次中断。

3 实验测试

实验主机为DELL台式机,CPU为奔腾D处理器,主频2.80 GHz,内存2 GB,操作系统为Ubuntu9.10,内核版本2.6.31。

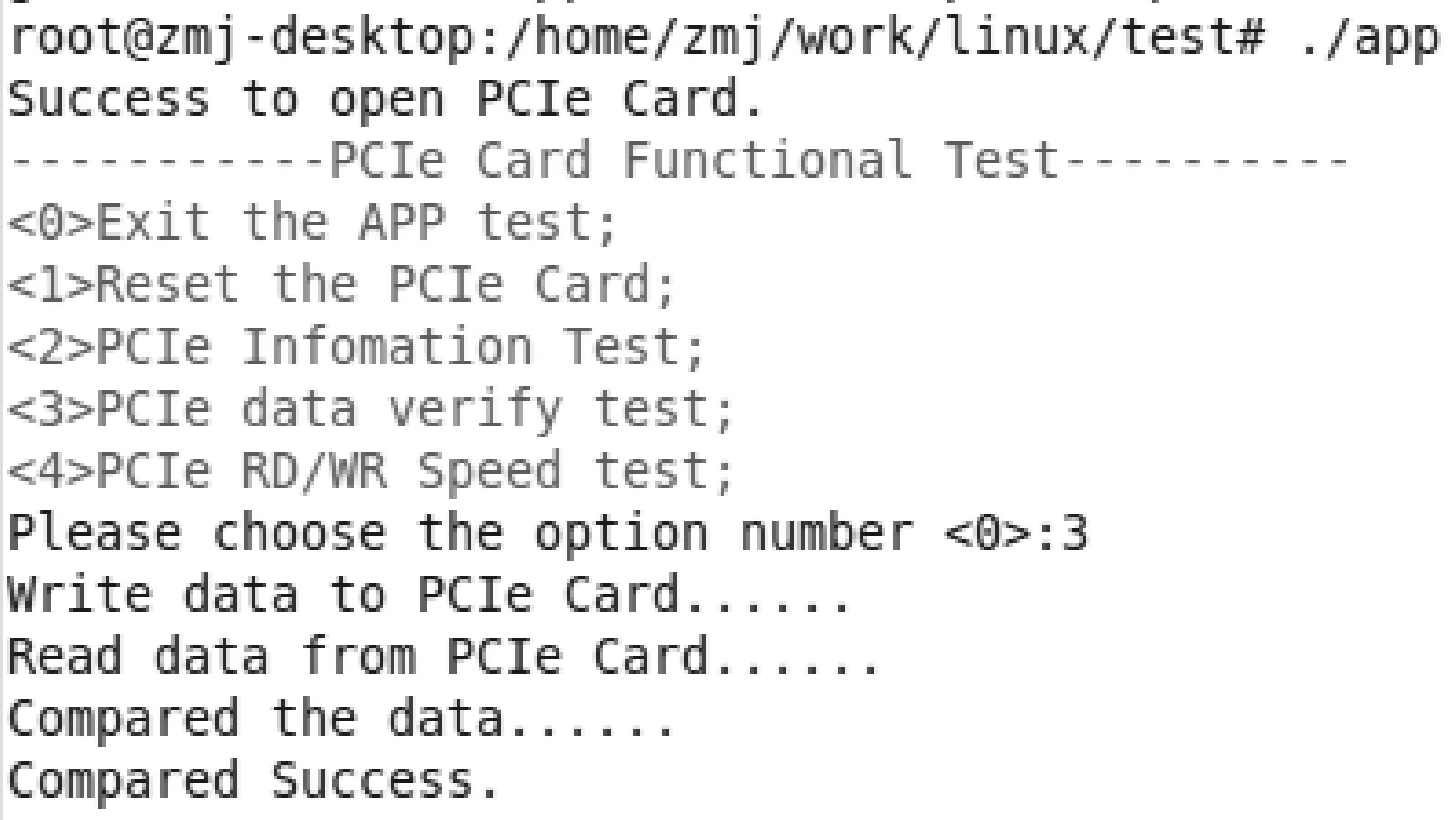

测试方法1如下:

将PCIe卡插到台式机主板插槽,在Linux下加载PCIe卡驱动程序;系统产生2048字节随机数,向PCIe卡中写入随机数,卡接收到随机数并缓存到FPGA的双口RAM中进行存储;从PCIe卡的双口RAM读数据,数据长度与写入保持一致;将读出数据与写入数据进行比对,若一致,则读写正确,否则错误。

数据正确性验证测试如图7所示。

图7 数据正确性验证测试

测试方法2如下:

将PCIe卡插到台式机主板插槽,在Linux下加载PCIe卡驱动程序;系统产生2 048字节随机数;系统计时,向PCIe卡中写入随机数,卡接收到随机数并缓存到FPGA的双口RAM中进行存储;从PCIe卡的双口RAM读数据,数据长度与写入保持一致;循环上两步10万次,待结束计算所用时间;根据时间与所写数据量,计算PCIe卡读写速度。

PCIe卡传输速度测试如图8所示。由于传输速度测试采用双向先写后读方式,因此实际单向读或写的速度应为实测速度的两倍左右,远大于400 Mbps。

结 语

[1] 李木国,黄影,刘于之.基于FPGA的PCIe总线接口的DMA传输设计[J].计算机测量与控制,2013,21(1):233-235.

[2] 王晓庆,周晓波,赵强.PCIE高速数据采集系统的驱动及上位机软件开发[J].计算机应用与软件,2013(9):331-333.

[3] 李晃,巩峰,陈彦化.基于PCIE驱动程序的数据传输卡DMA传输[J].电子科技,2014,27(1):117-120.

朱孟江、王元强、聂云杰、洪昊,主要研究方向为电力系统信息安全设计开发。

DesignofPCIeDataCardBasedonXC6SLX45TPlatform

ZhuMengjiang,WangYuanqiang,NieYunjie,HongHao

(NARI Group Corporation,Nanjing 211100,China)

To improve the transmission rate and the flexibility of data processing,a design method of PCIe data card based on FPGA is proposed in the paper.The scheme adopts the way of IP core on Xilinx XC6SLX45T platform.The card transmission mode uses the DMA mode,which can enhance the transmission speed,which is as high as 400 Mbps.

FPGA;IP Core;PCIe;DMA

TP336

A

2017-08-07)

图8 PCIe卡传输速度测试