基于FPGA和DDS技术的多通道信号源设计∗

杨建华

基于FPGA和DDS技术的多通道信号源设计∗

杨建华

(西安工业大学电子信息工程学院西安710032)

为了解决普通信号源频率分辨率低、频率准确度低、开发更新周期长、信号通道少的问题,文中设计并实现了一种以FPGA、高速D/A和低通滤波为核心,基于DDS技术的多功能多通道信号源。在FPGA中设计了PCI接口控制器、同步时钟控制模块、SRAM控制器、DDS模块等。系统测试结果表明该系统硬件电路简单可靠,能够产生幅度和频率可调的正弦波、方波、三角波、锯齿波和任意波形信号,频率分辨率可达0.01Hz,频率准确度小于等于±0.1%。

直接数字频率合成(DDS);FPGA;信号源;相位累加器

Class NumberTP273

1引言

在科研及教学领域的通信系统、自动化系统以及各种电子测量系统中,常常需要一个频率精度和稳定度高,而且需要用到多种不同频率和相位的信号进行系统测试或者数据分析。传统的波形发生器都是由模拟的电路实现,受到硬件电路的限制,不仅产生的波形少,精度低,而且体积大,灵活性差。直接数字频率合成(Digital Frequeney Synthe⁃sis,DDS)是一种继直接频率合成法和间接频率合成法之后,随着电子技术的发展迅速崛起的第三代频率合成技术[1~2]。随着数字集成电路和微电子技术的发展,DDS技术日益显出它的优越性。DDS技术具有频率分辨率高、频率切换速度快、频率切换时相位连续等优点[3~5]。目前,市场上已出现许多DDS专用芯片,但是专用芯片有很多局限性,比如控制方式固定,同时只能输出一路信号,而且价格普遍偏高[6~7]。利用FPGA的高速、高性能和可重构性,将其作为核心控制单元可平衡系统的性能与成本。美国佛罗里达国际大学在其设计的通用型多通道信号发生器中,采用单个Xilinx Virtex IIFPGA开发板作为系统核心控制器[8],Roy Taniza等在设计雷达系统的信号模拟器时,使用了单块Xilinx高密度FPGA实现了纯数字式DDS[9]采用FPGA以及其它处理器是设计信号源实现高速性、可靠性和高集成度的重要手段。本文基于DDS基本原理,设计了基于FPGA的信号源硬件平台,在QuartusⅡ上完成了信号发生器的逻辑设计、综合及仿真,最终在硬件平台上调试验证,实验测试结果达到设计要求。

2 DDS原理分析

DDS电路一般由参考时钟、相位累加器、波形存储器、D/A转换器(DAC)和低通滤波器(LPF)等组成。

DDS的核心是N位的相位累加器。在时钟脉冲控制下,相位累加器不断对频率控制字K进行累加,将累加器的输出作为读波形存储器ROM的地址,读出波形数据,然后再进行调幅、数模转换、滤波从而得到光滑的波形信号。对于正弦信号发生器,它的输出可以用下式来描述,方波、三角波和锯齿波原理相似。

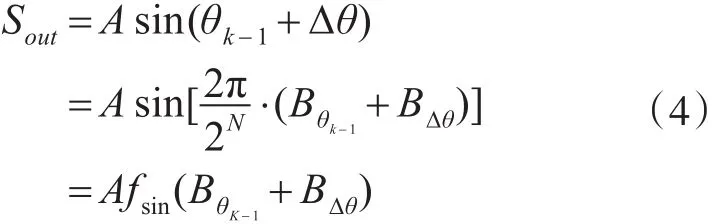

其中Sout是指该信号发生器的输出信号波形,fout指输出信号对应的频率。离散化处理后可得在一个clk周期Tclk,相位θ的变化量为

为了对Δθ进行数字量化,把2π切割成2N,由此每个clk周期的相位增量Δθ用量化值BΔθ来表述:,且BΔθ为整数。与式(2)联立,可得:

显然,信号发生器的输出可描述为

其中θk-1指前一个clk周期的相位值,同样得出:

3基于FPGA的信号源系统设计

3.1系统总体结构设计

整个系统采用PC机和FPGA来设计实现,系统总体结构框图如图1所示。通用PC机主要完成信号源工作模式选择、控制参数设置、信号数据的生成及下载、状态检测等功能,为用户提供友好的操作平台。FPGA作为信号源主控制器,主要实现数据传输存储、信号模拟输出、接口通讯协议以及同步控制等功能,FPGA与通用计算机之间通过高速PCI总线实现数据通讯。

图1 信号源总体结构框图

在系统中为每个通道设计了两片大容量SRAM作为信号数据存储区,两块SRAM在FPGA的控制下实现交替操作,实现信号的持续性和完整性。

3.2基于FPGA的逻辑模块设计

3.2.1 FPGA控制逻辑整体框架

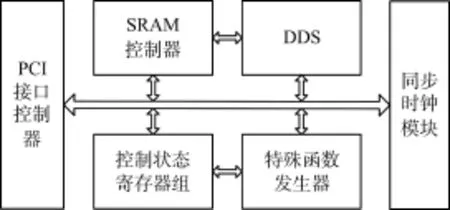

FPGA是系统的核心控制模块,实现系统所有数字逻辑的控制。FPGA控制逻辑的整体结构如图2所示,包括PCI接口控制器、同步时钟控制模块、SRAM控制器、DDS等几个模块。

在130 ℃条件下分别进行带壳、不带壳烘焙10、20、30、40 min,种籽衣总黄酮含量测定结果如图 2所示。与未烘焙种籽衣相比,种籽衣经过不同条件烘焙后总黄酮含量呈现不同程度的损失,其中,带壳焙烘焙种籽衣在20 min总黄酮含量较10 min略微上升后,继续烘焙总黄酮含量又会下降;不带壳烘焙的种籽衣总黄酮含量在10~30 min时间段呈现上升趋势,随后在40 min时降到最低。

图2 信号源FPGA控制逻辑结构框图

主要完成以下主要功能:

1)实现PCI总线向本地总线的转换。

2)实现DDS直接数字频率合成器,通过DDS控制器实现对典型信号和任意信号的生成与参数控制。

3)SRAM控制器实现两个SRAM的相互交替读写操作,保证数据输出的连续性和稳定性。

4)通过控制命令及状态寄存器模块,使得上位PC和FPGA控制器之间的交互控制更加简单可靠。

3.2.2 DDS的FPGA设计实现

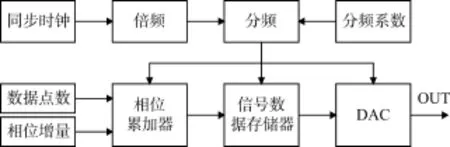

DDS的FPGA实现功能结构如图3所示。

图3 DDS功能结构图

DDS系统时钟由同步时钟分频处理后得到,相位累加器是DDS系统的核心,为了充分发挥其优越性,累加器的位数通常都较大,相位控制字可控制信号的相位及频率输出特性。信号数据存储区是仿真数据的缓冲存储区域,DDS系统通过相位累加器的相位输出来查找数据存储区中的相应数据并将其读出转换;对于用户的自定义信号,因为数据形式和内容的随机性较大,数据的存储缓冲器采用SRAM实现,用户可通过更新SRAM的数据内容来实现对不同目标信号的模拟仿真;对于常用的正弦、方波等信号,设计中将其数据固化在FPGA内部,在FPGA配置完毕后自动加载,用户只需通过上位机进行类型选择和参数设定就可实现典型信号的模拟输出。

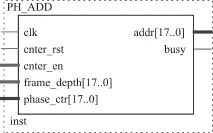

1)相位累加器模块设计

图4 相位累加器模块

图5 相位累加器功能仿真图

2)数据存储输出控制器设计

乒乓机制处理的流程描述如下:输入数据流通过“输入数据流选择单元”,分时地将数据流分配到两个数据缓冲模块。数据缓冲模块采用双口SRAM模块。在第一个缓冲周期,将输入的数据流缓存到数据缓冲模块1中;在第二个缓冲周期,通过“输入数据流选择单元”的切换,将输入的数据流缓存到数据缓冲模块2中,与此同时,将数据缓冲模块1缓存的第一个周期的数据进行预处理,并通过“输出数据流选择单元”的选择,送到“数据流运算处理模块”被运算处理。在第三个缓冲周期,通过“输入数据流选择单元”的切换,将输入的数据流缓存到数据缓冲模块1,与此同时,将数据缓冲模块2缓存的第二个周期的数据预处理,并通过“输出数据流选择单元”的选择,送到“数据流运算处理模块”运算处理,如此不断循环[10]。

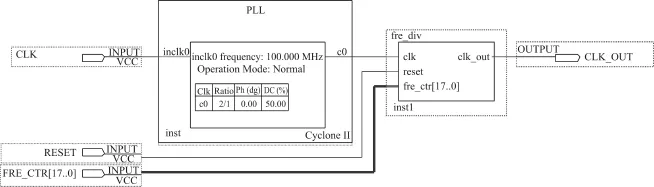

3)同步时钟设计

为保证系统各模块的同步性,系统采用Cy⁃clone II的全局时钟驱动网络。Cyclone II系列PLL具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,可进行系统级的时钟管理和偏移控制。采用PLL可实现更高的内部时钟频率,通过全局时钟网络可使时钟延迟和时钟偏移最小,减小或调整时钟到输出(TCO)和建立(TSU)时间。信号模拟输出的同步时钟结构如图6所示,主要包括PLL锁相环模块、时钟分频模块。设计中时钟信号由专用的时钟引脚CLK[0]输入,然后经过PLL锁相环实现锁相倍频。为了弥补传统DDS由频率控制字累加而引起的精度损耗,这里同时设计了时钟频率控制模块,用户可通过设定时钟频率控制模块的参数来实现对输出信号频率特性的调整。

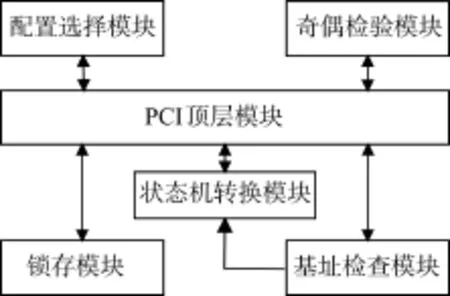

4)PCI通信接口控制器IP核的设计

PCI接口IP核的设计采用了自顶向下的设计方法,按照功能需求将其划分为不同的子模块,主要包括顶层模块、配置选择模块、锁存模块、状态机控制模块和基址检查模块等,其中顶层模块是各子模块的互连接口,同时定义了整个IP核的外围信号。PCI接口IP核的总体功能结构如图7所示。

图6 FPGA控制模块功能结构

图7 PCI接口IP核总体功能结构图

4性能测试

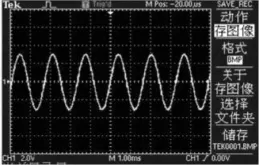

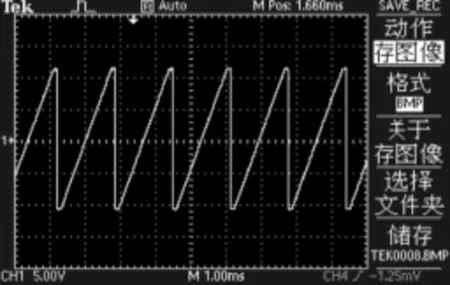

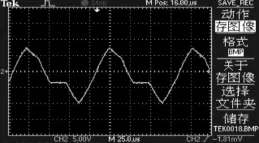

根据系统要求,FPGA为主控制器,与外部SRAM和DAC转换电路直接连接,实现数据存储和输出的时序控制;FPGA同时实现PCI接口控制器,通过其内部PCI接口IP软核实现与控制计算机的命令和数据交换,完成用户对信号模式和参数的控制。系统在FPGA内部设计生成了正弦、方波、三角和锯齿波四种典型信号,任意波形信号数据由用户生成,通过通信端口下载到外部缓冲存储去,适用于实验数据分析。这里给出几种信号波形(正弦波(A=±3.2V,f=625Hz),锯齿波(A=±11V,f= 660Hz),任意信号波形的测试结果,如图8~图10所示。

图8 正弦波测试结果

图9 锯齿波测试结果

图10 任意信号测试结果

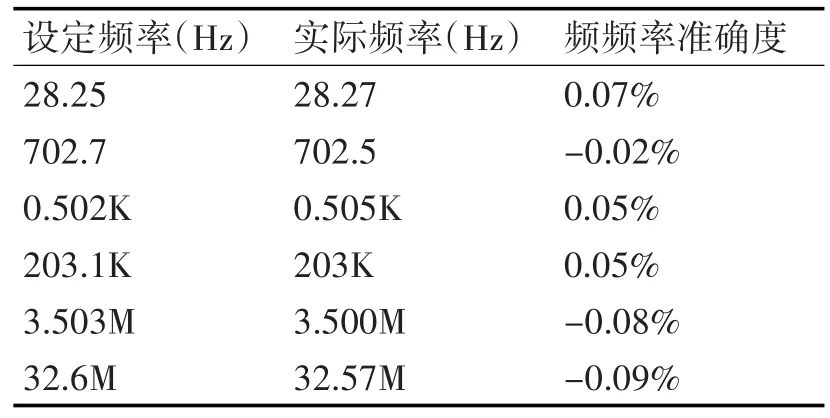

实验测试表明该系统输出40MHz正弦信号时仍能保持比较好的波形形状,而最低输出频率能达到0.01Hz;输出10MHz三角波频率仍能维持良好的形状,对于方波,输出频率到1MHz时出现了明显的过冲现象。依据频率准确度计算公式计算数据如表1所示,通过分析可以看出系统的频率准确度≤±0.1%。

表1 频率准确度

从测试结果可以看出,系统能够灵活模拟常用的典型信号和用户定义的任意信号,且信号频率和幅值均可通过用户设置实现快捷调节,满足设计要求。

5结语

本目前市场上采用专用DDS芯片开发的信号源比较多,它们输出频率高、波形好、功能也较多,但采用FPGA设计的DDS信号源与之相比较,具有如下优势,基于FPGA的DDS信号源可以在一片FPGA芯片上实现信号源的信号产生和控制,并且只要改变存储波形信息ROM数据,就可以灵活地实现任意波形发生器。本设计是基于DDS技术,采用FPGA器件设计并实现的信号源,能够产生幅度和频率可调的正弦波、方波、三角波和锯齿波,频率范围在0.01Hz~40MHz,频率分辨率达0.01Hz,频率准确度≤±0.1%。易实现控制,并且整个系统可由一片FPGA芯片外加键盘、LCD、DAC和LPF完成,因而电路简单,性能稳定。

[1]王丹,李平,文玉梅,等.采用DDS频率合成的虚拟信号发生器研究[J].传感技术学报,2007,20(3):586-591.

WANG Dan,LIPing,WEN Yumei,etal.Research on Vir⁃tual Signal Generator Based on DDS Frequency Synthesiz⁃er[J].Chinese Journal of Sensors and Actuators,2007,20(3):586-591.

[2]孙群,宋卿.基于DDS技术的便携式波形信号发生器[J].仪表技术与传感器,2009(4):69-70.

SUN Qun,SONG Qing.Portable Signal Generator Based on DirectDigital Synthesis[J].Instrument Technique and Sensor,2009(4):69-70.

[3]Kent Gary W,Sheng Neng-Haung.A High Purity,High⁃Speed Direct Frequency Synthesizer[C]//IEEE Interna⁃tionalFrequency Control Symposium,1995:207-211.

[4]刘晨,王森章.直接数字频率合成器的设计及FPGA实现[J].微电子与计算机,2004,21(5):63-65.

LIU Chen,WANG Senzhang.Design of DDS and Imple⁃mentation with FPGA[J].Microelectronics and Computer,2004,21(5):63-65.

[5]高书亮,黄智刚,杨东凯.基于DDS的BOC(m,n)信号发生器及其FPGA实现[J].数据采集与处理,2009,24(2):243-247.

GAO Shuliang,HUANG Zhigang,YANG Dongkai.BOC(m,n)Signal Generator Based on DDS and Its FPGA Im⁃plementation[J].Journal of Data Acquisition&Process⁃ing,2009,24(2):243-247.

[6]高琴,姜寿山,魏忠义.基于FPGA的DDS信号源设计与实现[J].西安工程科技学院学报,2006,20(2):210-214.

GAO Qin,JIANG Shoushan,WEIZhongyi.Design and re⁃alization of signal generator with DDS based on FPGA[J]. Journal of Xi'an University of Engineering Science and Technology,2006,20(2):210-214.

[7]曾云,韩顺锋.基于FPGA的DDS信号源设计及误差分析[J].舰船电子工程,2009,29(2):72-74.

ZENG Yun,HAN Shunfeng.Design and Error Analysis of DDS Signal Generator Based on FPGA[J].Ship Electron⁃ic Engineering,2009,29(2):72-74.

[8]Yao J F,Wunnava S V.General Purpose Multi-Channel Signal Generator Based on Xilinx Virtex II Pro FPGAs[C]//International Conference on Asic,2007:98-101.

[9]Taniz a R,Jadia K.High Density FPGA Based Waveform Generation for Radars[M].IEEE Press,2010.

[10]F.Cardells,J.Valls.Optimization of Direct Digital Fre⁃quency Synthesizer Based on CORDIC[J].IEEE Elec⁃tronics Letters,2001,37(21):1278-1280.

A Multichannel SignalGenerator Based on DDS and FPGA

YANG Jianhua

(Schoolof Electronic Information Engineering,Xi'an TechnologicalUniversity,Xi'an 710032)

In order to solve the problem of the low frequency resolution,low frequency accuracy,the long cycle of develop⁃mentand update and the less signalchannel,a multi-function and multi-channelsignalgenerator which is based on DDS technolo⁃gy with FPGA,high-speed D/A and a low-pass filter as the core is designed and implemented.In the FPGA,the PCIinterface con⁃troller,synchronous clock controlmodule,SRAM controller and DDS module etc are designed.The experimentresults show thatthe system is simple and reliable and can generate sine wave,square wave,triangular wave,saw tooth wave and arbitrary waveform sig⁃nal.The frequency resolution comes up to 0.01Hz and frequency accuracy is equalor lesser than±0.1%.

directdigitalsynthesis,FPGA,signalsource,phase accumulator

TP273

10.3969/j.issn.1672-9722.2017.08.042

2017年2月5日,

2017年3月20日

国家自然科学基金:深海空间站回转型穿梭器网络化控制性能分析与优化(编号:61473224);陕西省教育厅专项科研计划项目(编号:16JK1372)资助。

杨建华,男,博士研究生,讲师,研究方向:控制理论与控制工程,电子技术应用。