基于40 nm CMOS工艺的低杂散低噪声亚采样锁相环设计

曾 铭,王宇涛,林福江

(中国科学技术大学,信息科学技术学院,安徽 合肥 230026)

基于40 nm CMOS工艺的低杂散低噪声亚采样锁相环设计

曾 铭,王宇涛,林福江

(中国科学技术大学,信息科学技术学院,安徽 合肥 230026)

基于SMIC 40 nm CMOS工艺,设计了一款应用于2.4 GHz的高性能低杂散低噪声亚采样锁相环(SSPLL)。压控振荡器(VCO)的输出直接被参考时钟信号采样,实现了核心环路无分频器。使用互补开关对和Dummy采样器消除了BFSK效应,减少了参考杂散。同时,通过自偏置缓冲器的隔离作用进一步减少了杂散。可调死区产生电路加速了锁定建立过程。后仿结果表明,该SSPPL在1.1 V的电源电压下核心电路功耗为5.84 mW,在50 MHz的频偏处参考杂散为-84.56 dBc,带内相位噪声为-125 dBc/Hz@1 MHz。

亚采样;参考杂散;锁相环;BFSK效应;低杂散

0 引言

随着无线通信技术的迅速发展以及消费电子的盛行,对集成电路的需求日趋增加。一个稳定的高纯度的低杂散、低噪声时钟信号在许多应用中都是必不可少的,例如高速数据通信串并行转换、计算机各种钟频信号的供给、无线通信系统中上变频和下变频等。较差的杂散和相位噪声会导致相邻通道信号的频谱混叠,降低信噪比[1]。传统的电荷泵锁相环(Charge-Pump Phase-locked Loop,CPPLL)中,在带宽确定的情况下,参考杂散主要来自电荷泵充放电电流的失配[2]。降低参考杂散的传统方法有两种,一是选取较小的环路带宽,这可以抑制控制电压线的纹波,从而减少杂散,但这会增加环路滤波器的面积,不利于片上集成。二是采用Cascode结构的电荷泵,但是这种结构的电荷泵电流匹配范围较小,而且不利于低电源电压设计。亚采样锁相环(Sub-Sampling Phase-locked Loop,SSPLL)[2]电路结构消除了传统电荷泵锁相环中鉴频鉴相器延迟失配和电荷泵电流失配引起的杂散,同时,由于核心环路中没有分频器的存在,带内噪声极大降低,可以同时实现大带宽和低杂散、低相位噪声。

1 传统电荷泵锁相环杂散机理分析

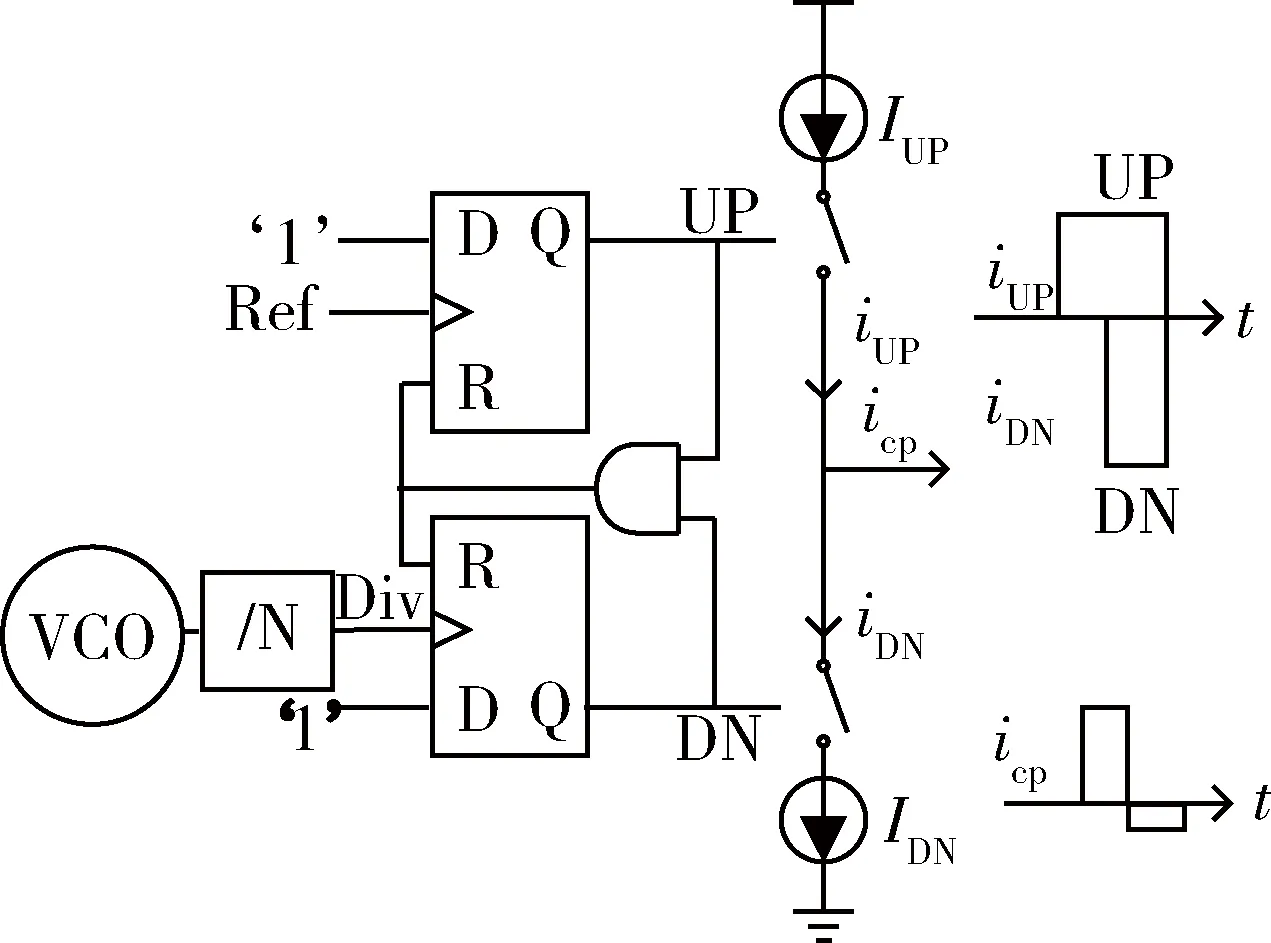

传统电荷泵锁相环的参考杂散主要来源于鉴频鉴相器(Phase Frequency Detector,PFD)以及电荷泵(Charge Pump,CP)的失配,包括CP的静态电流失配、上下开关管导通时间失配、开关信号UP和DN的延时失配等。如图1所示,这些失配会导致CP的输出电流产生失配,该电流注入到环路滤波器并转换成控制电压的纹波,导致锁相环的输出产生较大的杂散。该电压纹波的周期与参考信号的周期相同。

图1 传统电荷泵杂散原理结构图

假设CP输出电流纹波的基波幅度是iCP,fref,相应于VCO输出信号的参考杂散SPfref,CP可以表示为:

(1)

其中,FLPF(s)是环路滤波器的跨阻传输函数,KVCO是VCO的调谐增益,fref是参考信号的频率。

对于一个二阶的环路滤波器, 跨阻传输函数表示为:

(2)

其中,R1、C1、C2是二阶环路滤波器的电阻和电容,fzero=1/2πR1C1,fpole=1/(2πR1C1C2/(C1+C2))是环路滤波器的零点频率和极点频率。

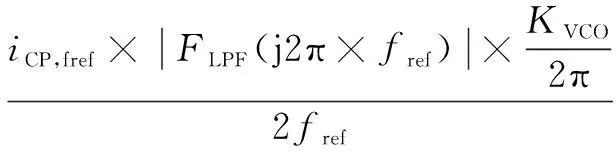

所以,PLL的输出杂散可以近似表示为:

(3)

PLL开环带宽可以表示为:

(4)

所以参考杂散可以表示为:

(5)

由式(5)知,传统的CPPLL为了得到比较好的参考杂散可以牺牲相位裕度以及带宽,但这样会影响系统的稳定性以及增加锁定时间。通过减少电荷泵的电流失配也可以减少参考杂散,但是由于传统的CPPLL的PFD/CP一定存在静态失配,而且这种失配随着工艺的进步会变得更加明显,因为先进工艺的沟道长度调制等效应更加明显,会导致电荷泵CP电流失配增大,参考杂散会进一步恶化。

2 亚采样锁相环杂散机理分析

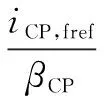

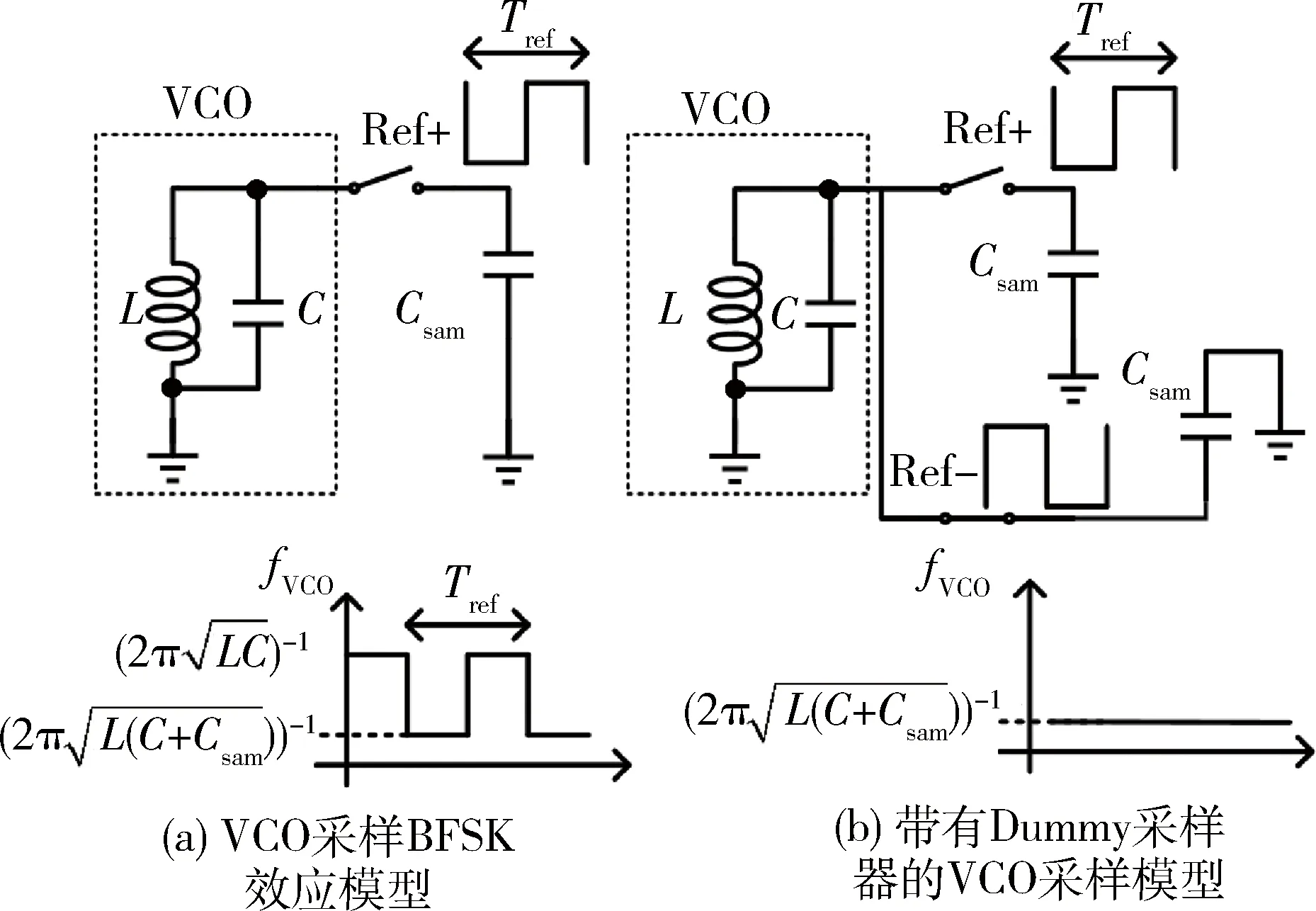

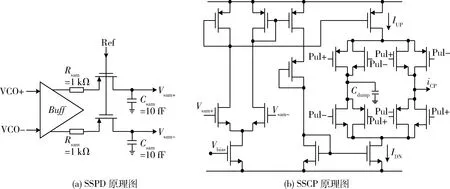

亚采样锁相环可以同时实现大环路带宽和低参考杂散。本文设计的亚采样锁相环SSPLL结构图如图2所示,亚采样锁相环SSPLL包括核心环路(Core Loop)和锁频环路(Frequency-locked Loop,FLL)以及Dummy采样器。核心环路包括亚采样鉴相器(Sub-Sampling Phase Detector,SSPD)、亚采样电荷泵(Sub-Sampling Charge Pump,SSCP)、环路滤波器(Low-Pass-Filter,LPF)、压控振荡器VCO;锁频环路包括鉴频鉴相器、窄死区产生器(Narrow Dead Zone Creator)、电荷泵、分频器(Divider)。

图2 亚采样锁相环结构图

开始工作时,SSPLL的核心环路以及锁频环能都处于开启状态,直到Div和Ref+的相位差小于窄死区产生电路能够鉴别的值,这时锁频环就停止工作。从这之后,核心环路单独工作,开始累积相差,直到Div和Ref+的相位差大于窄死区产生电路能够鉴别的值,锁频环又开始工作。上述过程可能会在锁定行为建立过程中重复出现,直到VCO的输出频率是锁频环电路所要求的整数倍,且VCO输出信号的零交调点与采样信号的下降沿对齐,这个时候SSPLL就处于锁定状态。由于SSPD的捕获范围有限,为了确保环路能够锁定在正确的频率,加入锁频环路。

亚采样锁相环电荷泵的电流是由采样电压幅度决定的,在锁定状态时,流入到环路滤波器中的净电荷为零,SSCP的上下管的导通时间相同,电流也一定相等,所以SSCP不存在静态电流失配。即IUP=IDN,上下电流失配消失,从而消除了因电荷泵电流失配引起的参考杂散。

亚采样锁相环杂散的主要来源是SSPD对VCO的周期性扰动,最显著的就是BFSK效应。

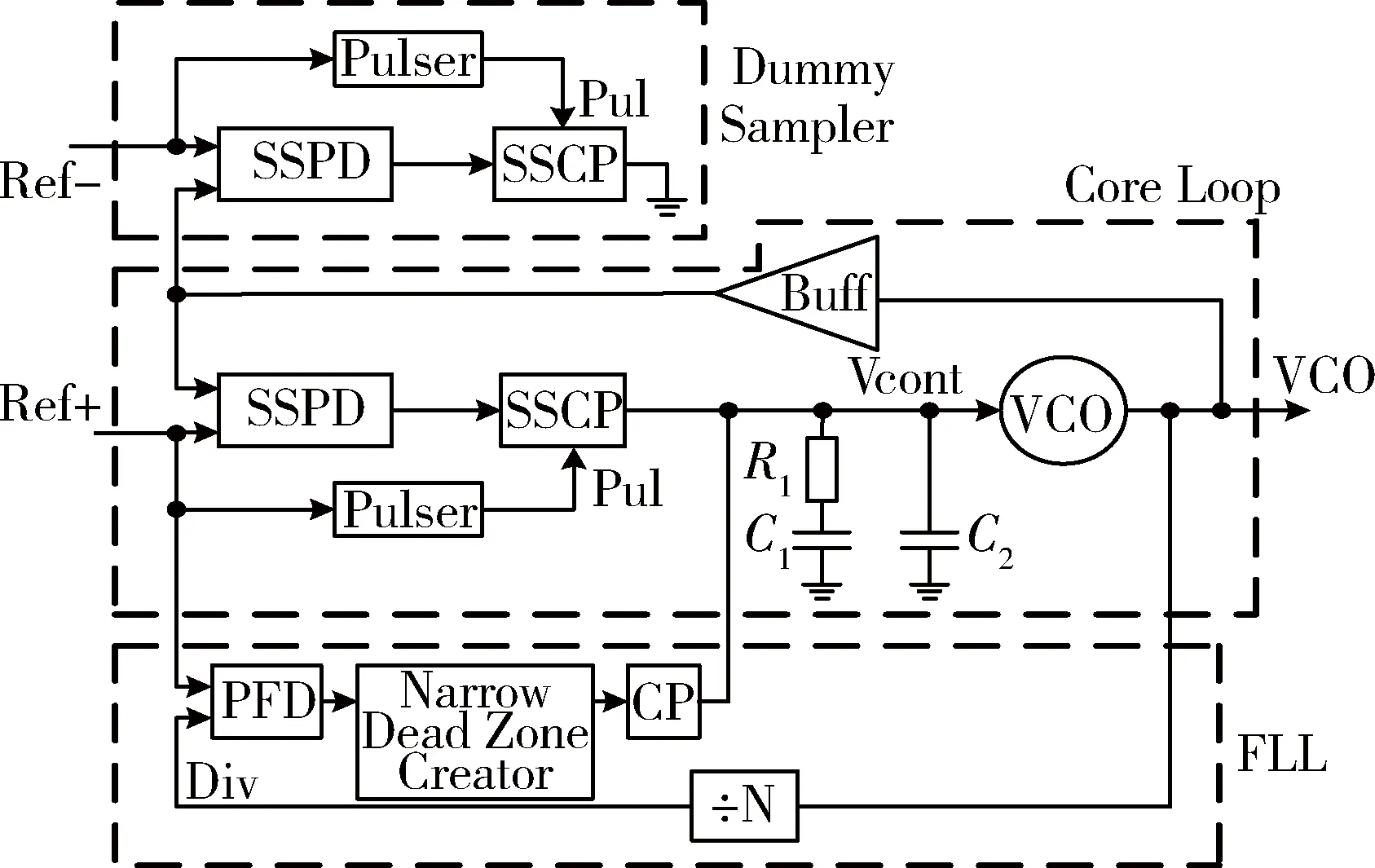

BFSK效应就是SSPD在采样管开启和关断的时候,VCO的负载不相同导致VCO的输出频率发生周期性的变化。这会导致输出频谱不纯,恶化杂散。由于BFSK效应产生的杂散为:

(6)

其中,Mref为参考时钟信号的占空比;Csam为SSPD的采样电容;分频比N=fVCO/fref;Ctank为VCO的LC tank的总电容,包括MOS管的寄生电容。

通过Dummy采样器和互补开关对可以消除BFSK效应,如图3所示,采样管开启和关断的时候,VCO的输出负载始终保持一致。

图3 采样模型

但是由于实际的电路制造过程中采样电容会存在一定的失配,参考杂散可以表示为:

SPfref,BFSK,SSPLL=

(7)

其中,PC为失配系数,此值一般很小。

相同的功耗和带宽情况下,本文提出的亚采样PLL的杂散远远低于传统电荷泵PLL的杂散。

除了BFSK效应,采样器SSPD对VCO的电荷泄露、电荷分享等也会恶化参考杂散,为了消除这些恶化杂散的机理,同时保证VCO的输出波形不失真,以确保SSPD对其能够正确采样,本文采用了自偏置的一级反向器作为缓冲器,隔离VCO和SSPD。

3 亚采样锁相环具体电路实现

3.1 亚采样鉴相器/电荷泵

SSPD/SSCP的电路原理图如图4所示,SSPD用参考时钟Ref+信号直接采样VCO的输出信号,检测VCO输出信号和Ref+信号下降沿的相位误差,转化成电压差(Vsam+-Vsam-),SSCP把电压差转换成电流,注入到环路滤波器中变成VCO的控制电压,改变VCO的输出相位。

图4 SSPD/CP的电路实现

由于亚采样结构中无分频器,环路增益较大,从而使得环路滤波器的面积变大,这将不利于片上集成,而使用脉冲产生器可以产生互补的可调脉冲信号(Pul+,Pul-),该互补信号控制电荷泵上下电流开关的导通时间,从而减少SSPD/CP的增益,减少环路滤波器的电容面积,实现片上集成。SSCP采用互补的开关管抑制了电荷泵的电荷注入、电荷分享等效应。

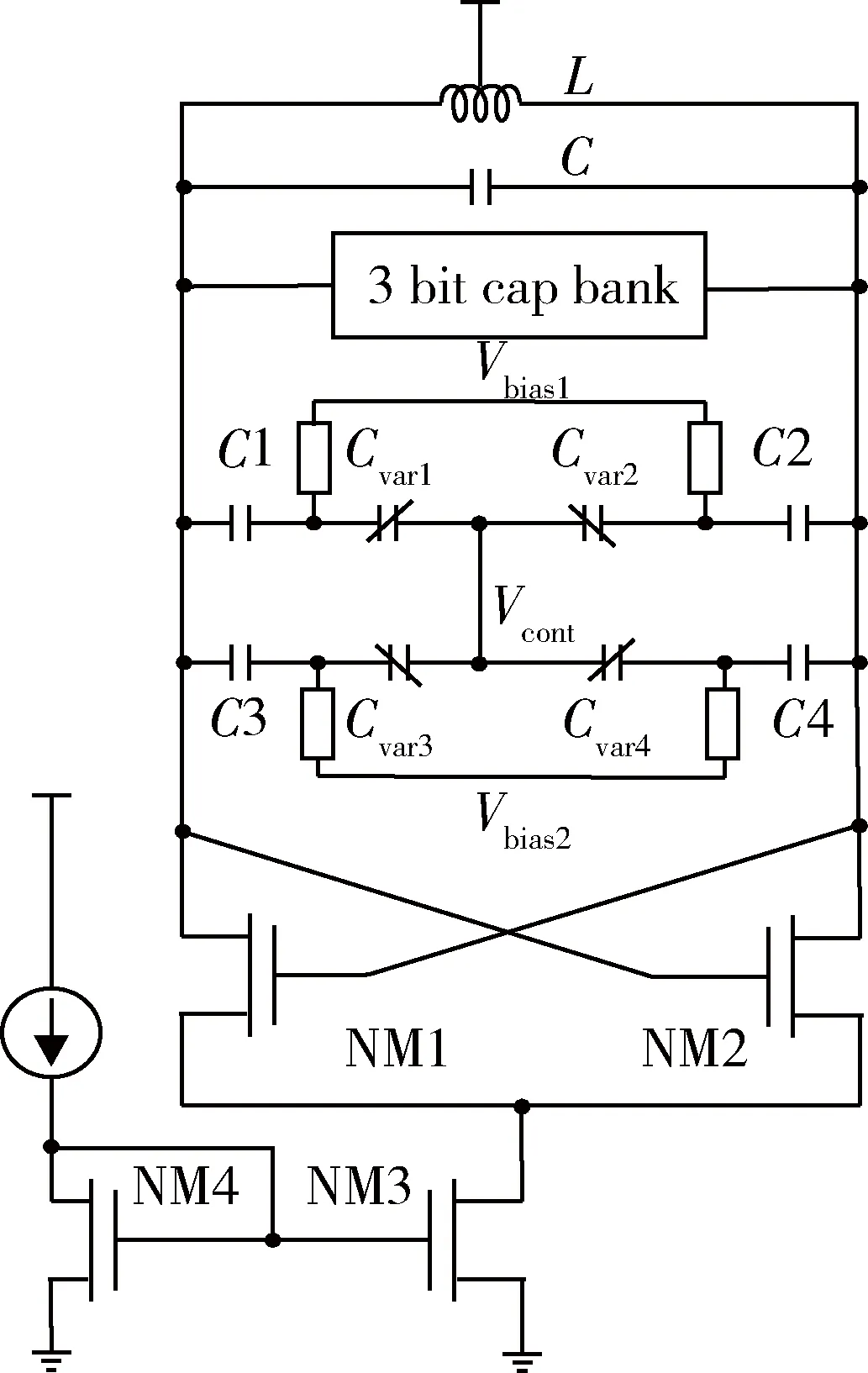

3.2 高线性度压控振荡器

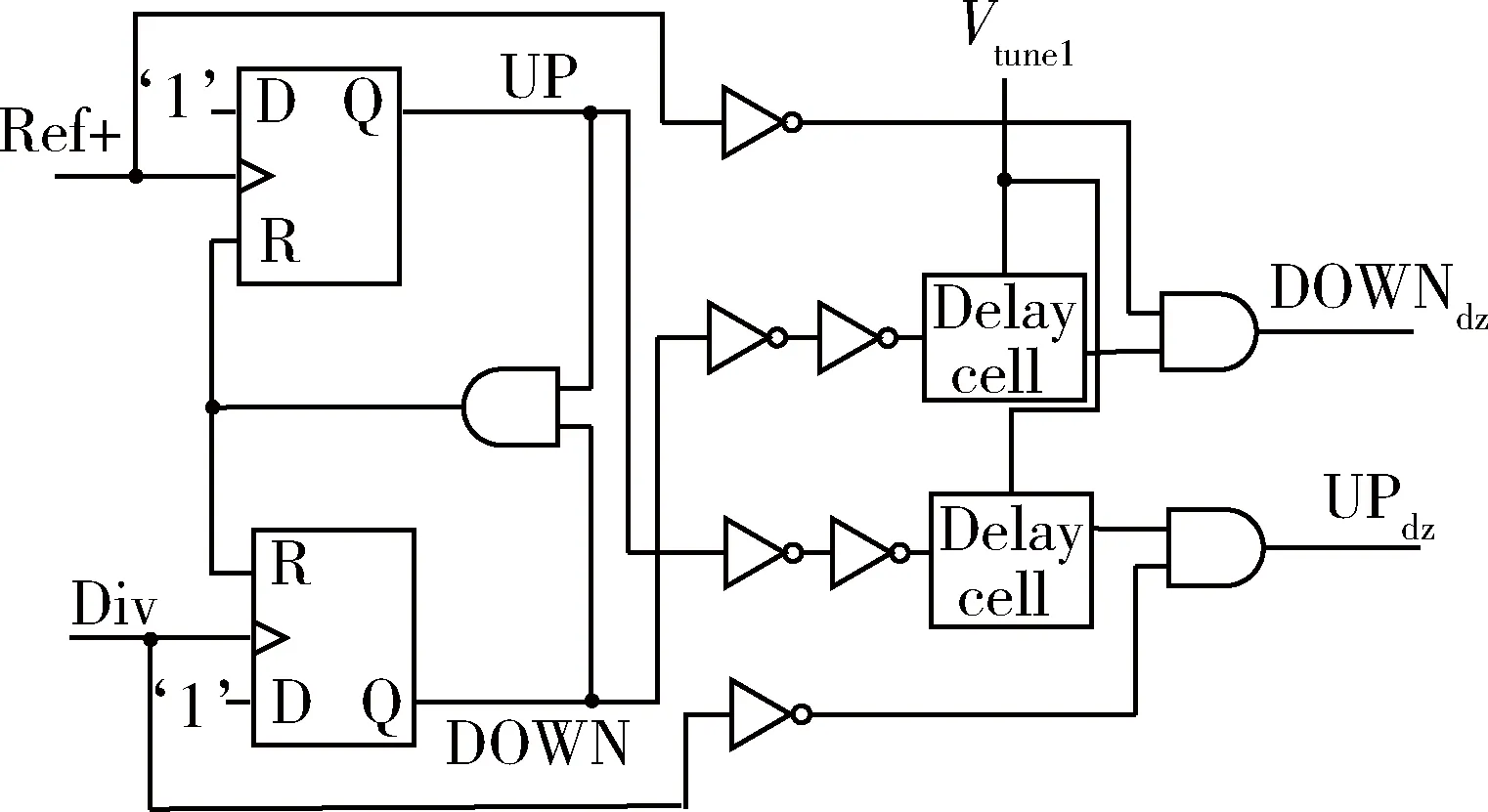

为了获得较低的相位噪声,本文采用电容电感型压控振荡器(LC VCO),如图5所示。该VCO采用分布式变容管以增加调谐线性度[3],采用3 bit的数字位控制的电容阵列用来增加调谐范围,如图6所示,该VCO的调谐范围为2.27 GHz~2.55 GHz,频率调谐增益为72 MHz/V。

图5 高线性度压控振荡器

图6 高线性度VCO调谐曲线

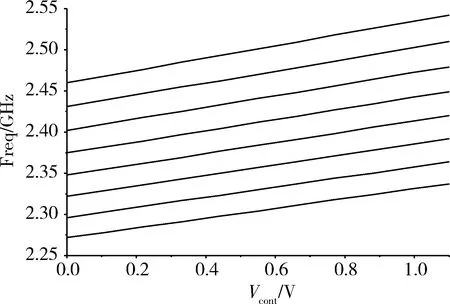

3.3 鉴频鉴相器/可调死区产生电路

为了减少SSPLL锁定建立过程中累积相位的时间,提出了一个带有可调死区产生电路的鉴频鉴相器,如图7所示,Vtune1用来调节延迟单元的充放电电流,从而控制PFD输出信号脉冲宽度,改变死区的大小,通过该电路可以加速锁相环的锁定。

图7 鉴频鉴相器/可调死区产生电路

4 版图设计及仿真结果

本文采用SMIC 40 nm CMOS工艺设计,其中参考晶振频率为50 MHz,电源电压为1.1 V。

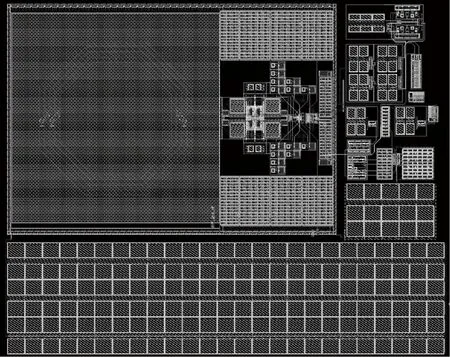

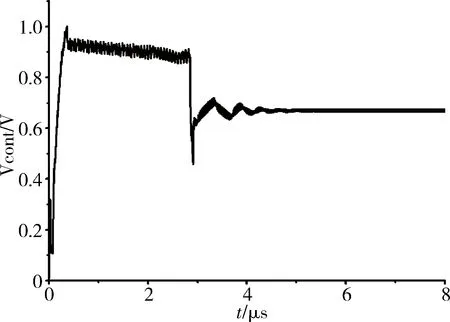

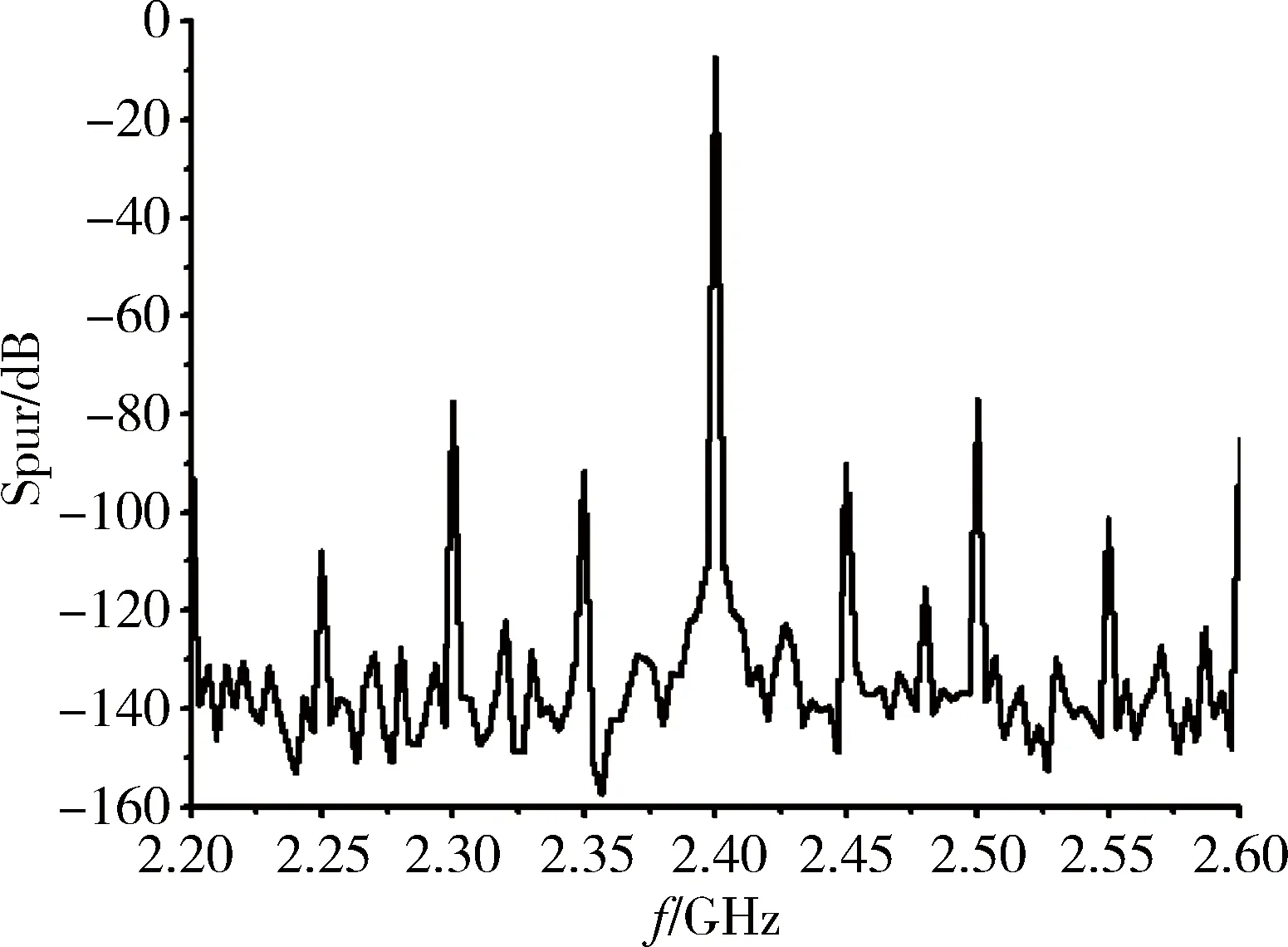

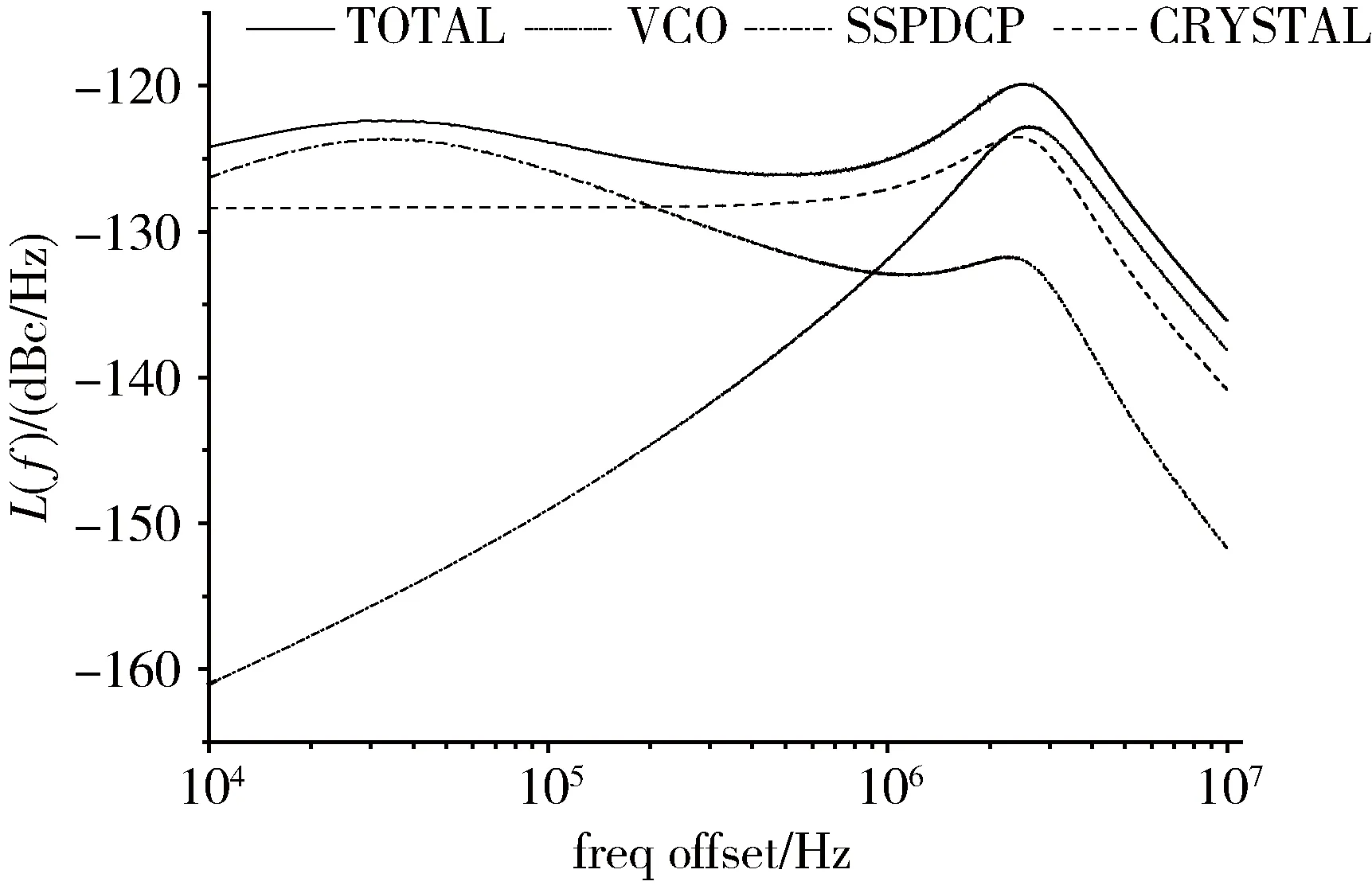

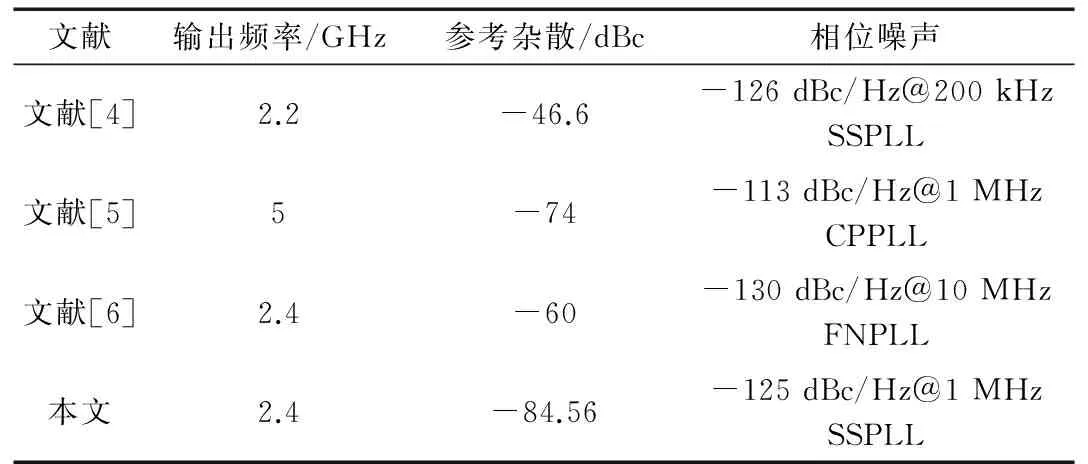

SSPLL整体版图如图8所示。绘制版图后,提取寄生参数进行后仿真,环路锁定行为建立过程如图9所示,环路锁定时间约为5 μs,控制电压锁定值为0.67 V。该亚采样锁相环环路带宽约为2 MHz,图10为本文设计的SSPLL频谱图,输出频率为2.4 GHz,偏离中心频率50 MHz处,参考杂散为-84.56 dBc。图11为环路各部分及整体相位噪仿真图,在1 MHz处的带内噪声为-125 dBc@1 MHz。本文设计的亚采样锁相环与文献[4]、[5]、[6]的锁相环对比如表1所示。

图8 SSPLL整体版图

图9 SPPLL环路控制电压Vcont曲线

图10 SSPLL输出频谱

图11 环路相位噪声仿真

文献输出频率/GHz参考杂散/dBc相位噪声文献[4]2.2-46.6-126dBc/Hz@200kHzSSPLL文献[5]5-74-113dBc/Hz@1MHzCPPLL文献[6]2.4-60-130dBc/Hz@10MHzFNPLL本文2.4-84.56-125dBc/Hz@1MHzSSPLL

5 结论

基于SMIC 40 nm CMOS工艺,本文设计了一个片上集成的SSPLL,分析了传统电荷泵锁相环和亚采样锁相环的杂散机理,提出了减少杂散的解决方法以及减少锁定时间的电路。该亚采样锁相环在1.1 V的电源电压下,功耗为5.84 mW,参考杂散为 -84.56 dBc,带内相位噪声为-125 dBc/Hz@1 MHz。

[1] RAZAVI B, BEHZAD R. RF microelectronics[M]. New Jersey: Prentice Hall, 1998.

[2] GIERKINK S L J. Low-spur, low-phase-noise clock multiplier based on acombination of PLL and recirculating DLL with dual-pulse ring oscillator and self-correcting charge pump[J]. IEEE Journal of Solid-State Circuits, 2008, 43(12): 2967-2976.

[3] Chen Nan, Huang Lu, Wang Chenlun, et al. Low phase noise and linear gain VCO using self-switched biasing[C].2011 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 2011: 137-140.

[4] Gao Xiang, KLUMPERINK E A M, BOHSALI M, et al. A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by[J]. IEEE Journal of Solid-state Circuits, 2009, 44(12): 3253-3263.

[5] Kuo Chunyi, Chang Jungyu, Liu Shenluan. A spur-reduction technique for a 5-GHz frequency synthesizer[J]. IEEE Transactions on Circuits and Systems I: Regular Papers,2006,53(3):526-533.

[6] PARK P, PARK D, CHO S H. A 2.4 GHz fractional-N frequency synthesizer with high-OSR ΔΣ modulator and nested PLL[J]. IEEE Journal of Solid-state Circuits, 2012, 47(10): 2433-2443.

Design of low spur low phase noise sub-sampling PLL based on 40 nm CMOS process

Zeng Ming, Wang Yutao, Lin Fujiang

(School of Information Science and Technology, University of Science and Technology of China, Hefei 230026, China)

This paper presents a 2.4 GHz high performance low spur low phase noise sub-sampling phase-locked loop in SMIC 40 nm CMOS process. The output of VCO is directly sampled by the reference clock signal, and the core loop is realized without divider. The effect of BFSK is eliminated by using complementary switch pairs and dummy sampler, and reference spur is reduced. At the same time, the spur is further reduced by using self-biased isolation buffer. The settling time is reduced by adjustable dead zone creator. The post simulation result showed that the core circuit of SSPLL consumes 5.84 mW at 1.1 V supply voltage, reference spur can be as low as -84.56 dBc at 50 MHz offset, and it exhibits phase noise of -125 dBc/Hz at 1 MHz in band.

sub-sampling; reference spur; phase locked loop; BFSK effect; low spur

TN43

A

10.19358/j.issn.1674- 7720.2017.16.010

曾铭,王宇涛,林福江.基于40 nm CMOS工艺的低杂散低噪声亚采样锁相环设计[J].微型机与应用,2017,36(16):33-36,40.

2017-02-24)

曾铭(1993-),通信作者,男,硕士研究生,主要研究方向:射频集成电路。E-mail:zengm93@mail.ustc.edu.cn。

王宇涛(1993-),男,硕士研究生,主要研究方向:射频集成电路。

林福江(1958-),男,博士,博士生导师,国家“千人计划”,主要研究方向:射频芯片建模、设计。