电表用主控芯片的低功耗设计研究

周芝梅,赵东艳,王艳艳,何旭杰

(1.北京智芯微电子科技有限公司 国家电网公司重点实验室 电力芯片设计分析实验室,北京 100192;2.北京智芯微电子科技有限公司 北京市电力高可靠性集成电路设计工程技术研究中心,北京 100192)

电表用主控芯片的低功耗设计研究

周芝梅1,2,赵东艳1,2,王艳艳1,2,何旭杰1,2

(1.北京智芯微电子科技有限公司 国家电网公司重点实验室 电力芯片设计分析实验室,北京 100192;2.北京智芯微电子科技有限公司 北京市电力高可靠性集成电路设计工程技术研究中心,北京 100192)

智能电表的功能日趋复杂,电表要求能持续现场工作不少于5年,所以对主控芯片的功能和功耗要求都比较高。研究设计了一款新型电表用主控芯片,功能方面集成了RTC模块、LCD驱动及常用的通信接口模块,同时为了达到低功耗指标,设计了三种不同的工作模式满足电表不同应用场景下的低功耗需求。经过实测,在电表的各种工作模式下,本芯片都实现了非常好的功耗性能。

智能电表;低功耗; 微控制单元;工作模式

0 引言

智能电表作为智能电网建设中的重要组成设备,从以往单一电能计量功能,发展为可以实现阶梯电量计费、保存历史用电数据、关键事件告警和支持多种通信模式等复杂功能。同时电表标准要求1 200 mA锂电池,在电能表寿命周期内无需更换,断电后可维持内部时钟正常工作累计不少于5年[1], 所以电表主控的低功耗设计非常重要。

本文垂直优化电表不同应用场景下的工作需求,研制了集高精度实时时钟[2]、温度传感、显示模块、多种通信接口于一体的主控SoC芯片。同时基于动态电源管理技术,芯片的工作模式、工作电压和频率可以随业务模型灵活配置,使芯片的性能和功耗达到最优。

1 系统功能分析

常用的智能电表方案应用框图如图1所示,电表完成的功能主要包括电能计量、数据的安全保护、本地RTC计时以及支持电表的对外通信,包括485通信口、SPI、I2C和红外,还有本地液晶显示、按键触发等功能[3-4]。电表的应用方案中,用到的功能芯片包括: 一颗主控芯片,一颗RTC芯片,一颗安全芯片,一颗EEPROM和一颗计量芯片,主控MCU芯片完成重要的控制、通信等功能。

图1 智能电能表典型应用方案

根据电表的应用需求,电表主控的设计主要关心两个方面,一是主控完成的功能,二是主控的功耗,这两点是芯片设计的关键。

2 主控芯片的功能结构

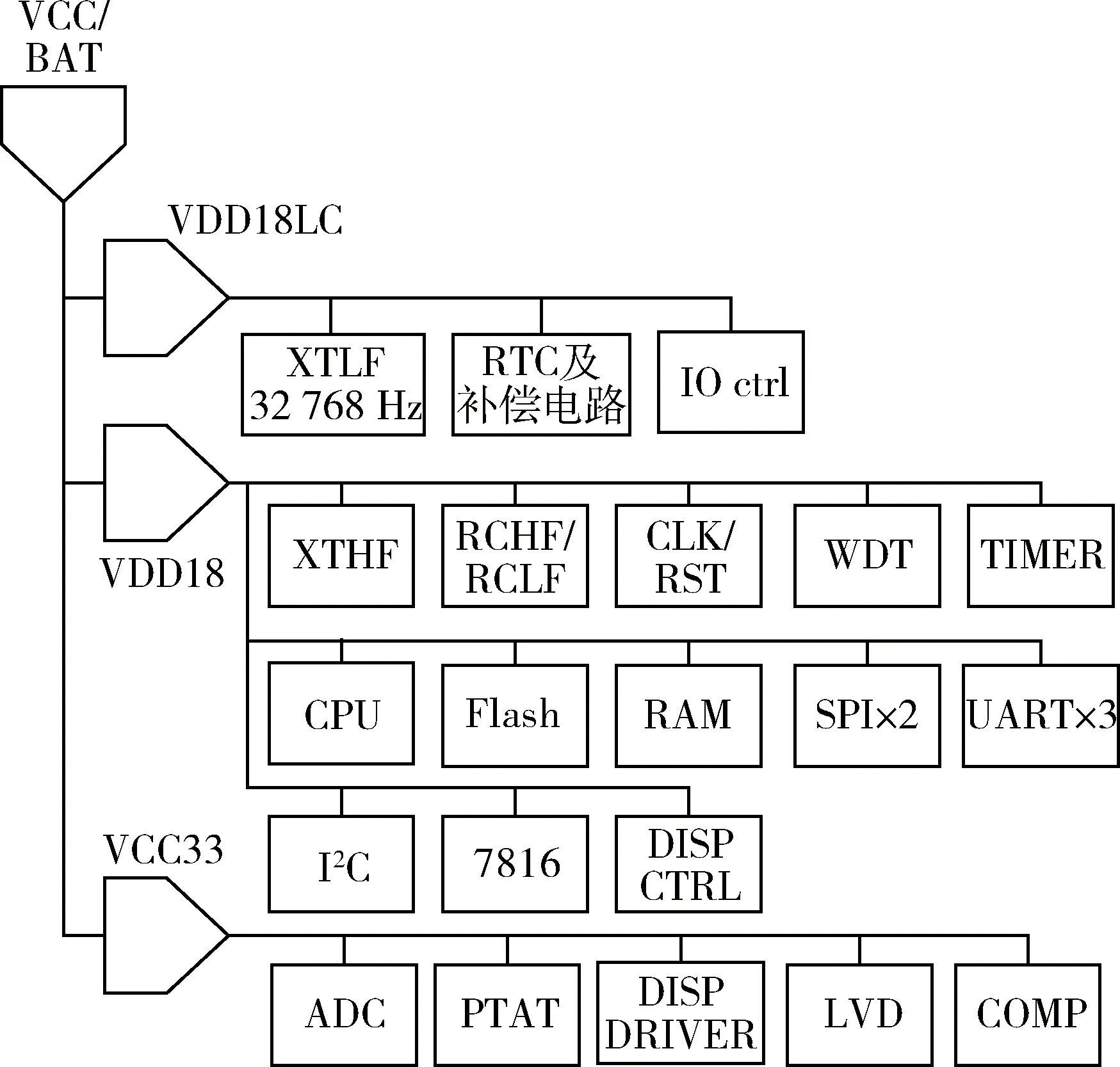

根据电源应用方案的分析,本文设计的电表主控芯片,功能框图如图2所示,芯片CPU采用ARM Cortex-M0[5-6],内置128 KB Flash存储器,32 KB RAM,集成了四通道DMA;三路串口分别负责与485通信、载波模块和红外收发器通信,SPI与计量芯片通信;ISO7816与ESAM安全芯片通信, I2C分别与EEPROM通信;液晶驱动最大支持4×34和6×32的LCD驱动模式;另有4路TIMER、1路看门狗等功能。

图2 电表主控芯片功能框图

芯片架构采用AMBA二级总线结构,一级AHB总线上含两个主设备CPU和DMA,三个从设备分别是SRAM控制器、Flash控制器和APB 桥,总线采用矩阵结构互联,提高数据带宽;二级APB总线挂的是ADC、GPIO、SPI、RTC和串口等外设。

3 芯片的低功耗设计技术

CMOS逻辑电路的功耗可以分为动态功耗和静态功耗两部分。动态功耗是指当芯片处于激活(Active)状态时,也即信号发生跳变时的功耗,静态功耗是指芯片处于未激活状态或者没有信号跳变时的功耗[7]。 动态功耗70%源自开关电容电流功耗[8],开关电容的功耗定义如式(1)所示:

P=0.5*T*C*V2*f

(1)

静态功耗主要是指泄漏电流功耗,在CMOS电路中,有反偏PN结漏电流和亚阈值沟道电流,静态功耗主要取决于不同工艺的器件参数。

3.1 芯片的低功耗模式设计

为了降低芯片工作时的功耗,根据电表的不同应用场景,设计了三个不同的工作模式,以满足电表不同应用场景下的低功耗需求。三种工作模式分别为Active、Sleep和Stop,Active工作模式应用于电表正常工作时,Sleep应用于电表挂装后市电掉电,以电池供电的工作模式,Stop模式适合电表放在库房尚未挂装时的极低功耗模式。这三种工作模式之间的转换如图3所示。

图3 芯片工作模式转换图

这三种工作模式的切换控制在PMU模块里实现,在软件写完相应控制寄存器后,PMU根据控制寄存器的内容,使用硬件状态机完成三种状态之间的切换,主要包括时钟模块的关闭、Isolation控制信号的使能和电源模块的关闭等。三种工作模式的具体工作状态如下:

(1)Active模式

此模式为主控的正常工作模式,在这个模式下, 芯片工作于高频RCHF 32 MHz时钟,也可由软件配置为其分频时钟,CPU时钟打开,周围的功能模块的工作模式由CPU运行软件设置决定。

(2)Sleep模式

在此模式下,大部分功能模块包括CPU的时钟被关闭,PMU、中断处理模块和RTC工作于低频晶振时钟XTLF(32 768 Hz),然后由硬件状态机将高频32 MHz时钟关闭。

Sleep模式下可以支持的唤醒源包括:按键唤醒,比较器唤醒,RTC定时唤醒中断,32 768 Hz晶体停振检测唤醒和看门狗唤醒。

(3)Stop模式

在这个模式下,芯片的时钟首先被切换到低频时钟XTLF(32 768 Hz), PMU模块自动将LDO18和LDO33都关闭,使工作在这两个电源域的模块都掉电以降低功耗。此时芯片只保留有RTC定时唤醒和管脚按键唤醒,其他唤醒源不支持。功耗只剩RTC的功耗和按键唤醒模块的功耗,其他数字模块的由于完全掉电,没有功耗。

图4 三种工作模式的功能和功耗模型

上述三种工作模式对应的功能和功耗模型如图4所示, Active模式下支持的功能最多,功耗也最大,相反,Stop模式下支持的功能最少,对应的功耗也最低。

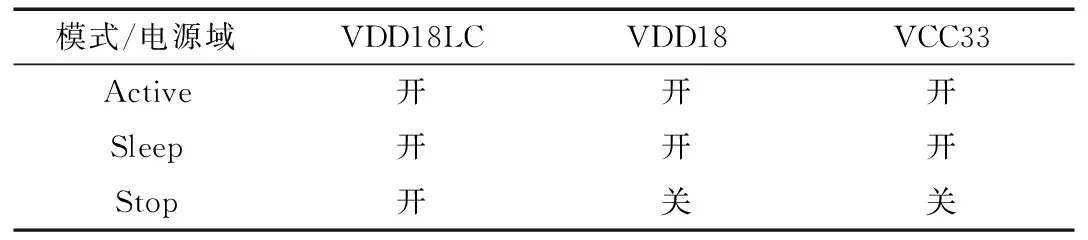

3.2 芯片低功耗电源设计

配合芯片的三种工作模式,芯片采用了多电源域的设计技术,整个芯片的内部电源分为三大块:VDD18LC,VDD18和VCC33,如图5所示。VCC33电源下工作的主要是模拟模块,包括ADC转换电路(ADC)、温度传感器(PTAT)、显示屏驱动(DISP DERIVER)、低电压检测(LVD)和比较器(COMP)。VDD18给大部分数字电路提供工作电压,包括M0 CPU、RAM控制器、SPI控制器等大部分的数字功能模块。当芯片工作在Stop工作模式时,VCC33和VDD18这两个电源域都支持关断,以降低芯片的静态电流。VDD18LC也是1.8 V数字电路工作电压域,只不过这部分电源只要芯片工作就需要常开,不支持局部关断,在这个电压域工作的电路有32 768 Hz振荡电路、RTC及补偿电路、按键检测电路。

图5 芯片电源域设计示意图

不同工作模式下电源域的开关状态如表1所示。

表1 工作模式与电源域

3.3 芯片低功耗电路设计

电路的动态功耗正比于电路翻转频率和电路规模,SoC电路中时钟的动态功耗约占芯片动态功耗三成。所以,降低芯片动态功耗的一大举措是降低时钟和信号的翻转频率。在本文设计的主控芯片中,降低动态功耗主要采取以下几种技术:

(1)门控时钟技术

对每个功能模块设计单独的时钟门控,在不需要模块工作时关闭模块时钟,减少时钟电路的翻转功耗; 同时,在对芯片的RTL代码进行综合时,插入时钟门控单元,这样寄存器输入端的时钟在信号不翻转时就不会翻转,极大地降低了时钟的动态功耗[9]。

(2)低功耗总线技术

现在的SoC设计都采用标准化总线完成芯片内模块的互联,总线的引入使得芯片设计进入模块化结构设计,方便系统的集成,也有利于系统的扩展。但另一方面, AHB总线和APB总线信号伸展到了芯片的每一个功能模块,从总线的互斥性可以看到,总线的主设备同一时刻只会访问一个从设备,但是不被访问的从设备的输入总线信号还是会跟随翻转,所以总线的无效翻转功耗很高。

本设计采用总线反相技术来降低总线的功耗。在每个时钟周期,总线矩阵处理模块将总线上当前数据总线值与上一个数据值进行比较,选择是发送原码还是反码,选择依据是哪一种码导致总线的翻转更少,设计时需要总线增加一位极性信号,以让接收模块正确地恢复总线上的数据。例如,如果当前周期总线数据为0000,下一个周期总线数据为1110,则总线下一周期实际会传输的数据是0001,同时将极性反转信号置起,这样从设备接收到这组信号后,会将总线数据取反,还原出真正的总线数据1110。这项技术极大地减小了总线的动态功耗。

(3)异步电路设计

在同步电路中,系统由全局时钟控制,在每个时钟脉冲到来时,所有的触发器都会运行,并消耗动态功耗,尽管在这个过程中一部分触发器并没有新的数据需要存取。而异步电路则没有这种无效的功耗浪费,系统的电路单元仅在需要其工作的时候才启动,完成工作之后就恢复静止状态,处于静止状态的电路单元仅仅消耗漏电流,而不会有无效的动态功耗。

在该芯片的设计中,对于部分在低功耗模式下需要工作的电路,在RTC、WDT和按键检测电路中,局部使用了异步电路设计技术,大大降低了这部分电路在低功耗模式下的动态功耗。

4 结论

本论文设计了一款集成RTC和多种常用通信接口的电表主控芯片,通过针对性地规划芯片的电源域和工作模式,在设计上融合多种低功耗设计技术,使电表在仓库存储、正常工作和电池供电等不同应用场景下,都能达到理想的低功耗。

该芯片在TSMC 180 nm 工艺线流片生产。对芯片在室温下进行实际测试,在三种工作模式下的功耗数据如下:

(1) Active模式:CPU从RAM 执行指令,芯片电流115 μA/MHz;

(2) Sleep模式:芯片工作模块包括RTC、IO检测模块和中断控制模块,RAM数据保持,芯片电流1.45 μA。

(3) Stop模式:芯片工作模块包括PMU、RTC和IO检测模块,RAM掉电,芯片电流0.85 μA。上述数据与目前德州仪器、英飞凌等国际大公司同类芯片的功耗数据相当,实现了非常好的低功耗性能[9-11]。

[1] 国家电网公司企业标准Q/GDW1364-2013 单相智能电能表技术规范[S].2013.

[2] 赵东艳,周芝梅,王于波,等.一种基于累积误差控制的RTC补偿算法及电路[J].电子技术应用,2014,40(3):66-68.

[3] 申斌.智能电表系统的设计与研究[D].南京:南京林业大学,2013.

[4] 静恩波.智能电网AMI中的智能电表系统设计[J].电测与仪表,2010,S2(4):46-49.

[5] ARM Limited. Cortex-M0 integration and implementation manual[Z]. 2009.

[6] ARM Limited. Cortex-M0 User guide reference manual[Z]. 2009.

[7] 马芝.低功耗方法在SoC芯片设计中的应用[J].中国集成电路,2010,19(9):38-46.

[8] 崔义智.低功耗技术在后端设计中的应用[D].上海:复旦大学,2008.

[9] Freescale. K17 sub-family reference manual[Z].2014.

[10] ST. STM32L063R8C8 reference manual[Z].2014.

[11] Texas Instruments. MSP430F41x2 data sheet[Z]. 2011.

Research on the low power design of MCU used in smart meter

Zhou Zhimei1,2, Zhao Dongyan1,2, Wang Yanyan1,2, He Xujie1,2

(1. State Grid Key Laboratory of Power Industrial Chip Design and Analysis Technology, Beijing Smart-Chip Microelectronics Technology Co., Ltd., Beijing 100192, China;2. Beijing Engineering Research Center of High-Reliability IC with Power Industrial Grade, Beijing Smart-Chip Microelectronics Technology Co., Ltd., Beijing 100192, China)

The construction of smart grid has led to a more and more complex function demand for smart meter. At the same time the meter must continue to work on field for no less than five years, so low power design requirement is very high for the Microcontroller Unit (MCU) of the meter. This paper focuses on the design of a MCU used in the smart meter, which integrates the function modules including RTC module, LCD driver module, and the common communication interface modules. The chip is designed in three work modes to meet the low power consumption demand of the meter in different scenarios. In the actual test, the chip is proved to achieve a very good power data in all three work modes.

smart meter; low power; MCU; work mode

TN492

A

10.19358/j.issn.1674- 7720.2017.16.009

周芝梅,赵东艳,王艳艳,等.电表用主控芯片的低功耗设计研究[J].微型机与应用,2017,36(16):30-32,40.

2017-02-21)

周芝梅(1977-),通信作者,女,硕士研究生,工程师,主要研究方向:信号处理与专用集成电路设计。E-mail:zhouzhimei@sgitg.sgcc.com.cn。

赵东艳(1970-),女,硕士研究生,高级工程师,主要研究方向:信号处理与专用集成电路设计。

王艳艳(1982-),女,硕士研究生,中级工程师,主要研究方向:专用集成电路设计。