LDMOS器件ESD防护特性分析与优化设计

王涛,黄龙,潘建华,赵秋森

(无锡中微晶园电子有限公司,江苏无锡214035)

LDMOS器件ESD防护特性分析与优化设计

王涛,黄龙,潘建华,赵秋森

(无锡中微晶园电子有限公司,江苏无锡214035)

LDMOS器件具有高输出功率、高增益、高线性、良好的热稳定性等优点,广泛应用于功率集成电路中,但在ESD防护过程中易发生双回滞而降低ESD鲁棒性。基于0.25 μm Bipolar-CMOSDMOS工艺,分析了LDMOS器件峰值电场的转移是发生双回滞现象并引起弱鲁棒性的主要原因,提出阳极用P+替代N+的版图改进方法。TLP测试制备的LDMOS器件显示,器件漏电流稳定维持在10-8A量级,二次失效电流大于9 A。结果表明,抑制的双回滞能有效增强鲁棒性,使其适用于高压功率集成电路的ESD防护。

LDMOS;双回滞;鲁棒性

1 引言

LDMOS器件具有高输出功率、大增益、高耐压和较低的导通电阻等优点,因而广泛应用于功率集成电路中[1]。同时,因其具有较强的耐压能力,常用作ESD防护器件[2~4],然而,在ESD应力作用下,LDMOS器件易发生双回滞现象,导致弱的ESD鲁棒性。因双回滞导致防护器件鲁棒性降低的现象已得到不少关注[5],但分析双回滞发生的物理机制,在保证器件的品质因子条件下提出合理的优化设计仍具有较大的工程应用价值。

本文基于0.25 μm BCD工艺制备了不同版图结构的LDMOS器件,结合TLP测试结果,分析了双回滞现象的原因及内部机理,结合现有的工艺条件,提出了合理的版图优化方案,证明了在抑制双回滞、增强ESD鲁棒性方面具有明显效果。

2 LDMOS器件测试与分析

2.1 器件ESD防护能力测试

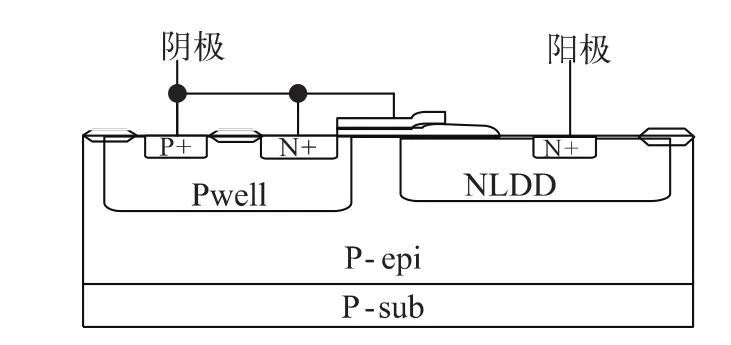

在P型衬底(P-sub)、P型外延(P-epi)的工艺下制备的LDMOS器件的结构剖面图如图1所示,在P型衬底上加入了N型轻掺杂漏(NLDD)版图,使其具备较高的耐压能力;同时,源区加入了P型掺杂注入(Pwell)版图,以保证器件具备较高的维持电压。将栅极、源极以及衬底接地,构成器件的阴极,漏极作为阳极。

图1 LDMOS器件结构剖面

2.2 器件ESD防护能力测试

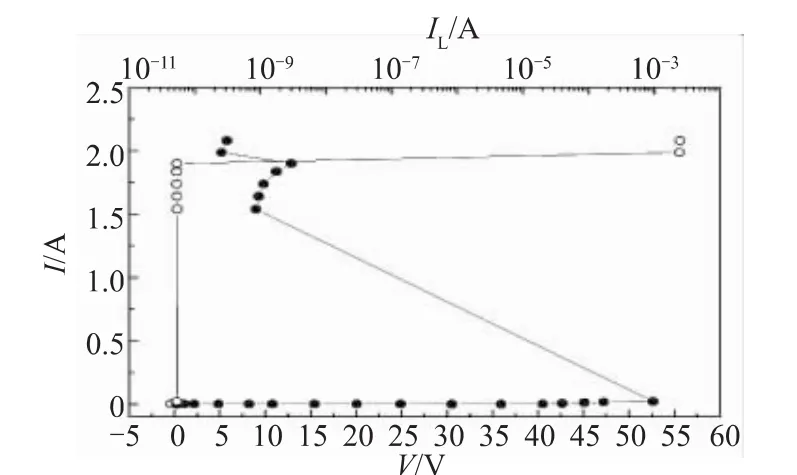

利用Barth 4002型TLP测试系统对制备的LDMOS器件进行测试,设置ESD脉冲测试信号的上升时间为10 ns,脉冲宽度为100 ns,步长为1 V。每施加一次TLP测试脉冲,同时对器件进行漏电流测试,即在器件两端加一高于工作电压10%的直流电压,测试器件中的漏电流。器件的测试结果如图2所示,其中实心符号代表电流-电压(I-V)特性,空心符号代表对应的漏电流(IL)。

图2 LDMOS器件的TLP测试I-V曲线

2.3 器件ESD防护能力分析

测试结果显示,随着器件两端ESD脉冲电压逐步增大,器件开始处于未开启状态,此时漏电流很小且稳定地维持在10-11A量级,当器件触发开启并发生第一次回滞,漏电流保持不变,当TLP电流增至2.0 A时,器件发生了第二次回滞,漏电流从5.40×10-11A增至2.43×10-3A,漏电流值急剧增大,表明器件已完全失效。

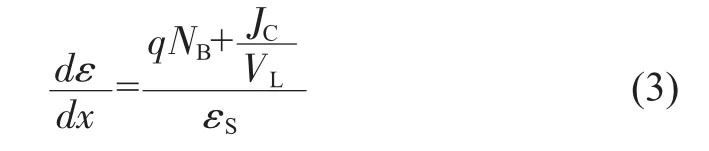

LDMOS器件在ESD应力下可等效NPN三极管结构,其简化的等效结构以及在不同电流密度下器件内部电场的分布如图3所示,其中阴极的N+等效三极管的发射极(E),Pwell和P-sub等效三极管的基极(B),NLDD和阳极的N+等效三极管的集电极(C)。在器件未开启,即电流密度较小的情况下(J=J1),空间可动电荷可忽略,由于集电结反偏,所以靠近集电结的基区的电子被抽走,最大电场出现在集电结上。由泊松方程可知,基区的电场分布为:

其中,NB表示基区的掺杂浓度,q表示电子电量,εS为相对介电常数。集电区的电场分布为:

其中NC表示集电区的掺杂浓度。

随着ESD应力增强,器件触发开启,并发生第一次回滞,此时电流密度增至空间可动电荷不能忽略时(J=J2),靠近集电结附近的基区的电子浓度不再为0,而是等于JC/VL,其中JC是集电极的电流密度,VL是电子的极限漂移速度(约为106cm/s),大电流会增加P型基区的净电荷密度,此时基区的电场分布可表示为:

大电流的注入会中和掉N-集电极区域的电荷密度,此时N-集电极区域的电场分布可表示为:

若电流的注入进一步增大(J=J3),当JC/qVL大于NC时,原来P型的基区变成了准中性区域,N-集电极变成带负电荷区域,最大电场出现在阳极的N+和NLDD之间,即基区扩展到了集电极区中,因为N+区域的掺杂浓度较大,此时雪崩倍增速度增强,器件两端的电压降低,第二次回滞现象发生。

图3 LDMOS器件的等效结构及其在不同电流注入下的电场分布

发生基区扩展现象会对LDMOS器件的ESD防护特性带来诸多不利的影响。首先,基区的展宽会使寄生NPN三极管的放大系数下降,降低器件的ESD泄放效率;其次,器件最大电场由原来的N-和P-well区域转移到N-和N+之间,漏端成为器件最脆弱的地方,强电场集中分布在漏端使器件具有极差的ESD鲁棒性。

3 提高鲁棒性的优化设计

从上述分析可知,为提高器件的二次失效电流,增强器件的鲁棒性,可采取增大漏极到栅极距离的方法,限制集电极的电流密度,从根本上避免超过发生基区展宽效应的临界电流密度值,但是此方法不仅会提高器件的导通电阻,而且占用较大的版图面积,结合本批次制备工艺的特点,在不增加版图面积、合理控制制造成本的前提下,利用P+版图代替阳极的N+版图,优化后的器件结构剖面图如图4所示,与传统的LDMOS相比,主要区别在于将LDMOS器件漏极中的N+注入换成P+注入,避免了等效三极管中集电极具备不同浓度分布的结构,从而抑制了双回滞现象的发生,并且当ESD应力作用于器件时,可形成一个类似SCR结构的PNPN路径泄放ESD电流,因此在保证其他参数不变的情况下,具备较强的ESD鲁棒性。

图4 优化后LDMOS器件的结构剖面图

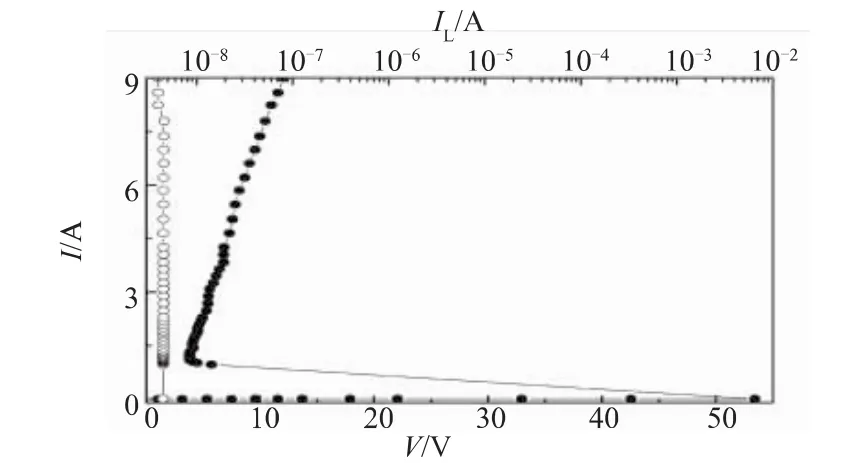

利用10 ns上升时间和100 ns脉冲宽度的TLP测试系统对制备的优化器件进行测试,结果如图5所示,其中,实心曲线代表TLP I-V曲线,空心曲线代表对应的漏电流。由测试结果可知,一直达到9 A也没有出现明显的失效现象。

图5 优化后LDMOS器件的TLP测试I-V曲线

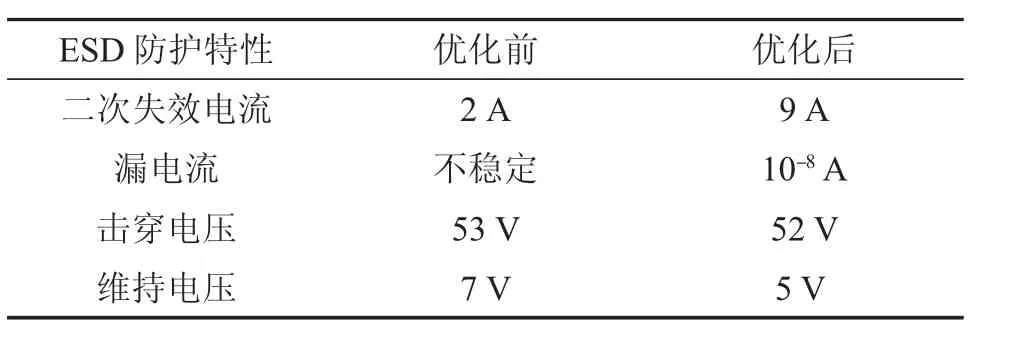

器件改进前后ESD防护特性对比结果如表1所示,击穿电压和维持电压基本保持不变,优化后器件漏电流稳定维持在10-8A量级,表明器件已经有效地抑制了双回滞现象的发生,同时二次失效电流提高到9 A以上,器件具有较强的鲁棒性。

表1 优化前后LDMOS器件ESD防护特性比较

4 结论

提出了版图的优化方法,利用P+替代N+制备了LDMOS器件,二次失效电流大于9 A,验证了版图优化方法对抑制双回滞现象、增强器件鲁棒性的有效性。优化的LDMOS器件适用于片上高压功率集成电路的ESD防护,为该工艺平台的高压ESD防护设计提供了有益的参考。

[1]黄晓兰,等.功率RFLDMOS的关键参数研究[J].半导体学报,2006,12.

[2]汪洋,等.18 V LDMOS器件ESD电流非均匀分布的模拟和测试分析[J].固体电子学研究与进展,2012,32.

[3]Wang C T,et al.ESD protection design with lateral DMOS transistor in 40-V BCD technology[J].IEEE Transactions on Electron Devices,2010,57.

[4]李梅芝,等.栅压对LDMOS在瞬态大电流下工作的温度影响[J].半导体学报,2008,28.

[5]Ker M D,et al.Double snapback characteristics in high-voltage nMOSFETs and the impact to on-chip ESD protection design[J].IEEE Transactions on Electron Device Letters,2004,25.

Analysis of ESD Protection Characteristics and Optimization for LDMOS Devices

WANG Tao,HUANG Long,PAN Jianhua,ZHAO Qiusen

(Wuxi Zhongwei Microchips Co.,Ltd.,Wuxi 214035,China)

LDMOS is widely used in high voltage ICs by reason of its high output power,high gain,high linearity and excellent heat stability.The ESD robustness of LDMOS devices may be weakened by the double snapback occurred in the high voltage ESD protection process.The LDMOS device analyzed in the article is fabricated in 0.25 μm Bipolar-CMOS-DMOS process.The failure and weak robustness are mainly caused by the peak electric field transfer.To solve the problem,the layout of LDMOS is modified using the P+instead of the N+.The TLP test results indicate that the leakage current remains the level of 10-8A and the second failure current is more than 9A.The robustness of the optimized LDMOS can be effectively strengthened due to the suppressed double snapback,providing a suitable ESD protection solution for high-voltage power integrated circuits.

LDMOS;double snapback;robustness

TN602

A

1681-1070(2017)08-0041-03

王涛(1984—),男,湖南郴州人,硕士,毕业于南京大学,工程师,现在无锡中微晶园电子有限公司工作,主要研究方向为半导体器件的设计及射频器件测试应用等。

2017-1-5