输出电容对LDO稳定性影响分析

何光旭,马文超,王彬

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

输出电容对LDO稳定性影响分析

何光旭,马文超,王彬

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

由于线性调节器内部没有开关管产生的交流开关损耗,同时比开关电源具有较低的RFI干扰,因此在现代电源系统中,仍然有它的一席之地。低压降集成线性稳压器即LDO是线性调节器的一种,一般采用P-FET或者PNP作为调整管,导通压降可以小于100 mV,效率得到大大提升,在射频、无线、电池供电等领域得到广泛应用,但必须对其做环路补偿,才能稳定工作。首先讨论了内部补偿、前馈电容补偿和输出电容补偿之间的关系,然后给出如何选择输出电容,最后以某输出可调LDO为例做仿真,说明输出电容对LDO稳定性的影响。

LDO;前馈补偿;输出电容补偿

1 引言

低压降集成线性稳压器相对于常规线性稳压器来说,由于压降小、效率高等特点,在电子设备中得到广泛使用。调整管采用PMOSFET或者PNP晶体管,导通压降甚至可以做到小于100 mV,功耗大大降低,效率得到明显提升,在低电压大电流的场合更为明显。但LDO组成的电源环路中,由LDO内部误差放大器形成的低频主极点Pdom、输出端旁路电容Cout和负载RL构成负载极点Pload以及由PFET或者PNP晶体管的输入电容和驱动门级或基级的输出阻抗形成电源极点Ppwr。因此,需要对LDO环路进行补偿,才能稳定工作。目前常用的补偿方法有内部密勒补偿[1],前馈电容补偿[2]和输出端旁路电容补偿[3],这三种补偿方法不是孤立存在的,而是相辅相成的,然而在目前的文献资料中都是将它们分别讨论,文章对三种补偿方法进行统一分析,给出LDO环路中输出电容选择的思路。

2 LDO环路结构和小信号模型

2.1 LDO环路结构

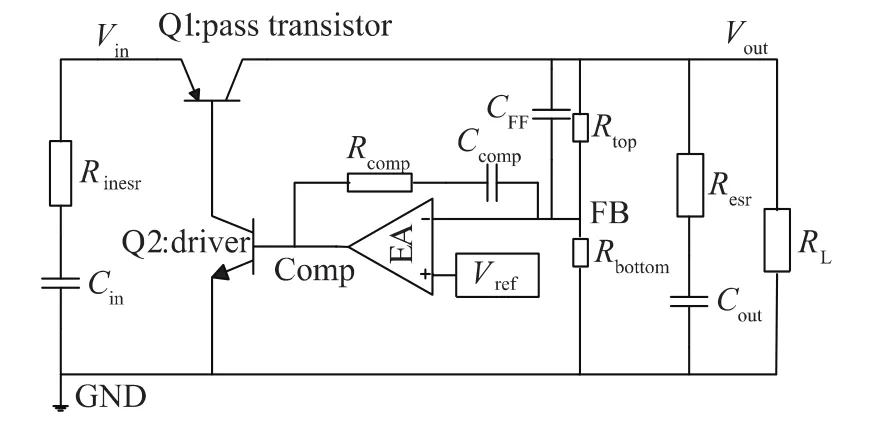

由PNP构成的LDO电路如图1所示,Vout经过分压电阻网络Rtop和Rbottom形成反馈电压Vfb,输入到内部误差放大器(EA)的反向输入端,EA的正向输入端接芯片内部基准电压Vref,由运放放大器虚短虚断原理可得到Vout和Vref满足关系式(1):

图1 LDO环路结构图

当由于外界因素导致Vout即Vfb变化时,PNP管的基极电压发生变化,使得PNP工作在线性电阻区或饱和区的不同位置,总使Vout与Vref恒满足关系式(1)。通常先选择Rbottom保证其与Rtop形成的串联支路电流是Ifb的100倍以上,再根据输出电压要求通过式(1)得到Rtop。

2.2 LDO小信号模型

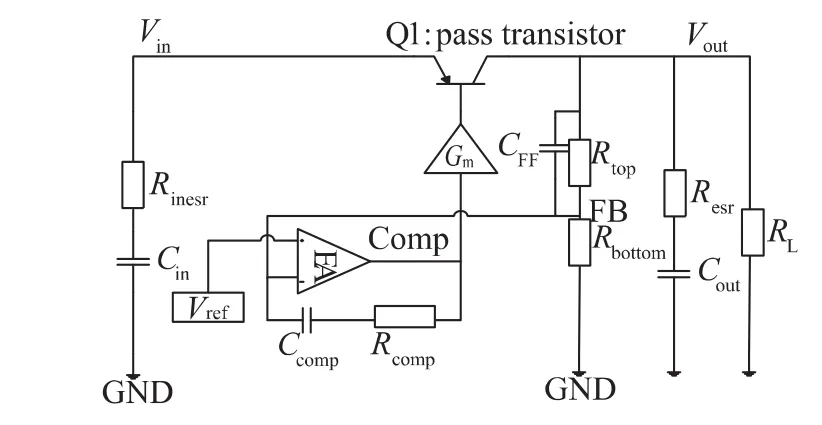

图2中,CFF与负反馈分压电阻Rtop并联作为前馈补偿电容,可以提高系统稳定性、PSRR、减小输出噪声和提高负载瞬态响应;利用输出端旁路电容的等效串联电阻RESR进行环路补偿,提高系统带宽和相位裕度;在LDO内部,误差放大器的反向输入端和输出端之间通常会设计一个电阻串联一个电容作为内部补偿网络。从负反馈控制理论来说,闭环系统稳定的前提条件是开环系统足够的相位裕度和幅值裕度,上述三种补偿方法主要从相位裕度角度进行考虑,保证系统在开环转折频率处有足够的相位裕度。

图2 LDO小信号模型

3 LDO环路补偿分析

3.1 前馈补偿

前馈补偿电容CFF对LDO反馈回路形成一个零点ZFF和一个极点PFF,即:

图3 LDO系统零极点波特图

当Rtop/Rbottom>>1时,即输出电压Vout比较大时,PFF大约是ZFF的Rtop/Rbottom倍。PCOMP是由弥勒补偿极点,PLOAD是负载极点,PCOMP和PLOAD构成系统的两个低频主极点;PPWR是由P-FET或者PNP功率管的输入电容和驱动该功率管的输出阻抗形成的电源极点,与寄生参数形成的极点构成系统的高频极点(图3中未标出)。

从图3中可以看出,ZFF的引入可以提高系统的相位裕度,从而提高系统稳定性。但这里需要指出的是,当输出电压比较高时,即Rtop/Rbottom比较大时,ZFF和PFF分得比较开,相位裕度提升更为明显;反之,如果输出电压很低,比如输出电压接近参考电压时,CFF对相位裕度的提升效果不明显。在这种情况下,需要用到3.2节所述的大多数LDO采用的补偿方法。

3.2 输出电容ESR补偿

输出端连接的旁路电容Cout都有一定数值大小的ESR,对系统而言,引入了一个零点ZESR,计算公式如下:

从图4中可以看出,ZESR可以显著提高相位裕度和带宽,但是相同容值不同封装、材质、厂家、批次的电容,其RESR会有所不同,而且同一个电容的RESR会随着温度的变化而变化,导致ZESR的位置发生变化,因此对能使LDO稳定输出的电容ESR有一个范围要求,即最大和最小值。

最小ESR要求限定了最大值ZESR_max,如果实际电容比要求的最小ESR小,那么ZESR右移,当接近或超过转折频率时,对相位裕度提升很小或没有提升;最大ESR要求限定了最小值ZESR_min,如果实际电容比要求的最大ESR大,ZESR会左移,对带宽提升过多以至于高频极点使系统变得不稳定。

图4 LDO系统零极点波特图

陶瓷电容或低ESR钽电容,具有良好的高频噪声滤波效果和快速瞬态响应能力,但从上面的分析看出,如果不对电路进行其他补偿,陶瓷电容或低ESR的钽电容可能会导致输出不稳定。

3.3 内部密勒补偿

为了降低对输出端电容ESR的苛刻要求,芯片设计师常常对内部误差放大器进行补偿,如图1中所示,Rcomp和Ccomp引入了低频主极点PCOMP的同时也进入了一个零点ZCOMP,这个零点的作用等同于ZESR。有了内部零点补偿,降低了对输出电容ESR的要求[3]即ESR下限可以为0 Ω,但同时也降低了上限,因为误差放大器提供的零点和负载ESR提供的零点会使得带宽增加,从而导致高频干扰,使系统不稳定。

4 仿真结果

下面以某输出可调LDO为例说明在实际应用过程中产生的输出不稳定现象(如图5所示),并进行仿真分析。该芯片具有超低的输入电压范围(1.5~7 V),输出电压可通过分压电压可调,芯片内部误差放大器补偿点通过Comp管脚引出,简化外部补偿元件,使用时将Comp引脚与输出端连接10 nF的陶瓷电容即可。与Rbottom并联的电容Cx补偿了输出电容零点,即:

Rbottom根据输出电压要求选定为10 kΩ,产品手册推荐使用的电容范围是10~220 μF,ESR范围是10 mΩ~2 Ω,为了能对不同负载变化时有较好的瞬态响应能力,这里选用220 μF,通过查找电容手册可以得到对应的ESR(35 mΩ),可以计算出Cx=1 nF。

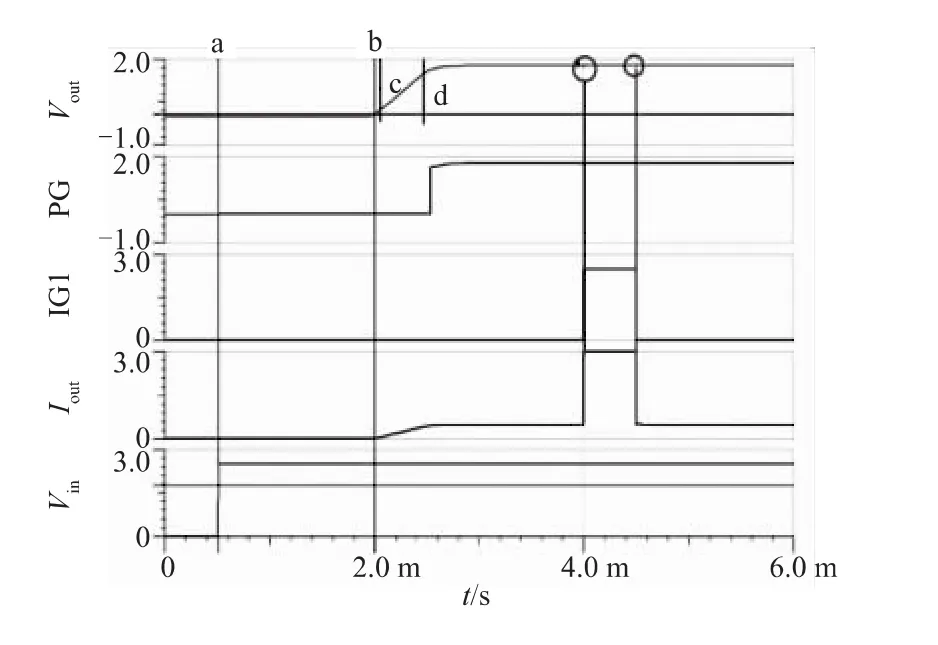

Vin=2.5 V,Vout=1.8 V,负载电阻RL=3.6 Ω,在4 ms时突然增加2.5 A负载(输出current limit设为3.5 A),仿真时间为6 ms,仿真结果如图6所示。长线a和长线b之间为芯片启动时间(约1.5 ms),短线c和d之间为输出软启动时间,在t=4 ms时,输出电压略微下降,t=4.5 ms时负载突然减小,输出电压略微向上过冲。仿真结果表明,ESR小于100 mΩ能适应不同负载突变的情况,在大负载情况下若ESR大于100 mΩ,Vout输出不稳定。

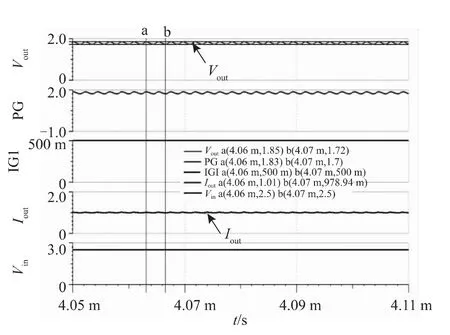

图7中ESR=500 mΩ、t=4 ms时负载从500 mA突变到1 A,输出有约4%的纹波电压,当负载再增加时可减小电容ESR,否则Vout输出不稳定。

图5 电压输出波形

图6 ESR=100 mΩ、Iout=0.5~3 A、t=4 ms时仿真结果

5 结论

综上分析,选择输出电容时要考虑以下因素:

(1)电容稳定性,由于要求LDO的输出滤波电容和ESR具有较好的稳定性,钽电容是最好的选择。陶瓷电容由于受温度和直流偏压影响很大,不适合大多数LDO应用[4]。

图7 ESR=500 mΩ、Iout=0.5~1 A、t=4 ms时仿真结果

(2)参考产品手册说明对输出电容的最小值要求和ESR范围要求。结合LDO内部电路结构,大部分厂家会给出LDO最小输出电容要求和在不同负载下能稳定的电容ESR范围,为选择输出电容提供了参考依据[5]。

(3)在PCB layout方面,要尽可能使电容靠近输出端,用粗线连接电容焊盘和芯片输出管脚,电容接地端用过孔与GND平面或者内部plane连接,以消除走线电感引起的振铃现象,过大的寄生电感可能导致选择的电容失去应有的滤波效果。

[1]Bruce Carter,RonMancini.Op Amps for Everyone[M]. Burlington:Texas Instruments Inc,2009:98-103.

[2]Pros and Cons of Using a Feedforward Capacitor with a Low-Dropout Regulator[EB/OL].http://www.ti.com/lit/an/ sbva042/sbva042.pdf,2014-7.

[3]AN-1482 LDO Regulator Stability Using Ceramic Output Capacitors[EB/OL].http://www.ti.com/lit/an/snva167a/snva 167a.pdf,2013-4.

[4]LP2989 Micropower and Low-Noise,500-mA Ultra Low-Dropout Regulator for Use With Ceramic Output Capacitors[EB/OL].http://www.ti.com/lit/ds/symlink/lp 2989. pdf,2015-3.

[5]ESR,Stability,and the LDO Regulator[EB/OL].http://www. ti.com/lit/an/slva115/slva115.pdf,2002-5.

Analysis of Effect of Output Capacitor on LDO Stability

HE Guangxu,MA Wenchao,Wang Bin

(China Electronic Technology Group Corp No.58 Research Institute,Wuxi 214072,China)

Linear regulator has no switch transistor that generates AC switch loss and thereby incurs lower RFI interference than switching power supply.Low dropout regulator(LDO)generally uses P-FET or PNP as regulated transistor to obtain<100 mV dropout voltage,which enables its wide application in RF,wireless and battery supply.However,LDO must be compensated to work stably.In the paper,the relationship between internal compensation,feedforward capacitor compensation and output capacitor compensation,and efficient selection of an output capacitor are discussed.The simulation result of TPS7H1101 shows the effect of output capacitor on LDO stability.

LDO;feedforward compensation;outputcapacitor compensation

TN432

A

1681-1070(2017)08-0029-04

何光旭(1984—),男,江苏南京人,硕士,毕业于东南大学,微电子工程师,主要从事集成电路应用及市场工作;

2017-3-9

马文超(1987—),男,安徽人,硕士,毕业于四川大学,应用工程师,主要从事开关电源应用工作;

王彬(1982—),男,吉林人,硕士,毕业于韩国清州大学电子工学院,产品经理,主要从事电源系统研究工作。