低应力非晶硅薄膜的制备

王剑敏

(上海华虹宏力半导体制造有限公司,上海,201206)

低应力非晶硅薄膜的制备

王剑敏

(上海华虹宏力半导体制造有限公司,上海,201206)

本文研究了三种降低非晶硅材料应力的手段:优化工艺参数。通过N2退火,将非晶硅的压应力变为张应力。通过额外的掺杂硼来改变非晶硅的应力。最初加入硼掺杂后应力会发生突变,但随着同步掺杂的浓度增加,最终的应力变化会趋向缓和。通过综合利用以上三个手段,最终的实际结果达到了预定的低应力目标。

低应力;非晶硅;微机械;半导体制造

0 引言

非晶硅材料被广泛运用在微电子和微机械的工艺制作中。在微机械工艺中,经常会淀积较厚的非晶硅材料作为机械结构或非晶硅牺牲层,这时非晶硅本身的力学参数,特别是对应力的要求就比较苛刻。当非晶硅薄膜自身具有较大的的应力时,微机械结构会发生扭曲变形,影响结构的性能,当作为牺牲层时,还会发生刻蚀后结构坍塌等问题。为防止以上问题的发生,非晶硅的应力必须等到有效的控制,绝对值越小越好。

本文所涉及的非晶硅材料被运用在微电子与微机械结合的工艺中,在生长非晶硅材料前,微电子的器件都已做完,并已开始金属布线,为使得前层的金属布线不在非晶硅生长时受高温融化,所以必须使用增强型等离子体化学气相淀积方法,在400℃左右的温度情况下制备非晶硅,由于此时等离子轰击造成的压应力相对于低温的生长环境产生的张应力要大,所以一般的等离子体非晶硅薄膜都会是压应力。

1 降低非晶硅材料应力手段

(1)通过优化工艺参数,调整非晶硅材料本征的应力。【1】相关的文献描述中针对的都是在低压化学气相淀积法(LPCVD)中生长的多晶硅或非晶硅材料,典型的生长温度是在高温下550-700℃,研究不同淀积压力下膜应力与淀积温度的关系,随着淀积温度的变高非晶硅会进入到过渡区再转变为多晶硅,薄膜材料的应力也会由原来的压应力变为应力,再转变为压应力。但在本文增强型等离子体化学气相淀积(PECVD)的制备中,因为在较低温度下制备,产生的只能是非晶硅,所以不会有非晶硅到多晶硅的结晶及体积收缩的变化,很多工艺的变化趋势需要重新摸索。

(2)通过加热退火,将压应力变为张应力。【2】[3][4]在参考文献中的退火温度普遍都是在600-1000℃,而在本文中为不使得前层Al线融化,所以必须在400℃以下的退火温度下进行。在更高的温度和长时间的退火会使得应力的大幅下降,但因为本文在生长非晶硅材料前已集成了微电子电路,当然无法承受这样长时间及高温的热过程,所以此手段无论从退火的时间还是退火的温度考虑,都存在着很大的制约和局限性。

(3)通过额外的掺杂来改变非晶硅的应力。[5]通过参考相关的文献,通过n型或p型的同步掺杂会对薄膜最终的应力产生很大的影响。在非晶硅材料中,对于应力起作用的掺杂原子都以替位形式而存在,在通常情况下,P 型掺杂如硼掺杂会使薄膜趋向张应力,而n型掺杂如磷或砷掺杂,薄膜会更趋向于压应力。

本文希望通过综合以上三个手段,利用现有的生产设备进行具体实验,通过分析具体实验结果最终达到预定的目标。

2 实验条件及目标设定

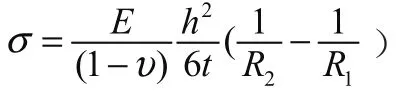

本文的实验条件:在无图形的监控硅片片上先淀积一层1000A 的TEOS(四乙氧基硅烷)基的SiO2薄膜,再在其上利用现有增强型等离子体(PECVD)设备淀积1.3um的非晶硅,通过测量前后的曲率半径,同时通过椭偏仪准确测量非晶硅薄膜的厚度,得到最终的应力,具体公式如下:

其中σ:薄膜平均应力(Pa)当符号数值为+时表明是张应力,当数值为-时表明是压应力。

E/(1-ν):衬底双轴弹性系数 对于(100) Si:E/ (1-ν)=1.805×1011Pa

h:衬底厚度(m) 一般制品衬底厚度725μm=0.725×10-3m

t:薄膜厚度(m)R1:成膜前衬底曲率半径(m)R2:成膜后衬底曲率半径(m)

最终的应力要求|σ|<50MPa。

3 优化工艺参数

为了得到本文所要求应力的非晶硅薄膜,首先列举影响工艺反应最终结果的工艺参数及可供工艺调整的范围如下:

温度:350-400℃,由于在本文的非晶硅运用中,前层已有Al 线,为了不使Al线融化,所以只能在较低的温度下进行。

压力:1-10Torr;SiH4:10-1000sccm;Ar:10-10000sccm;He:10-10000sccm

HF:10-1000W,LF:10-1000W.

通过变动以上参数,进行DOE 实验设计,如图 1各实验条件下等到的应力结果可知,应力可由最初的-473MPa 调整至-172MPa左右,但因为本文使用的是等离子体方法制备的非晶硅,本来薄膜的应力就可以看作是接受热能产生的张应力和等离子轰击产生压应力的综合,而在400度左右的低温下,等离子体轰击产生的压应力将占主导地位,所以即使怎么改变工艺参数,最终的应力值始终未能达到|σ|<50MPa的目标。

图 1 各实验应力结果

4 退火处理

在通过工艺优化调整的基础上,需要有一些额外的手段来进一步改变非晶硅薄膜的应力,因为使用增强型等离子体化学气相淀积法制备时,在等离体的轰击下,应力通常会呈压应力(负值),而当增加了退火热处理后,由于额外的热能会使得薄膜向张应力改变。

在本文的非晶硅应用中,非晶硅牺牲层被安排在前层具有Al 的工艺中,这也就意味着,后续的所有工艺和处理应保持在较低的温度下(典型在400度以下)进行,所以本文的退火处理只能运用现有的非晶硅工艺腔体,在400度的工艺温度下,通入N2作为退火气体,通过改变退火的时间,调查应力的变化趋势。

图2中应力变化差值随退火时间的变化趋势实在非晶硅本征应力-400MPa 左右的工艺条件下取得的,从可以看出,随着N2退火处理时间的增加,在100-300S的时间变化区间里,应力的改变值大致呈现线性关系。但硅片周边和中心区域的温度差难免有差别,随着退火时间的增加,硅片周边和中心区域的温度梯度造成了在硅片的周边区域目检发现严重的鼓包也随之增多。

针对优化工艺参数的实验条件下,即使通过300s N2anneal,非晶硅薄膜材料的应力也只能从-172MPa变为-139.3MPa,这说明了即使随着退火时间的增加,由热能带来的张应力会在一定的程度上抵消等离子体轰击带来的压应力。但随着退火时间的增加,由于毕竟还是在相对低的温度情况下(400℃)退火,抵消的程度有限,且退火时间也不能过长。

图2 应力变化差值随退火时间的变化

5 增加硼掺杂

经过以上实验改善,本文中利用增强型等离子体化学气相淀积法制备的非晶硅,应力绝对值还是维持在100MPa 以上,与目标值|σ|<50MPa 还有很大的距离。

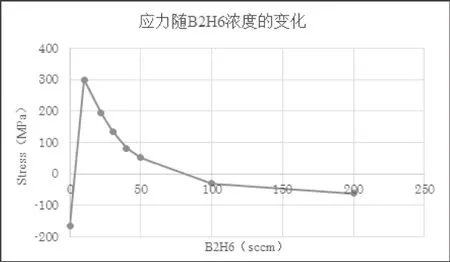

根据现有的文献报道,如在非晶硅成长的过程中,同步掺杂会对应力有很大的影响。当掺杂硼原子时会使薄膜趋于张应力,而是掺杂磷原子时会使薄膜区域压应力,所以我们选择了以B2H6 作为掺杂气体进行同步掺杂淀积,通过变化B2H6的流量,测量最终的应力变化趋势。

在本文中我们选取了B2H6流量0-200sccm,得到相关应力结果,从最终的应力随B2H6 浓度变化的趋势图图3来看,应力随B2H6流量的变化,并不是单向变化的,由等离子体制备的非晶硅,由于射频的轰击,薄膜本身呈现压应力,当在非晶硅淀积的同时B2H6流量的加入 ,起初非晶硅薄膜的应力情况会急剧变化至张应力且绝对值非常高,随着B2H6 的逐步增加非晶硅薄膜逐渐向压应力方向变化,当B2H6 的流量达到100sccm左右时,应力变化趋于缓和,当B2H6 =100sccm 时,|σ|<50MPa,达到预定的目标,且当B2H6 设定100sccm流量时,即使流量略有波动,应力也不会剧烈变动。

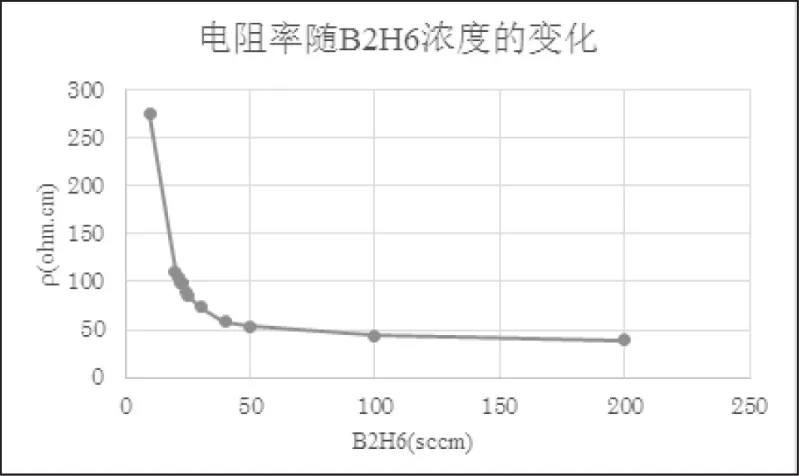

为解释应力随B2H6 浓度变化的机理,我们同时测量了相应的电阻率如图 4。因为都是在非晶硅淀积后直接测量应力和电阻率,非晶硅薄膜未经过高温退火,所以电阻率的变化直接反映了在非晶硅内替位式掺杂原子的多少,而替位式掺杂原子的数量,直接影响了薄膜的应力变化,。从图 4可以看出,随着B2H6流量的增加,起初电阻率急剧下降,应力也随着在非晶硅中加入了比硅原子小的硼原子而使得应力逐渐由最初的张应力转变为压应力,但当B2H6 流量的增加,电阻率趋于饱和,在非晶硅中的替位式掺杂硼原子趋于饱和,同时反映在应力的变化中,应力的变化也区域缓和。

图3 应力随B2H6浓度的变化

图4 电阻率随B2H6浓度的变化

6 总结

本文通过具体研究三种手段来降低非晶硅材料的应力,1.通过优化工艺参数,调整非晶硅材料本征的应力,但因为本文使用的是等离子体化学气相淀积的制作方法,所以等离子体轰击产生的压应力相对于低温产生的张应力起主导地位,所以调整的余地只是有限。2.通过加热退火,将压应力变为张应力。在本文中非晶硅薄膜在一定的退火时间内应力的变化差值呈线性关系,但由于退火的温度和时间受实际运用的限制,最后没有实际采用。3.通过额外的掺杂硼来改变非晶硅的应力,加入硼掺杂后应力会发生突变,但随着同步掺杂的浓度增加,最终的应力变化会趋向缓和。通过综合利用以上三个手段,最终的实际结果达到了预定的低应力目标。

[1]S.M.Sze,edit Semiconductor sensors.1977:64.

[2]H.Guckel,J,J.Sniegowski and Christenson.Sensors and Actuators.

[3]H.Guckel,D.W.Burns,C.C.G.Visser,H.A.C.Tilmans and D.DeRoo.IEEETrans.Electron Devices,1988,ED-35;800.

[4]P.Kruievitch,G,C.Johnson and R.T.Howe.Proc.Mat.Res.Soc. Symp.San Francisco,1992.79.

[5]M.S.Choi,E.W.Hearn.J.Electrochem.Soc.:Solid State Science and Technology,1984,151:2443.

Preparation of low stress amorphous silicon films

Wang Jianmin

(Shanghai Huahong grace Semiconductor Manufacturing Co.,Ltd.,Shanghai,201206)

Three kinds of methods were studied to decrease amorphous Si stress:1.Optimizing process parameter 2 Changing amorphous Si compress stress to tensile stress by N2 anneal 3 Changing amorphous Si Stress by additional boron dopant Stress was changed suddenly after added boron dopant at the very beginning,but by the in-situ dopant concentration increasing,stress variable trend will be alleviated.By making use of upper 3 kinds of methods comprehensively, final result achieved anticipated low stress goal

low stress; amorphous silicon; micromechanical; semiconductor manufacturing