数字信道化接收机的设计与实现

吕晨阳, 武明西

(中国船舶重工集团公司第七二四研究所,南京 211153)

数字信道化接收机的设计与实现

吕晨阳, 武明西

(中国船舶重工集团公司第七二四研究所,南京 211153)

在推导出实信号数字信道化的高效实现形式的基础上,通过硬件平台完成了1.6 GHz采样率32子通道数字信道化的硬件实现。在硬件实现过程中,介绍了算法的实现流程,对信道化关键模块——并行FFT模块的实现方法进行了重点介绍,并探讨了硬件模块与高速ADC数据接口方法,最后在硬件平台上对系统进行了实际测试,性能指标达到了设计要求,模块运行正确可靠。

数字信道化;多相滤波;现场可编程门阵列

0 引 言

作为电子战的重要组成部分,电子侦察在现代化的信息战争时代扮演着较重要的角色。为实现对非合作信号的侦察接收与高概率截获,电子侦察接收机常常需要较大的瞬时带宽覆盖、较高的接收灵敏度和较大的动态范围。相伴于电子技术的发展,电子侦察接收机先后经历过晶体接收机、瞬时测频接收机、超外差接收机、信道化接收机等多种形态。而其中信道化接收机利用并行的多个信道对信号进行覆盖,既具有外差式接收机的高灵敏度、高动态,又具有晶体接收机、瞬时测频接收机的宽频率覆盖,为较理想的电子侦察接收机体制。基于数字信号处理技术的数字信道化接收机因其在保证高灵敏度、大动态与瞬时覆盖接收的同时还具有信道一致性高、功耗较低、体积较小的优点而越来越得到广泛的应用。[1-3]

1 基于多相滤波的数字信道化高效结构

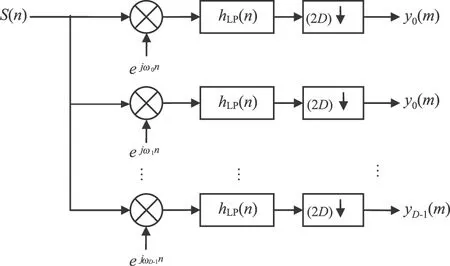

常规的数字信道化低通实现形式通过与多个不同频率本振数字混频和滤波抽取后将宽带接收信号搬移到基带,如图1所示。

图1 实信号滤波器组的低通实现

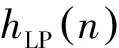

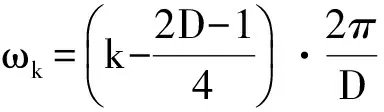

(1)

(2)

令

则有

(3)

(4)

式中

图2 信道化接收机模型

2 数字信道化接收机的实现

数字信道化接收机的硬件平台主要由高速采样ADC和处理FPGA组成。在实际使用时,前端接收机将接收到的射频信号转换为1.2GHz中频带通信号送至本平台。在本平台中,ADC通过带通采样模式,以1.6GHz采样速率完成对该1.2GHz中频信号的数字化,然后在FPGA内完成数字信道化处理。ADC选用Ti公司的ADC12D1800,FPGA选用Xilinx公司的XC7VLX485T。根据实际工程需求,设计子信道数K和抽取系数M为32,信道化后的数据率为50MSps。

2.1 高速模数转换

ADC12D1800芯片集成了两路独立的ADC转换器,具有12bit量化精度,每个通道最大1.8GHz采样率,并可通过交错采样,实现最大单通道3.6GHz的采样速率。其数据接口采用LVDS接口,内部集成了1∶1MUX或1∶2MUX,将输出的数据率降低。本文中ADC工作在1.6GHz采样率,采用1∶2MUX输出,每一路MUX的输出采用DDR模式,工作时钟为400MHz。

2.2 高速数据的并行接收

为了保证数据的有效接收,避免时钟沿的不稳定状态,数据与时钟的相对延时要求非常严格。决定数据和时钟的相对延时有两个因素:一是PCB板上时钟和数据走线长度,布线时控制并行线间和时钟的误差在5个mil以内;二是FPGA芯片内部的IO口延时和走线长度,该因素可借助FPGA内部的IDelay模块进行训练和延迟调节补偿以实现ADC数据稳定正确接收。

2.3 基于ISERDES的串并转换

如前所述,FPGA与ADC接口时钟为400MHz,实际数据传输率为800MHz,通常FPGA内部处理逻辑达不到该速率,因此需要对ADC输入的高速数据进行降速并行处理。这里借助FPGA内部串并转换器(dedicatedIOBinputdeserializer,ISERDES)硬件来完成该功能。ISERDES由串并转换器(serialtoparallelconverter)、数控延时单元(IDELAY)和滑动比特模块(BITSLIP)3部分组成。ISERDES支持单数据率(SDR)或双数据率两种采样模式,IDELAY具有64步长的延时调节功能,可以补偿布线的时延。BITSLIP可以重新排列输入的并行数据流。本平台设计ISERDES工作在1∶4的DDR模式,在FPGA内部得到200M的数据流,结合AD芯片内部的1∶2MUX完成对采样信号的8倍降速并行处理。

2.4 信号处理的实现

信道化接收机信号处理主要包括抽取、数字下变频、多相滤波和并行FFT。设计充分利用XILINX提供的成熟的IP核,并对算法中的一些运算进行优化。

2.4.1 多相下变频

2.4.2 多相FIR滤波器

根据子通道带宽和抑制比要求,利用FDATool设计滤波器系数,设计得到滤波器阶数为256,带宽为12.5MHz,阻带抑制比为60dB。由于是对复信号进行滤波,得到的信号带宽为25MHz。将滤波器系数进行抽取,得到多相滤波的每个子滤波器为8阶。FPGA内部的逻辑时钟为200MHz,而FIR滤波器的数据率为50MHz,故对滤波器进行1∶4的复用,降低资源消耗。信道滤波器幅度响应如图3所示。

图3 信道滤波器图

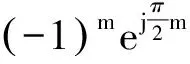

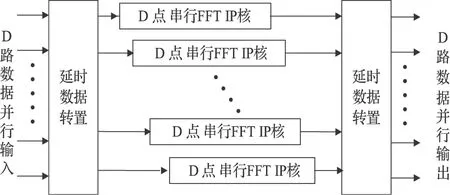

2.4.3 并行FFT单元

并行FFT核是该算法实现的关键技术之一。设计采用Xilinx公司串行的FFTIPCore为基础来进行并行FFT处理。实现的核心是将输入的并行数据转换成串行数据,同时保证能不间断地对输入的并行数据进行转换处理。本设计采用32点并行FFT,输入的数据分成组,每组32个数据,对每组的32个数据分别进行并串转换,输入串行FFT核,共采用8个FFT核,每个FFT核都是32点串行FFT核。每组数据延时一个时钟周期,同时每路FFT核输出结果的延时是一定的。所以,八路输出结果也是每路数据比上一路延时一个时钟周期。对输出结果进行并串转换,实现了并行的数据输入和并行的数据输入的效果。由于输入数据和输出数据的时序关系,保证了数据的连续输入和连续输出。实现框图如图4所示。

图4 利用串行FFT IP核构建并行FFT算法模型

3 实现与测试结果

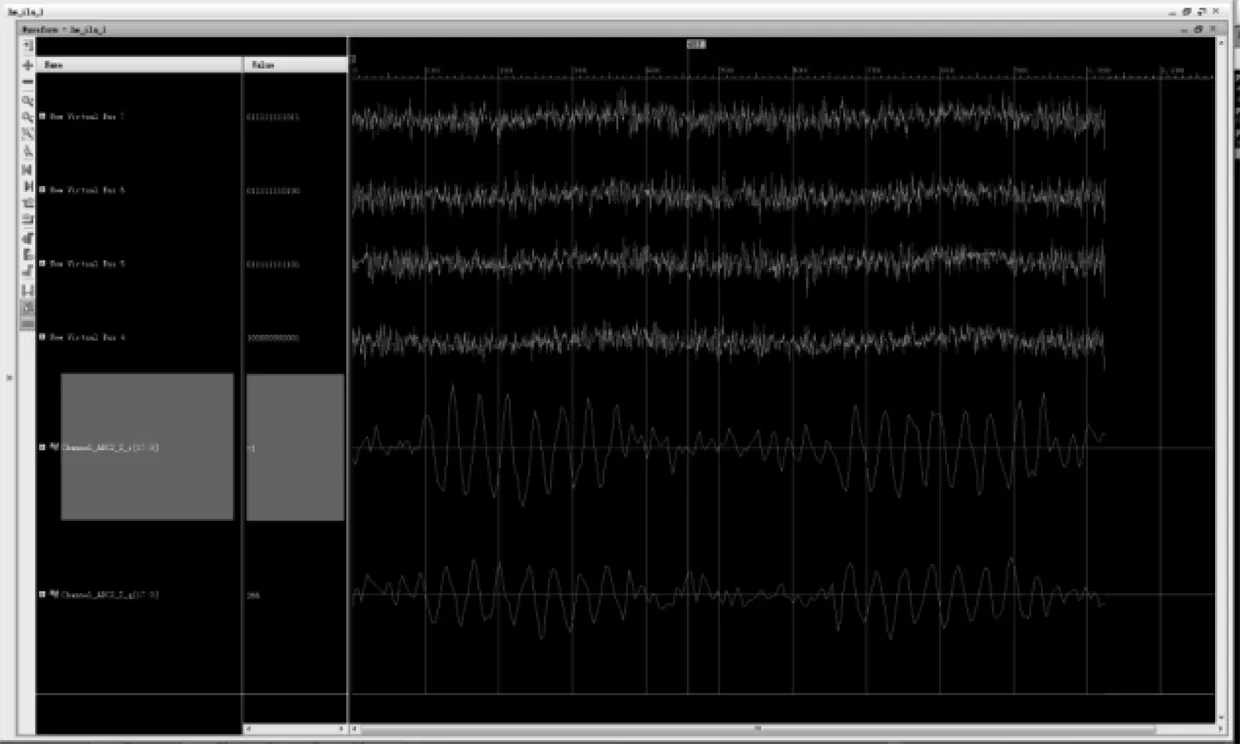

利用XILINX设计软件Vivado对设计结果进行综合、布局布线,生成比特流下载进FPGA芯片,通过前端输入功率为0dBm、频率为1.2GHz的连续波,通过开发环境的调试窗口抓取数据,将数据导入Matlab进行分析,得到如图5所示的结果。从图中可以看出,信号的无杂散动态范围大于60dB,计算得到ADC的有效位为8.6bit。

将输入信号功率降低为-50dBm,频率同样为1.2GHz,脉宽0.1μs,脉冲重复周期0.2μs,信号应在2、3信道输出,选择3信道抓取输出结果。图5中前4条信号为ADC输入的原始数据。从图中可以看出,信号已经淹没在噪声中,最下面的两条线为信号对应的信道输出的信号,分别为I路和Q路,此处信号的信噪比得到明显的提升。

图5 ADC数据频谱图

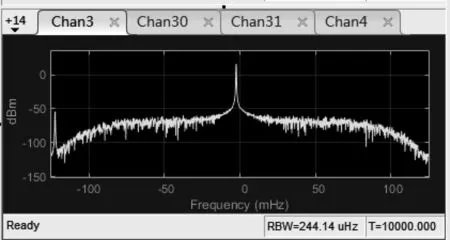

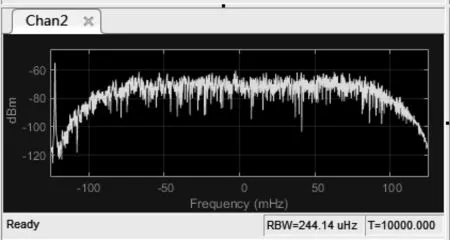

测试子信道分离度和抑制比。在ADC输入端叠加两个正弦信号,其中一个频率为1 210MHz,功率0dBm,另一个频率1 344MHz,功率-35dBm。通过Vivado调试接口抓取子信道数据并进行频谱分析,结果如图7所示。从图中可以看出,两个信号分别从3、21号子信道输出。信道3为1 210MHz的输出信道(如图8(a)所示),其功率为10dBm左右,显示功率未标校,利用相对值测量信道抑制比。图8(b)为非信号输出信道,其边缘的峰值为泄露的信号,从图中得到其功率为-50dBm左右,可以得到其差值为60dB左右。

图6 ADC原始数据与信道化输出结果

图7 部分信道输出频谱图

(a)

(b)

4 结束语

结合工程实践,笔者推导出基于多相滤波的数字信道化高效结构。该结构有效地降低了运算量和FPGA逻辑和运算资源,使算法的实时硬件实现变为可能。在高效实现算法基础上,利用FPGA完成了1.6 GHz采样率的32通道信道化接收机。经过测试,该接收机可有效分离不同频率的信号,信道外信号抑制比达到60 dB,能够满足宽带电子侦察接收机需求。

[1] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2] 杨静,吕幼新.高效数字信道化IFM接收机的研究[J].电子科技大学学报,2005, 34(1):444-447.

[3] 周欣,吴瑛.基于多相滤波的宽带接收机信道化算法研究[J].现代雷达,2006,28(11):71-74.

Design and implementation of digital channelized receiver

LYU Chen-yang, WU Ming-xi

(No.724 Research Institute of CSIC, Nanjing 211153)

Based on the derived highly-efficient implementation form of the digital channelization of the real signals, the hardware implementation of the 32-subchannel digital channelization is completed with the sampling rate of 1.6 GHz through the hardware platform. In the process of the hardware implementation, the implementation process of the algorithm is introduced with emphasis on the implementation method of the parallel FFT module, the key module of the channelization. Besides, the data interface method of the high-speed ADC and the hardware module is discussed. Finally, the system is tested on the hardware platform, indicating that its performance specifications meet the design requirements and the module operates correctly and reliably.

digital channelization; multi-phase filter; FPGA

2017-04-21;

2017-04-27

吕晨阳(1989-),男,工程师,硕士,研究方向:雷达信号处理;武明西(1983-),男,高级工程师,硕士,研究方向:雷达信号处理。

TN85

A

1009-0401(2017)02-0041-04