基于FPGA数字电压表的设计及实现

贾金明

摘要:针对传统的数字电压表可靠性低问题,该文提出了一种基于FPGA数字电压表的系统的设计。系统以Altera公司的高性能的FPGA芯片EP2C5T144C8N为控制核心,用硬件语言实现了数据采集、转换、显示等系统所需模块,通过硬件下载和测试,测试结果表明,该数字电压表测量系统可测量0~10V电压值,且精度较为0.02V。此设计方法可靠性较强。

关键词:数字电压表;数据采集;FPGA;EP2C5T144C8N

中图分类号:TF368 文献标识码:A 文章编号:1009-3044(2017)17-0256-03

随着电子技术的飞速发展,数字仪表在测量领域的作用显得更加重要,而数字电压表是数字仪表的核心,由于传统的数字电压表体积较大,精度较低,可靠性较差等缺点,本文提出了一种基于FPGA数字电压表的系统。该系统采用8位A/D转换器芯片ADC0809对输入的模拟电压进行采样,用FPGA芯片作为整个系统的控制核心,采用模块化设计方法对系统各个模块进行硬件设计,通过把整个系统设计下载到一片FPGA芯片上并通过显示模块进行显示测量电压的大小,系统能很好的显示要测量的电压量。且整个系统是在一片芯片上实现的,大大减少了传统设计系统的分立元件数量,降低了系统的耗能,增加了可靠性,且能较好地实现了电压的精准测量。

1系统设计

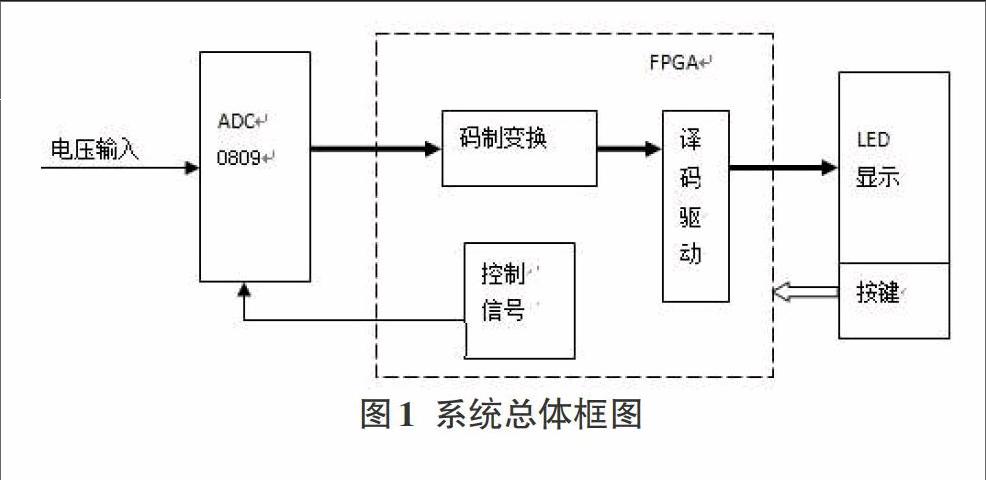

整个系统可以划分为FPGA芯片控制和A/D转换两部分,其中A/D转换芯片ADC0809的作用是将系统输入的模拟信号转换成数字信号,将转换后的数字信号送入FPGA芯片以待运算和处理;七段数码管的作用是将经FPGA转换后的BCD数据显示;FPGA芯片的作用是处理和协调,其中包含控制A/D数据的转换、接收A/D转换后的结果并进行编码、显示等。系统的总体框图如图1所示。

2系统的软件设计

当系统处于工作状态时,先将经A/D转换后的8位数据送入减法器,判断其极性以得到正确的信号正负值。然后将减法器输出的正确信号值送入移位寄存器,将其左移两位使得8位信号变为10信号。移位之后把数据送到可预置值减法计数器中,当有信号置入,减法计数器与加法计数器便同时开始工作,当减法计数器计数(减1计数)完毕,给加法计数器发送一个停止计数的信号,此时加法计数器停止计数,随后将加法计数器的三组BCD码值送入译码器,将三组BCD码译码为可驱动七段显示器的信号,并将之与一组代表极性的信号同时显示于七段显示器上。整个信号处理电路流程图如图2所示。

3系统的硬件设计

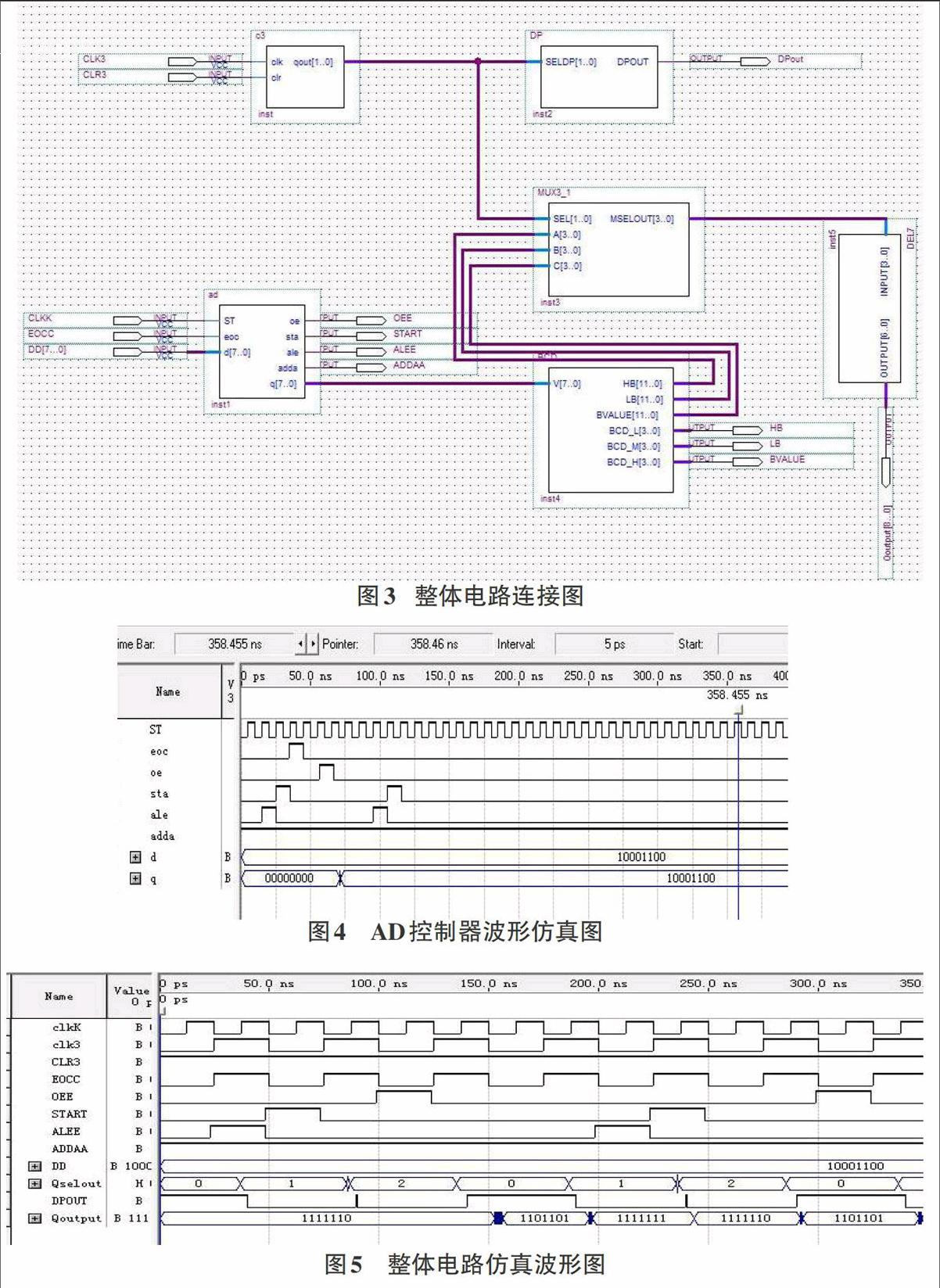

整个系统的硬件电路设计由控制模块、信号处理模块以及显示模块构成。将待测量信号(电压信号)送入A/D转换器,再由控制模块发出控制信号,启动A/D转换器的START开始转换,通过A/D周期采样得到的数字信号在信号处理模块中被转换为与电压信号对应的显示代码,随后显示模块发出控制与驱动信号,推动外部的显示器(LED)显示相应的数值,整个系统由外设键盘对系统进行复位操作。信号处理模块,将采集到的信号转换成与电压信号对应的数字显示信号。显示模块,是将信号处理模块对应输出的BCD码译成7段数码驱动值来显示。整个系统处于工作状态时,按固定的采样周期获取电压信号,经ADC0809转换为8位数字信号,此8位数字信号经FPGA芯片信号处理获得对应的12位数字码,再将这12位数字码显示信号导人数码管进行被测电压的显示。对ADC0809来说,它的输出共有256位,这表明芯片的分辨率为1/256,假设输入电压Vin为0~5V,则它的输出电压最小值是5/(256-1)=0.019V,这表明ADC0809所能处理的电压最小值约为0.02V,整个系统每个模块都是采取VHDL在QuartusⅡ编译环境下设计,整个顶层设计连接如图3所示,ADC控制仿真波形和整个电路的仿真波形如图4、5所示。

在AD转换控制器中,ST为时钟信号输入端,仿真是输入一个时钟信号。ECO为转换结束信号,当AD转换结束时,此端输出一个高电平(在转换期间ECO一直为低电平)。OE:数据输出允许信号,高电平有效,当AD转换结束时此端输出一个高电平,才能打开输出三态门,输出数字量。sta:AD转换启动脉冲输入端,输入一个正脉冲时期启动(上升沿使ADC0809复位,下降沿启动AD转换)。ale:地址锁存允许信号,高电平有效。adda:三位地址输入线,用于选通八路模拟输入中的一路。df7…0):输入电压。q:输出电压。

Start为A/D转换启动使能位,高电平使能,alee为信号输入选通端口锁存位,上升沿使能;start使能后,狀态显示位eoccc变为低电平,使整个系统进人转换模式,在此模式下st2对eoec信号位测试,要是为低电平则说明转换还没有完成,仍保持在st2下等候,等到状态反馈信号eocc跳变为高电平,转换结束并进入st3,并使oee变为高电平(输出使能),此时ADC0809的输出总线d(7…0)从高阻态变为有效输出信号。然后到状态st4,利用锁存信号(10ck的上升沿)将ADC0809输出的数据进行锁存。锁存的数据实质上先存在内部信号REGL中,再赋给输出端口Q,这个八位REGL信号,可用于后续模块数值转换和数码管的动态扫描,最终显示电压值。

4系统测试

设计采用的是EP2C5T144C8N的FPGA芯片其引脚与外围设备的连接如图6所示。ADC0809的ADDB、ADDC端口必须接地,时钟信号输入端CLOC所接的时钟信号为48kHz。

通过对整个系统进行软硬件调试,通过后进行硬件下载,为提高电路抗干扰性能,采取每个芯片的电源与地之间都接有去扰电容,类似数字地与模拟地分离的去干扰方式。整个系统的电路连接和调试成果如7图所示。

5结束语

通过测试,系统实现了量程为0~10V的电压测试,通过调节电压输入电位器,可以看到数码管上显示的数据跟着发生变化。使用该设计测一节全新的南孚碱性电池的电压输出值,数码管上显示的数值为1.599V。用数字万用表测量该南孚电池的电压为1.615V.测量误差=(1.615-1.599)=0.016V,量化误差=(0.016/1.615)*100%=0.99%<3%,从实际测量分析,该方法设计的数字电压表精度较高,具有很强的实际需求。