多个NIOS程序在EPCS中的存储及切换运行*

罗明华

(中煤科工集团重庆研究院有限公司,重庆 400039)

多个NIOS程序在EPCS中的存储及切换运行*

罗明华

(中煤科工集团重庆研究院有限公司,重庆 400039)

针对Altera FPGA,提出了一种在EPCS Flash中存入多个NIOS II嵌入式程序(不同的配置文件和NIOS II应用文件)并实现程序间相互切换运行的方法。通过搭建平台并以两个嵌入式程序为例,分别分析了它们的配置及引导流程,阐述了程序存储及切换运行的具体方法,实验结果证明了该方法的可行性。该方法使得带NIOS II软核的FPGA嵌入式系统在调试以及应用上更加方便灵活,尤其针对系统程序的远程更新,在不破坏原有程序的基础上即可完成,大大提升了系统的安全性。

FPGA;NIOS II;EPCS;程序存储;重配置;程序引导

引 言

FPGA(Field Programmable Gate Array,现场可编程门阵列)使用了预建的逻辑块和可重新编程布线资源使其具备自定义硬件功能,当用户在重新编译不同的电路配置时,能够当即呈现全新的特性[1]。尤其是它的嵌入式系统SOPC(System On a Programmable Chip)能够通过选择合适的CPU、外设和存储接口,以及定制硬件加速器等达到每一个新设计周期的独特目标[2]。

随着FPGA嵌入式系统的大规模应用,对程序的变更与维护在所难免,靠编程电缆进行现场的调试与更新十分不便。在具备通信接口的系统中进行程序的远程更新是很好的办法,基本流程是通过通信接口将程序以数据流的形式发送到FPGA中,FPGA使用IAP(In Application Programming,在应用编程)的方法将程序烧写到Flash中,再通过控制RSU(Remore System Update,远程系统更新IP核)进行FPGA的重配置[3]。而由于EPCS自带的引导程序只能识别紧随其后的应用程序,所以IAP烧写程序的同时也将原有基地址上的程序覆盖掉,而在覆盖过程中出现任何异常都极易造成原有程序及系统的崩溃[4]。为此,本文拟将第二个嵌入式程序存入到EPCS中未重叠的任何块上,并自行编写引导程序,以初始化文件的方式存入到由SOPC建立的ROM中,将CPU的reset地址指向此ROM,通过RSU重配置后CPU即可自动运行引导程序,实现第二个嵌入式程序的引导与运行。

1 系统结构

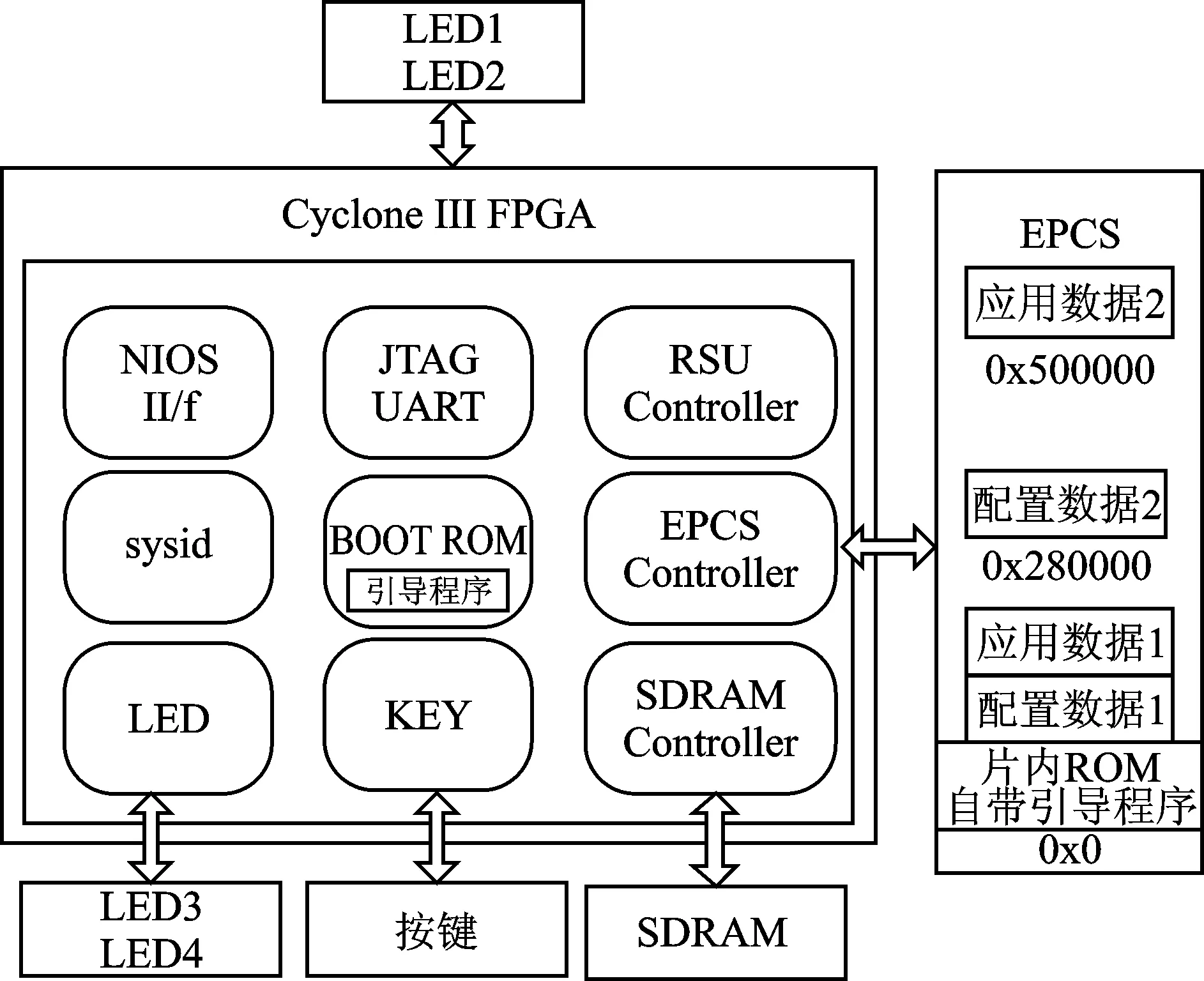

选用Altera公司EP3C16系列的FPGA以及EPCS64串行存储芯片,搭建如图1所示的SOPC系统。其中LED1和LED2为硬件直接控制的LED;CPU为32位RISC嵌入式软核NIOS II处理器;BOOT ROM是SOPC中建立的On-Chip Memory,专门用于引导代码的存储;JTAG UART是FPGA与PC间的一个桥梁,用于通信与调试;KEY与LED为PIO,用于嵌入式系统对外部按键和LED3、LED4的输入输出控制;EPCS Controller用来控制FPGA和EPCS的数据传输;SDRAM Controller用于控制外部SDRAM芯片;RSU Controller是Altera提供的远程更新模块,起重配置的作用。本系统将在EPCS中存入两个嵌入式程序,即程序1和程序2,两个程序间实现互相切换运行,以下将分别以两个程序为例进行讨论。

图1 系统框图

2 程序1

2.1 程序1的设置与烧写

系统中第一个程序,即上电启动程序,包含配置数据1和应用数据1。为了实现上电启动,在SOPC中将CPU的reset地址设置为EPCS,将exception地址设置为SDRAM,完成代码编写后生成配置文件和NIOS II应用文件。

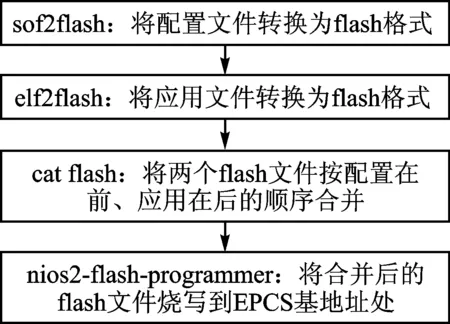

第一个程序在烧写时,应用文件必须紧随配置文件,使用NIOS II command shell合并文件并烧写到EPCS,流程如图2所示。

图2 程序1烧写流程图

2.2 程序1的引导过程

上电后,FPGA首先进入配置过程,配置完成后NIOS II被逻辑中的复位电路复位,从reset地址开始执行代码[5]。其中EPCS控制器基地址处有一段ROM存储区,存放有NIOS II的引导程序,所以NIOS II开始执行ROM中的引导程序[6]。引导程序通过读取EPCS中配置数据的头部信息获得配置数据的总长度,然后跳过配置数据直接找到应用数据,这也是应用文件必须紧随配置文件烧写的原因。随后引导程序将应用数据搬移到SDRAM中,搬移完成后指针跳转到SDRAM中执行刚才搬运过来的NIOS II嵌入式应用程序。

3 程序2

3.1 系统的重配置及引导过程

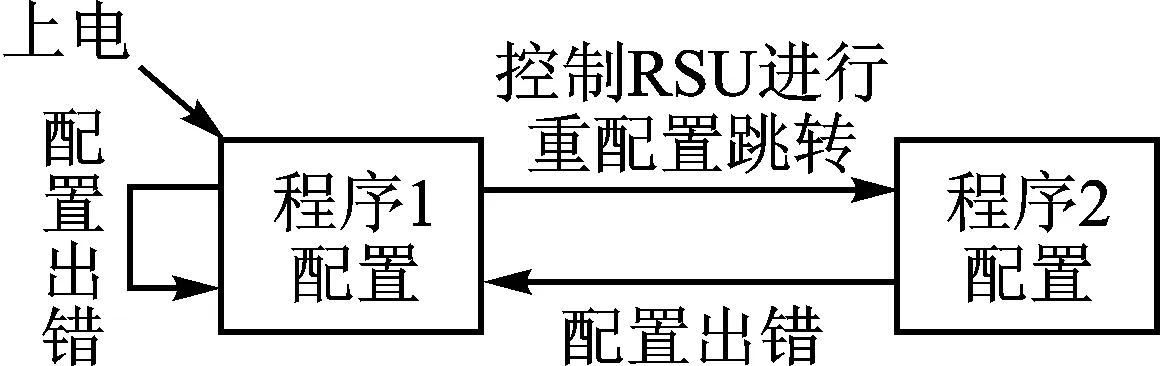

从第一个程序跳转到第二个程序,需要借助RSU Controller来进行重配置,其中RSU控制的配置逻辑如图3所示。

图3 RSU控制示意图

通过设置RSU的寄存器,可以使FPGA跳转到EPCS中任意块位置处,并根据此位置的配置数据进行系统的重配置,因此配置数据2可以存储在EPCS中的任意位置处。配置完成后,进入第二个程序应用数据的引导过程,这个过程无法使用EPCS控制器ROM中自带的引导程序,而需要自行编写。引导程序需要完成的任务是将应用数据2搬移到SDRAM并跳转指针到SDRAM执行相应的程序[7]。

图4 应用数据存储示意图

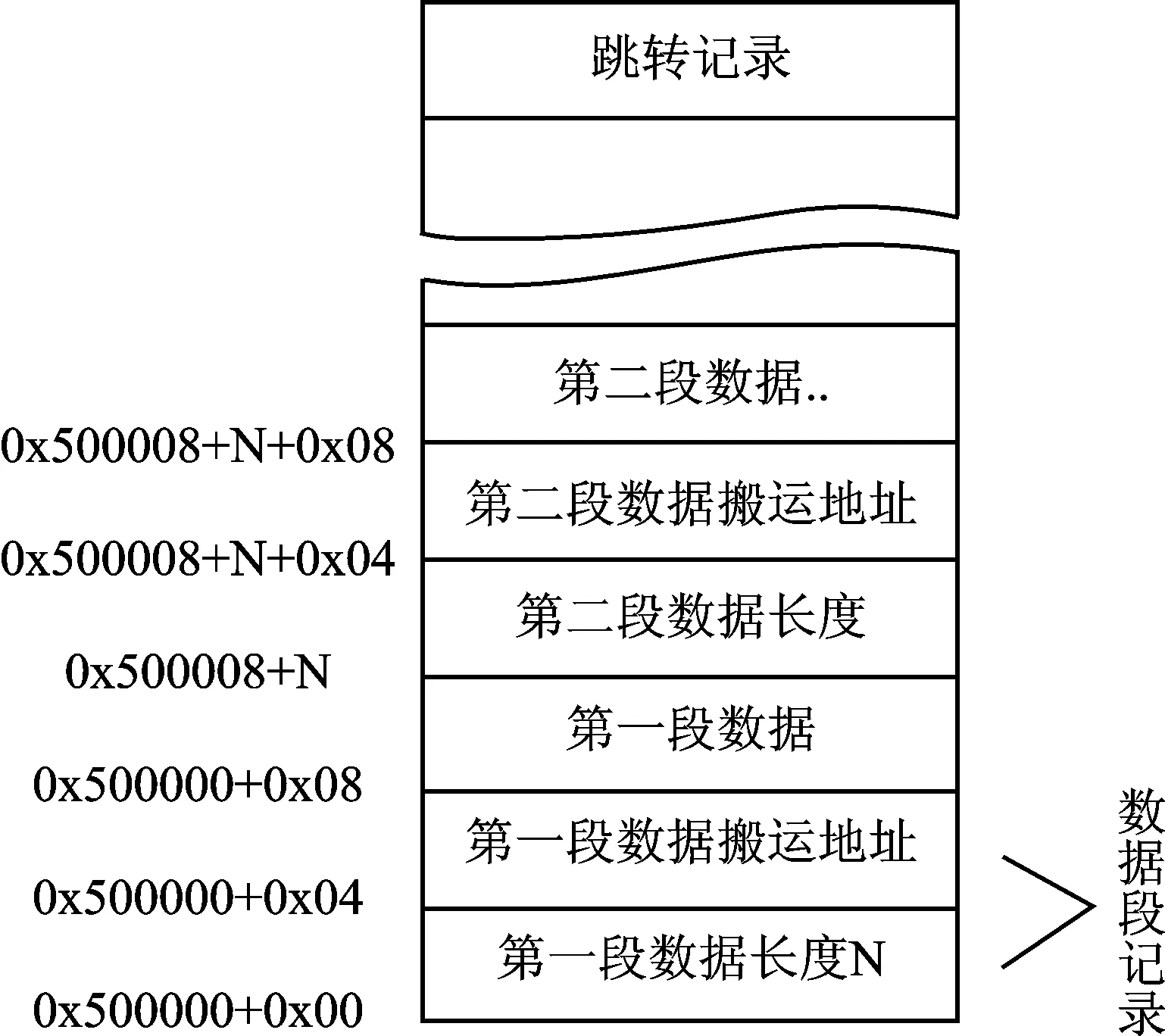

自行编写引导程序必须了解数据在EPCS中的存储方式。图4为本系统中应用数据2在EPCS中的存储示意图,数据被分为多个段,每个数据段由一个段记录和段数据构成,其中数据段记录由8个字节组成,前4字节表示本段数据的长度,后4字节表示本段数据所要搬运到的目的地址。紧随段记录之后的就是本段的有效数据。最后的段记录为跳转记录,前4字节均为0x00,表示数据的结尾,后4字节表示指针所要跳转到的目的地址[8]。按照应用数据在EPCS的存储方法,通过相应的NIOS II接口函数即可将应用数据从EPCS搬移到目的地址并运行。

引导程序属于应用程序编写,是在程序2的配置基础上进行的。要在配置完成后进入引导过程,reset地址需要指向引导程序存储的位置,由于EPCS中已经存储了程序1的数据,所以reset地址不能再选择EPCS,需要选择另外一个掉电不丢失的存储单元,即BOOT ROM。它本身是由IP核On-Chip-Memory构成的,让它掉电不丢失的办法是将编写的引导程序生成为BOOT ROM的上电初始化.hex文件(其中.text需要映射到BOOT ROM上),然后将初始化文件加载到Quartus中与硬件配置一同编译,最后生成的.sof配置文件中将自带BOOT ROM的初始化信息。将带有初始化信息的配置文件烧写到EPCS中,当FPGA通过RSU选择它并进行配置跳转时,BOOT ROM将被初始化而存储引导程序,FPGA在配置完成后即开始运行引导程序。

引导程序有两个地址需要关注:一个是应用数据2在EPCS中的存储地址,另一个是之前所提到的应用数据中段记录地址。第一个地址决定待搬移数据在EPCS中的源地址,它可以自行任意设置,所以应用数据2可以存储在EPCS中任意未重叠的位置处。第二个地址决定待搬移数据的目的地址,它是由CPU的reset地址所决定的,因此在编译应用程序2时,应该将CPU的reset地址由ROOT ROM改为SDRAM。

3.2 程序2的烧写

如上所述,程序2的配置文件和应用文件均可烧写到EPCS中任意位置,其中应用文件也不需要紧随配置文件烧写,但由于EPCS中程序的擦除及烧写都是以块为单位进行的,所以烧写的目的地址应该为各块的开始地址。

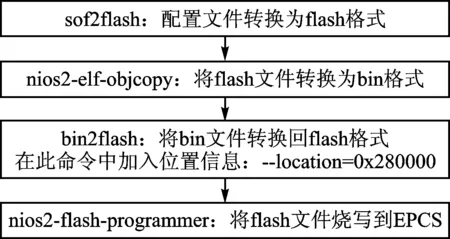

如图1中EPCS所示,本系统将配置文件2存放到EPCS偏移量为0x28 0000位置处,由于存在偏移量,所以并不能直接将sof文件转换为flash格式烧写,具体的烧写流程如图5所示。

图5 配置文件2烧写流程图

本系统将应用文件2存放到EPCS偏移量为0x50 0000位置处,烧写流程同上,需要先将elf文件转换为bin格式,再通过在bin2flash命令中加入位置信息- -location=0x50 0000以及使用烧写命令来实现对EPCS的带偏移量烧写。

4 实验结果

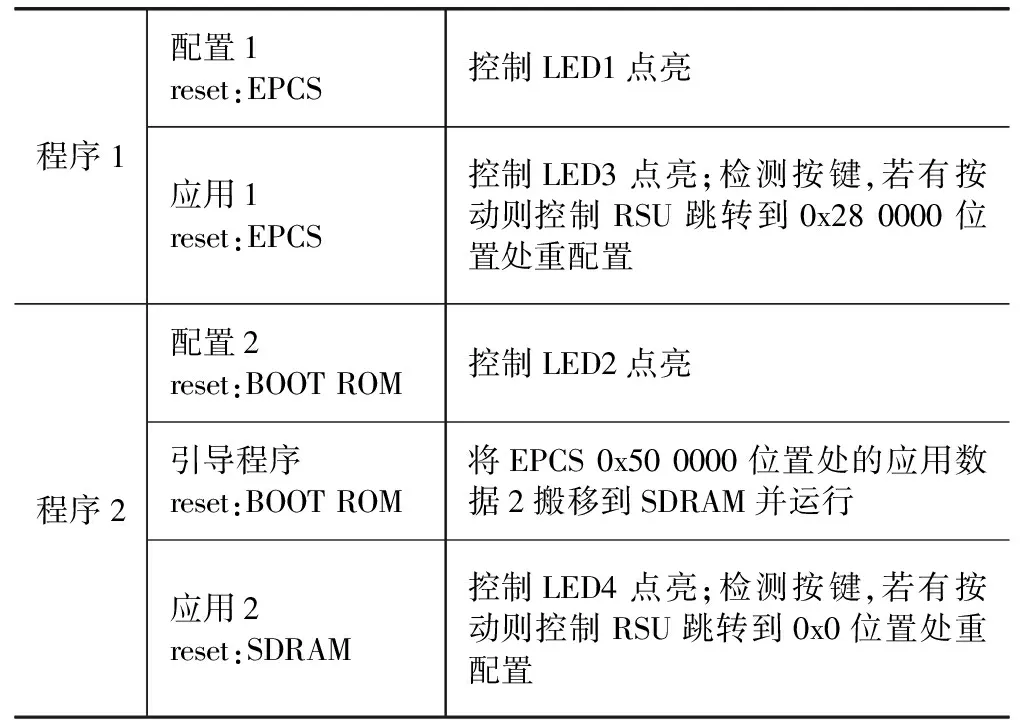

按上述方法搭建好如图1所示的SOPC系统,程序1和程序2的相关设置及功能如表1所列,其中reset表示SOPC中CPU的reset地址,如上方法所述,生成相关文件并烧写到EPCS中。

表1 程序1和程序2的相关设置及功能

烧写完毕后,系统重新上电,LED1、LED3将点亮,说明配置1和应用1正在运行;按下按键,LED1、LED3熄灭,LED2、LED4点亮,说明RSU已经控制在0x28 0000位置处进行重配置并通过引导程序启动了存储在0x50 0000中的应用;再次按下按键,重新回到程序1的状态。多次按动按键,现象来回跳转,说明程序1和程序2已经同时存储在EPCS中,并可完成程序间的切换。通过同样的方法,可以实现更多程序在EPCS中的存储和切换运行。

结 语

[1] 杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-719.

Method of Storage and Switching Running for Multiple NIOS Programs in EPCS

Luo Minghua

(China Coal Technology Engineering Group Chongqing Research Institute,Chongqing 400039,China)

In the paper,a method for Altera FPGA to store multiple NIOS II embedded programs into EPCS Flash and let them swtich to each other for running is proposed.Taking two embedded programs as the example,the program boot process,the specific method of the two program's storage and switch running are introduced.The experiment results show that the method is feasible.This method makes the FPGA with NIOS II soft core more convinient in program debugging and practical application.Especially for program remote update,it can be completed without destroying the original program,and therefore the security of the system is enhanced greatly.

FPGA;NIOS II;EPCS;program storage;reconfiguration;program boot

省部级-“矿用胶带机撕裂检测控制系统研究”;重庆市社会事业与民生保障专项项目(cstc2015shmszx90007)。

TN791

A