200 mm Trench MOSFET 管用硅外延电阻率管控

孙 健,刘 勇,谭卫东

(中国电子科技集团公司第 55 研究所,南京 211111)

200 mm Trench MOSFET 管用硅外延电阻率管控

孙 健,刘 勇,谭卫东

(中国电子科技集团公司第 55 研究所,南京 211111)

200 mm 重掺 As衬底的 MOSFET 外延片在后续芯片制程中,由于还需要经历高温环节 (大于 1100 ℃),因此衬底中 As的自掺杂效应将再次出现,从而使外延片边缘区域的电阻率降低明显。在外延过程中,需要将外延片边缘区域的电阻率有意控制略高于中心区域。在控制过程中通过引入Offset(差值) 的管理方法,确保外延层边缘 3 mm 区域与中心区域的偏差减小,从而实现片内管芯之间性能一致。

自掺杂效应;Offset-chart;高温烘烤工艺

1 引言

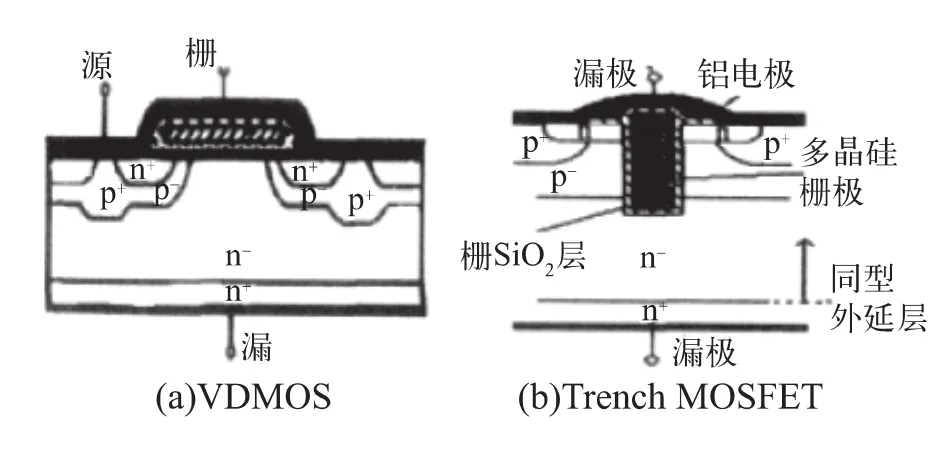

随着现代电子设备的小型化和高性能化,对功率半导体器件提出小体积和高效率的要求。其中功率MOSFET 作为功率半导体器件主体之一,被广泛应用于计算机、通讯、汽车以及消费电子领域,是分立器件和智能功率集成电路(SPIC)的重要组成部分。理想的功率 MOSFET 应当能够在关断状态时承受大的阻断电压,在开启状态时有小的正向压降,并且具有大的电流处理能力和较快的开关速度,从而减小其开关损耗[1]。但是在实际设计中必须兼顾各项指标,从而限制了功率 MOSFET 达到理想状态。为了提高功率MOSFET 的性能,国内外的研究者们在工艺条件和器件结构方面进行了不断优化和改进,其中首先是 H.W. Collins 等[2]人在保留早期平面型功率 MOSFET 原有优点的基础上,提出了 VDMOS(垂直双扩散型 MOS管),如图1(a)所示。为了进一 步 降 低导通电阻,D.Ueda 等 人[3]在 VDMOS 的 基 础 上 提 出 了 Trench MOSFET 结构,如图1(b)所示。相比 VDMOS,由于Trench MOSFET 结构中没有 JFET 这一寄生结构,因此可以进一步减小芯片尺寸,提高沟道密度,可大大降低导通电阻[4]。

图1 VDMOS 和 Trench MOSFET 结构示意图

由于 Trench MOSFET 具有以上的优点,在低压功率 MOSFET 领域中所占份额越来越重。其导通电阻主要由沟道电阻、外延层电阻和衬底电阻 3 部分组成[5],其中外延层电阻在整个导通电阻中占比超过 50%,是影响导通电阻的主要参数。加上其管芯尺寸较小,为了得到高良率和高一致性的管芯,对硅外延层内电阻率横向的均匀分布以及批次间电阻率的一致性提出了更高的要求。

200 mm 重掺 As衬底的 MOSFET 在后续芯片制程中,由于还需要经历高温环节(大于 1100 ℃),因此衬底中As的自掺杂效应将再次出现,从而使外延片边缘区域的电阻率降低明显。因此在外延过程中,希望将外延片边缘区域的电阻率有意控制略高于中心区域,确保在后续芯片制程中边缘区域与中心区域的电阻率值偏差减小,从而实现片内管芯之间性能的一致。

但是在外延片制备时,由于衬底杂质 As的气相扩散较重,尤其是在外延生长过程中,极易从硅片边缘扩散,并快速与化学反应还原出的 Si一并沉积在硅片边缘区域,形成外延层的杂质原子,从而将外延片边缘区域的电阻率拉低,很难满足外延后的芯片制程要求。如何有效控制外延片边缘的电阻率高于中心区域的整体趋势是本文研究的重点。

为了有效地控制硅外延片电阻率的片内分布和批次间分布,本文在常用的管控 X-chart和 R-chart的基础上,引入新的控制方法,从而有效管控电阻率的一致性。

2 200 mm 硅外延片电阻率测试 Pattern 选取

2.1 外延设备简介

本文中涉及的外延设备为美国 ASM 公司的E2000PLUS 单片外延系统。该外延设备每次外延 1片,相比一次多片外延炉,其优点在于减少了同炉次内片与片之间的负载效应等影响,加之该外延反应室体积较小,能够较精确地控制反应室内温度和气流分布,因此外延片片内的参数一致性优于多片外延设备。由于是单片外延,片与片之间的外延条件可重复性强,因此片与片之间的参数控制也优于多片外延炉。

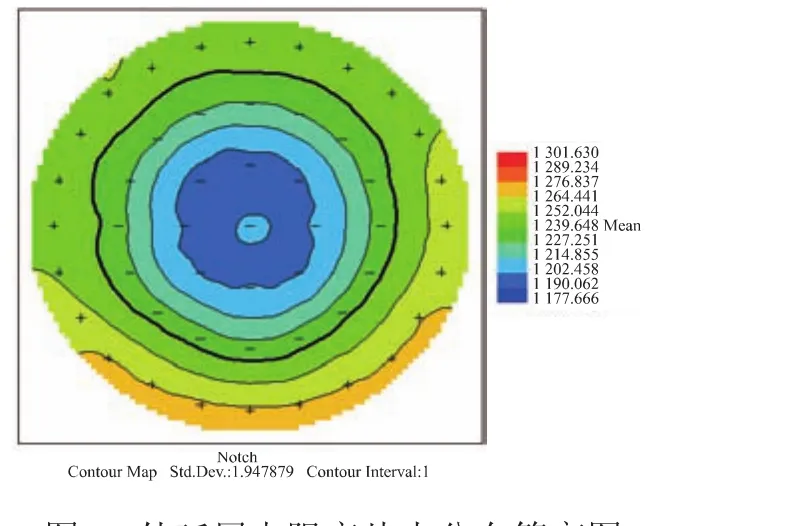

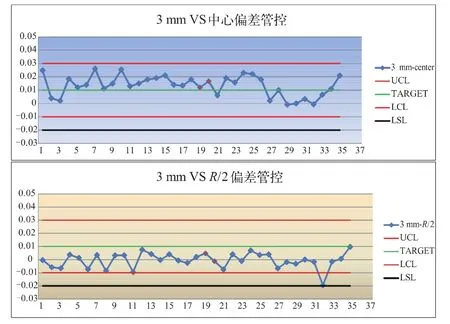

ASM 单片外延系统,外延片内的参数以中心点为圆心,呈同心圆式分布。通常情况下不同直径的圆之间外延参数有一定差异,而在同一个圆上的不同点,其外延参数基本一致,典型的外延层方块电阻率分布如图2所示。

图2 外延层电阻率片内分布等高图

2.2 外延层参数测试 Pattern 选取

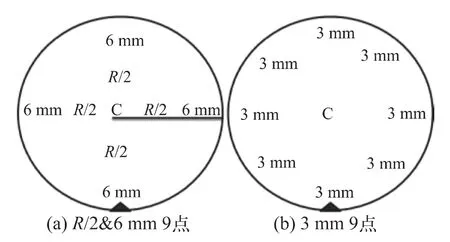

在外延层参数量测 Pattern 选取上,必须尽可能表征片内参数所有点的真实水平,即所有点的极差。由于 ASM 单片外延炉的外延层参数在片内有 2.1 节中的分布特性,因此电阻率测试选取两种 Pattern,第一种是 R/2&6 mm 9 点(即中心点 + 半径 4 个点 + 距边6 mm 4 个点),如图3(a)所示;第二种是 3 mm 9 点(即距边 3 mm 8 个点 + 中心点),如图3(b)所示。

图3 测试 Pattern 示意图

2.3 外延工艺控制

温度场调节:外延工艺上,由于 N 型外延层电阻率与温度呈正向分布,相对温度较高区域的电阻率也越高,反之电阻率越低。因此,首先需要将外延设备温度场分布趋势调节为中心区域低、边缘区域高。通过调节生长程序中控温模块的温度补偿,借助温控注入片进行监控,从而实现所需要的温场。

烘烤采用 1130 ℃高温烘烤工艺,并通入较大流量(60 slm)的氢气,目的如下:

(1)用 H2轰击衬底表面,去除衬底表面的自然氧化层;

(2)使衬底中的 As大量扩散出并被氢气带走,As原子在一定时间内扩散耗尽。

低温淀积:烘烤结束后,降温到 1100 ℃,通入SiHCl3、PH3和 H2进行化学气相反应,还原出来的 Si原子和 P原子沿着衬底的晶格方向进行排列,实现外延层生长。

3 外延层电阻率控制

3.1 X-chart和 R-chart

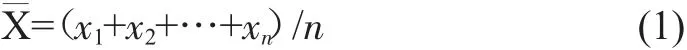

X表示子组的平均值:

n 为子组的样本容量,本文中 n=9 。

本文中 X 代表采用 R/2&6 mm 9 测试 Pattern,量测的 9 个点的电阻率平均值。因为 R/2&6 mm 9 测试Pattern 能够表征 wafer内约 94%的有效区域 (常规距边 3 mm 以外不做管芯),并且该区域内受测试不稳定性影响较小,因此在过程控制中使用电阻率的值,指导外延工艺掺杂量的调整。将量测的所有 X 进行 chart图管控,并制定相应的控制上下限,能够直观地监控电阻率值与目标值的差异和监控值的变化趋势。管控实例如图4所示。

图4 电阻率 X-bar管控实例

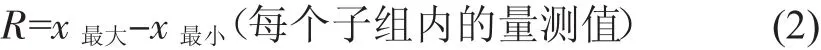

R表示子组的极差值:

本文中 R 值代表 R/2&6 mm 9 测试 Pattern,量测的片内9个点的极差值。

R 值反映片内该 9 点的离散程度,R 值越大,片内9 点越离散,反之越收敛,过程控制理论上要求将 R 值控制得越小越好。同时片间的R值代表片间的稳定性,理论上要求片间的 R 值不变,但在实际稳定生产时,R 值应该稳定在一定范围内。R 值的管控实例如图5所示。

图5 电阻率R值管控实例

3.2 Site-chart

Site 代表 R/2&6 mm 9 测试 Pattern,量测的片内 9个点全部在 chart图中显示,从而片内 9 点形成类似柱状的图形。Site-chart能够直观地监控到 9 个点的落点情况,出现有落在管控线以外的点时,触发 SPC 系统的报警。在过程控制中,要求子组内的9个点必须落在控制线以内,且不同子组间 Site 柱高度应该基本一致(柱子高度随 R 值的变化而变化),柱子整体在一条直线上(随着 X 波动)。Site 管控实例如图6 所示。

图6 电阻率 Site 管控实例

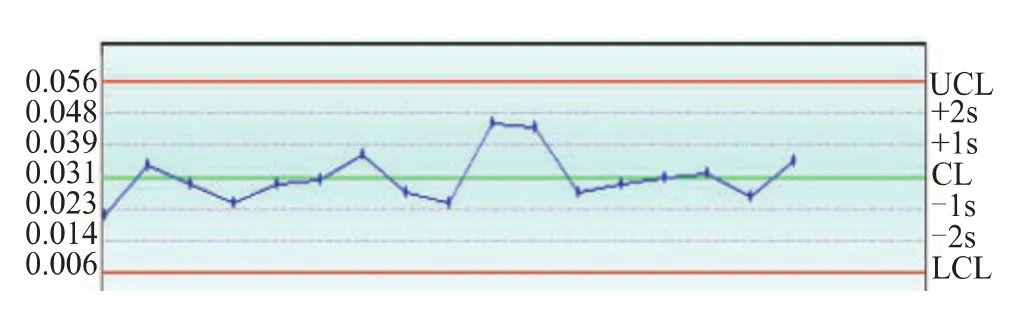

3.3 Offset-chart

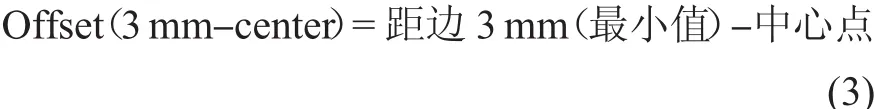

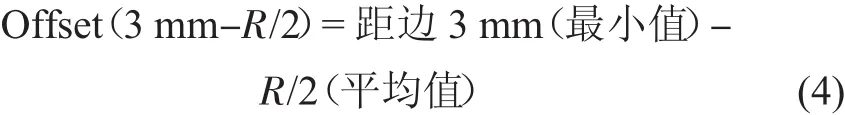

在常用的管控图中,无法实现外延片电阻率片内趋势的管控,因此本文引入 Offset(差值)的控制,本文的 Offset-chart包括以下两个管控参数:

即距边3 mm测试模式下,量测距边3 mm的 8个测试值中,取最小值减中心点的量测值。在实际过程控制中要求 0.03≥Offset(3 mm-center)≥-0.01,从而保证外延层边缘区域电阻率高于中心点。

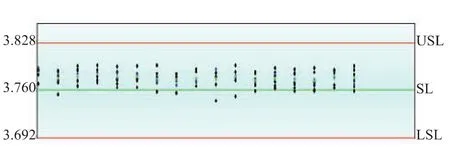

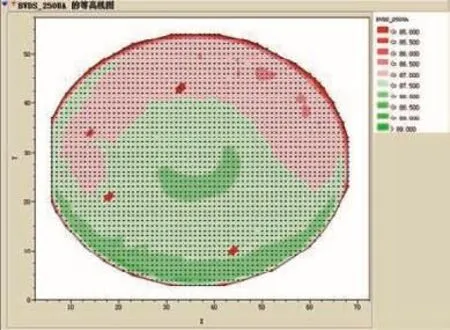

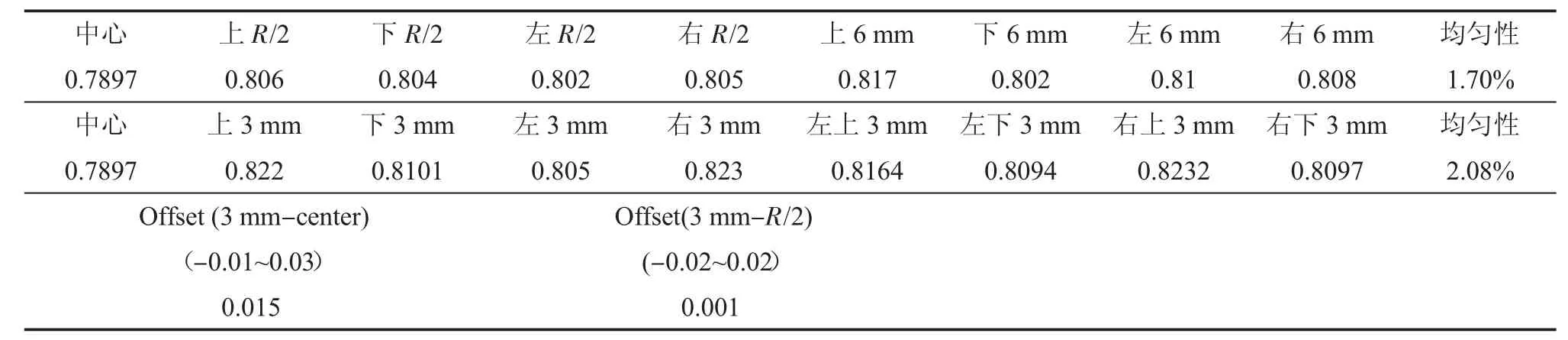

即距边3 mm测试模式下,量测距边3 mm的8个测试值中,取最小值减 R/2 的平均值。在实际过程控制中,要求 0.02≥Offset(3 mm-center)≥-0.02,从而保证外延层边缘区域电阻率高于 R/2。Offset管控实例如图7 所示。引入 Offset管控前外延片电阻率分布情况为中心电阻率高、边缘电阻率相对偏低,如表1 所示。器件 BV 分布图显示片内极差较大,边缘 BV 低,如图8所示。

图7 电阻率 Offset管控实例

图8 引入 Offset管控前 BV 分布图

引入 Offset管控后外延片电阻率分布情况为中心电阻率低、边缘电阻率相对提高,如表2 所示。

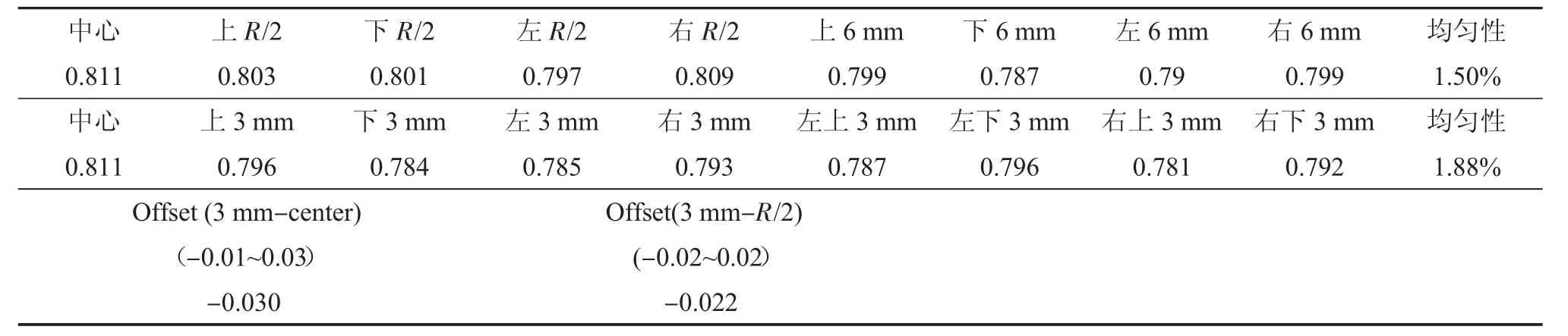

表1 管控前电阻率分布情况

表2 管控后电阻率分布情况

器件BV分布图显示片内极差明显改善,如图9所示。

图9 引入 Offset管控后 BV 分布图

4 结论

ASM E2000PLUS 单片外延系统生产 200 mm MOSFET 用硅外延片,结合该设备外延片片内电阻率分布的特点以及后续 Fab 制程的特点,在电阻率管控上除采用常规的均值和极差管控外,引入了 Site-chart和 Offset-chart两种管控方式,从而实现了对外延层电阻率进行片内电阻率所有点以及分布趋势的有效管控。客户端最终 Trench MOSFET 芯片参数一致性表现较优,其典型的电参数长期稳定在±2.5%范围内。

[1]Su Yan-fen,Liu Ying-kun.Advances in the Developmentof Trench MOSFET[J].Semiconductor Technology,2007,32(4):277-278.

[2]COLLINSHW,PELLYB,HEXFET.Anew powertechnology cutson-resistance,boots ratings[J].Electron Devices,1979, 17(12):36.

[3]UEDAD,TAKAGI H,KANOG.A new vertical power MOSFET Structure with extremely reduced on-resistance[J]. IEEE Trans Electron Devices,1985,32(1):2-6.

[4]苏延芳,刘英坤.Trench MOSFET 的研究与进展[J].半导体技术,2007(4):277-280.

[5]姚丰,何杞鑫,方邵华.一种新型低压功率 MOSFET 结构分析[J].半导体技术,2005,30(11):53-56.

意法半导体发布 2-40 A 1200 V SiC JBS 二极管

意法半导体 (以下简称 ST) 近期发布了一款 2-40 A 1200 V 的 SiC JBS 二极管,具有高转换率、高回收率、恒温特性,广泛用于碳化硅技术领域。

ST 表示,SiC 二极管工艺线生产的器件具有最佳的正向电压(VF最低),设计人员可通过使用低额定电流和低成本的二极管实现高有效性和可靠性的电路设计。因此,SiC技术有望向对成本更敏感的应用领域突破,例如光伏、工业马达驱动、家用电器和电源适配器等。

与此同时,性能导向型应用对 SiC 的效能、重量、尺寸和热性能都有极高要求。ST 的 SiC JBS 二极管通过低 VF达到效能优势,在蓄电池(OBC)和混动/电动(PHEV/EV)插电式充电桩等汽车设备领域具有竞争力。另一方面,该二极管在通讯、供电、高功率工业化开关电源(SMPS)、电动机、不间断电源(UPS)和大型光伏转换器等领域的电性能表现都非常好。该 SiC JBS 二极管 VF达到最低,还能降低器件工作温度,延长工作寿命。 (编译 李星悦)

原 文 链 接 :http://www.semiconductor-today.com/news_ items/2017/may/st_110517.shtml

新加坡科学技术研究院开发出可用于光学器件批量生产的混合硅激光器

在硅晶圆上生产半导体激光器一直以来是半导体行业的目标,这种制造工艺向来极具挑战性。近日,新加坡科学技术研究院 A*STAR 开发出一种新颖的制造方法,成本低廉、过程简便且可扩展性强。该混合硅激光器将 III-V 族半导体(如砷化镓和磷化铟)的发光特性与当前成熟的硅制造技术完美结合起来,可以将光子和微电子元件集成在单一硅芯片之中,从而获得价格低廉、可大批量生产的光学器件。其应用场景涵盖从近距离数据通信到高速远距离光传输在内的广泛领域。

A*STAR 研究院的 Doris Keh-Ting Ng 及其同事开发了一种生产混合 III-V 半导体和绝缘体上硅光学微腔的方法,大大降低了制造工艺的复杂性,使器件结构更加紧凑。此外,该工作首次使用了一种新型异质核配置和集成制造工艺,将低温 SiO2层间键合与双硬掩模、单光刻图案结合起来。

(编译 赵博)

原 文 链 接 :http://www.semiconductor-today.com/news_ items/2017/jun/a-star_190617.shtml

Control Method of Silicon Epitaxial Resistivity for 200 mm Trench MOSFET

SUN Jian,LIU Yong,TAN Weidong

(China Electronics Technology Group Corporation No.55 Research Institute,Nanjing 211111,China)

During the fabrication of200 mm MOSFET with Heavily-doped Arsenic,the high-temperature will cause the Arsenic ofsubstrate self-doped again,which may lowerthe resistivity offringe area ofthe EPIwafer. Resistivity of fringe area needs to be a little bithigher than thatof the center area during EPIprocess.With the offset controlling method,the deviation between 3 mm from edge of the EPI wafer and the center area are lowered to maintain performance uniformity within wafer.

self-doped effect;Offset-chart;H2-baked process

TN304.054

A

1681-1070 (2017)06-0036-05

孙 健(1980—),男,江苏泰州人,南京航空航天大学本科毕业,工程师,现在中国电子科技集团公司第 55研究所国盛公司从事硅外延生产质量管理工作。

2017-3-18