基于Nand Flash的星载综合数据固态记录系统*

杨海峰

(中国西南电子技术研究所,成都 610036)

基于Nand Flash的星载综合数据固态记录系统*

杨海峰*

(中国西南电子技术研究所,成都 610036)

在星载平台资源受限条件下,采用以FPGA+CPU为控制核心、Nand Flash为固态存储阵列的系统架构,实现了高速、大容量、高可靠的数据记录。针对传统双Plane操作与并行扩展对存储速度提升有限、芯片使用较多的问题,采用4级流水线方式控制Flash阵列。为解决标准传输协议传输效率低的问题,设计了一种自定义高速串行传输协议。为减缓空间辐射环境对存储数据的影响,采用了三模冗余、配置回读与部分重构等容错机制。对所提出系统进行的实验验证结果表明,该星载记录系统存储容量达36 Tbit,记录与回放速度分别达到16 Gbit/s与8 Gbit/s,传输误码率为10-12,传输包效率为96.7%,可作为通用存储系统以满足航天应用需求。

卫星有效载荷;固态记录系统;Nand Flash存储器;现场可编程门阵列;三模冗余

1 引 言

星载存储系统是航天飞行平台电子系统的重要组成部分,随着深空探测及载人航天等任务的大力发展,飞行器往往需要同时执行多种任务,探测任务的数据来源与复杂度增加,各类任务对星载存储系统的存储容量、存储管理、数据记录速率、数据回放速率、适应恶劣的空间环境的能力提出了更高的要求。同时,我国国土资源有限,难以在海外设置大量的地面接收站,更多依靠卫星过境时再将数据回放的方式,这样迫切需要一种可复用、扩展性强、容量大、存取速度快的星载数据存储设备。

美国国家航空航天局(National Aeronautics and Space Administration,NASA)与欧洲航天局(European Space Agency,ESA)等国外研究机构对星载固态存储设备开展了大量研究与实际应用,大多针对特定数据类型进行定制化设计,基本设计思想以单板甚至单处理芯片为核心,围绕单一数据类型进行设计,接口速度与芯片性能受限[1-4]。从航天任务的实际应用需求出发,目前国内外星载存储设备主要有以下一些问题:一是多元数据的综合化存储管理能力有待加强[5-7];二是采用并行扩展与双Plane读写技术,存储容量与速率提升较为困难[8];三是外部接口采用并行总线,硬件管脚占用较多,数据记录与回放速率较低[9];四是空间环境防护措施较为单一[10-11]。

为解决以上问题,本文以FPGA+CPU为中央控制核心,采用Nand型Flash为存储介质,并引入多元数据综合化存储体系、自定义高速串行传输协议,针对空间环境的特点设计了三模冗余、配置回读与部分重构机制等关键技术,在满足系统设计指标要求的前提下降低Flash芯片数量,解决星载设备中的大容量数据存储问题,完成数据的高速海量存储。

2 在轨数据存储需求分析

本固态记录系统主要为对地观测、测控、通信等载荷任务数据的大容量、高可靠存储提供支撑。各类载荷的数据种类众多,数据形式、保存周期、关键性各不相同。按对系统运行的影响及关键程度,划分为关键数据和普通数据两类数据。关键数据主要包含系统任务资源调度的参数文件、硬件配置文件、任务功能运行的信息库、功能应用执行的程序执行体等,需要长期、可靠的存储;普通数据主要包括状态监测数据和任务执行过程中产生的原始数据、载荷数据等两大类型,不会对系统运行造成影响,在任务前将根据存储资源需求进行清理。

在所有任务中,对地观测任务数据量最大。在分辨率为3 m时,对地观测任务的最高数据速率约为8.2 Gbit/s。若每轨对地观测任务开机10 min,按照平均工作时间计算,将产生约11.5 Tbit数据。

考虑数据可存储两天,同时考虑30%存储余量,则普通数据总存储需求为30 Tbit。关键数据存储主要考虑数据的可靠性,为防止辐照或其他原因对数据造成损坏而影响系统运行或任务执行,采用三模冗余(Triple Modular Redundancy,TMR)设计(即3块数据存储模块同时存储同样的数据,读出时进行判决输出)。本系统关键数据的存储容量要求30 Gbit以上,由于TMR设计,则每块数据存储模块的关键数据存储容量要求至少100 Gbit。考虑2倍的存储容量裕度和30%的降额损失(生命末期与坏块产生等影响),则每块数据存储模块的关键数据存储容量需求接近300 Gbit。

根据对有效载荷系统和任务过程数据需求的分析以及卫星总体的技术要求,主要指标梳理如下:

(1)总存储容量≥32 Tbit(含一个冷备份模块),存储介质选用高集成度、低成本的Nand Flash存储器;

(2)记录速率≥16 Gbit/s(双通道备份),回放速率≥8 Gbit/s,在进行数据存储时可以同时进行数据输出;

(3)数据记录传输的误码率≤10-12。

3 综合数据固态记录系统设计

3.1 系统总体架构设计

3.1.1 系统架构与模块设计

目前主流的星载记录系统有3种架构,即FPGA+DSP+存储阵列、FPGA+存储阵列、FPGA+CPU+存储阵列[12]。第一种架构在FPGA内实现存储阵列控制器设计,并可提供丰富的互连接口,DSP对于信号处理算法实现较强,但对系统的控制能力较弱;第二种架构无处理器的参与,对大容量存储系统的文件管理等操作需全硬件实现,设计难度大、通用性较差;第三种架构中,FPGA提供丰富灵活的接口,CPU可对系统提供操作系统支持,降低文件管理与开发难度,可便于星务管理系统的统一调度,因而本系统采用FPGA+CPU+存储阵列的架构。

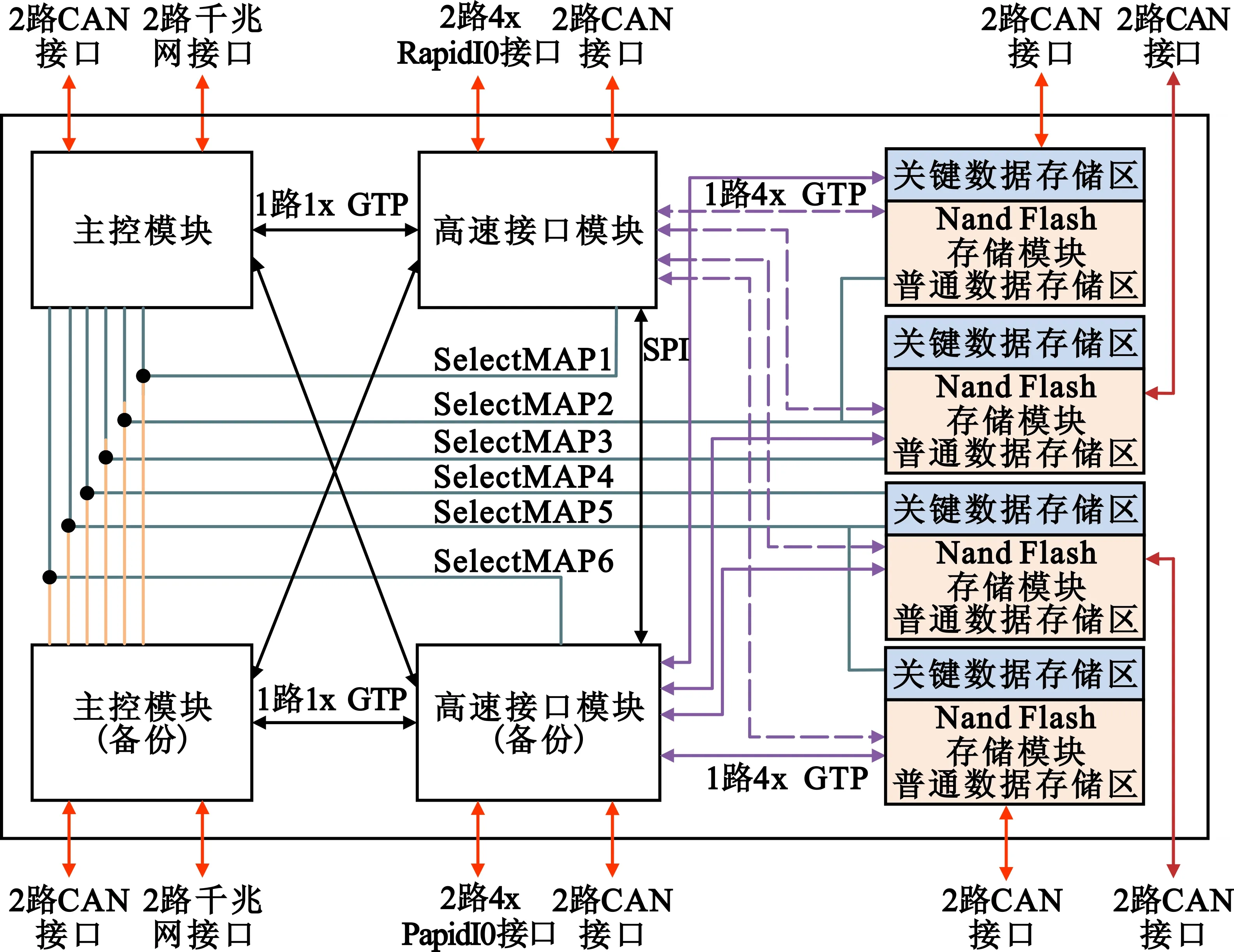

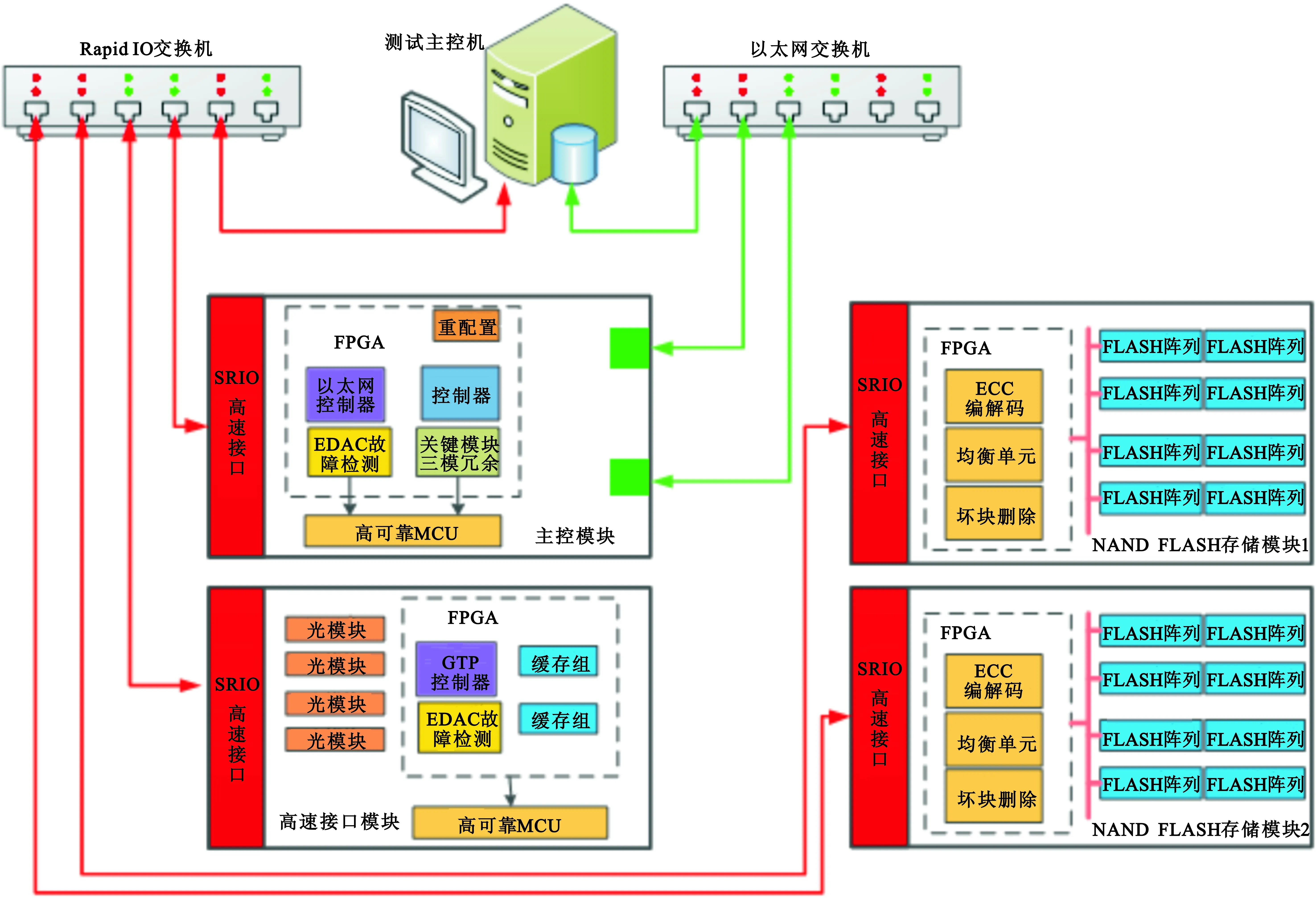

记录系统由8个模块组成,包括2块高速接口模块、2块主控模块、4块Nand Flash存储模块,所有模块均采用CPU+FPGA架构,CPU用于支持文件系统及接口控制等功能,FPGA便于硬件扩展与重构,模块符合VITA 78 SpaceVPX 6U空间标准规范,各模块互连架构如图1所示。

图1 综合数据固态记录系统总体组成图

在备份关系上,高速接口模块与主控模块采用1∶1双冗余备份设计;4块Nand Flash存储模块包含3块硬件冗余模块与1块备份模块,各模块的接口与硬件组成关系完全相同,以提高系统可靠性,总容量为36 Tbit。在互连关系上,高速接口模块与4块Nand Flash存储模块采用FPGA中内置的高速串行收发器GTP互连,并通过自定义高速串行传输协议进行数据的记录与回放。高速接口模块对外部载荷设备提供多路高速光纤SRIO接口,并支持SRIO交换架构,可与卫星平台其他载荷通过SRIO交换网络互连,提升系统互连的灵活性。高速接口模块与Nand Flash存储模块通过千兆以太网接口与主控模块互连,传输低速记录数据。高速接口模块与存储模块均通过两路互为备份的CAN总线与主控模块进行监控与健康管理等数据的交互,并在其控制下进行协同工作,完成数据的记录与回放功能。各模块的初始配置信息预置在Nand Flash存储模块的关键数据存储区,在系统发生软故障时,可通过在轨维护模式对系统进行软件恢复。

主控模块负责千兆网接口收发与综合数据固态记录系统的故障监控以及存储信息和目录信息管理。对外通过千兆以太网接口与其他设备进行数据交互,完成数据转存、通信以及配置文件的远程更新等功能,通过6路SelectMAP总线,对其他模块的FPGA进行回读检测和重配置。

高速接口模块具有3路4×光纤RapidIO高速串行接口,每路高速串行接口的数据传输速率为3.125 Gbit/s,主要完成光纤RapidIO高速接口数据的接收、缓存及分发,实现对外部载荷互连和对Nand Flash存储模块的数据传输。

Nand Flash存储模块由两组Flash阵列与相应的控制器组成。共分为两组 Nand Flash芯片,组内共用片选线,即全部并行连接,组外共用控制线,但不共用片选线,两组数据线以复用方式连接。每组阵列包含12片512 Gbit Nand Flash,则每块存储板的存储容量为12 Tbit,满足存储需求。关键数据存储空间是从12 Tbit容量中划分出300 Gbit存储容量。关键数据容量较小,且要求的速率不高,因此对关键数据采用更低Block容量的管理方式,以提高存储空间管理的精度,增加存储容量的利用率。

3.1.2 核心器件选型

FPGA、CPU、Flash存储阵列与缓存为本系统的核心元器件,其选型应考虑到空间环境的特点、实现系统指标所需的功能资源以及卫星平台机电热资源受限的共同约束。由于记录系统的规模较大,应在满足以上约束的条件下考虑元器件统型,以便于型号管理与元器件统型,尽量降低成本,具备经济可行性。

系统环境所使用的电子器件耐受电离辐射剂量能力依据载荷总体要求、飞行器轨道特性与文献[13]中的剂量深度曲线确定,计算出本系统关键元器件耐总剂量效应不低于15 krad(Si)。

各模块中的CPU主要为固态记录系统提供操作系统支持,同时为综合化的文件管理提供基础支撑,该类服务对CPU资源占用较低。基于操作系统和CPU对国产化的需求,考虑到传统宇航级CPU在性能与接口数量、种类上的限制,本系统选用龙芯3A CPU,通过增加壳体屏蔽厚度与器件升筛以适应空间环境。

各模块中功能资源使用最大的是FPGA资源,经实际设计综合后,每个高速接口模块包含2个4×RapidIO控制器、2个DDR2控制器、2个4×自定义协议高速串行接口控制器;每个主控模块包含2个Flash控制器、1路2×自定义协议高速串行接口控制器、1路4×自定义协议高速串行接口控制器。星载应用中多使用反熔丝或Flash型FPGA,以避免空间中的各种高强度辐射以及单粒子效应带来的影响,但反熔丝型FPGA仅能一次烧写,对调试测试等工作要求过高,且不能实现功能重构与系统扩展。Flash型与反熔丝型FPGA的逻辑资源受限,高速接口较少,市面可获得的型号无法满足本系统的要求。综合考虑,本系统选用型号为Virtex-5QV-XQR5VFX130的FPGA,其性能满足本系统要求。

根据前文所述,本系统将数据区划分为关键数据区与普通数据区。关键数据区Flash芯片采用3D-PLUS公司的具有抗辐照加固的3DFN128G08VS8308。普通数据区容量较大,若全部采用宇航级Flash芯片经济成本难以承受,且宇航级Flash芯片体积较大,无法将大量芯片在一块6U模块上布局,而将商用货架器件升筛加固在经济性和实现性上都是一条可行路线,因此采用Micron公司的MT29F512G08CUCABH3。选用3D-PLUS公司的非挥发性的磁性随机存储器(Magnetic Random Access Memory,MRAM)芯片3DMR4M08VS4428存储文件信息表与坏块信息等小文件。

3.2 数据存储流水线优化设计

就本系统而言,存储速度不低于16 Gbit/s,通过双Plane与并行处理后单芯片写入数据率约为368 Mbit/s,则至少需要42片Flash芯片并行才可达到要求。但是,42片Flash的容量为21.5 Tbit,远超单模块8 Tbit的需求,这就增加了设计成本,不利于星上集成。因此,需在以上操作下增加流水线优化技术,以提高存储速率。

根据Flash芯片的操作特点,充分利用芯片内部编程时间进行流水设计,可以大幅度提高数据的写入速度,即对一组Flash 芯片编程,不能进行其他操作时,可对另外一组芯片进行操作,原理如图2所示。通过查阅器件参数手册,每片Flash芯片包含4个Target,流水级数最高可达8级,当采用双Plane 操作时,本系统写入速度为(并联芯片数流水线级数页大小页个数)/(加载时间+写入编程时间)=(24×4×8 640×2)Byte/(90+1 300)μs=19 Gbit/s。通过以上分析,本系统单块存储模块最终采用24片Nand型Flash芯片,容量为12 Tbit,理论最高写入速度达到19 Gbit/s,3块主份存储模块容量达36 Tbit。由此可见,本系统采用4级流水操作控制Flash阵列时,相对于仅采用并行操作技术,节约了43%的芯片数量,且大大提高了写入速度,完全满足本系统的技术指标。

3.3 数据存储高速传输设计

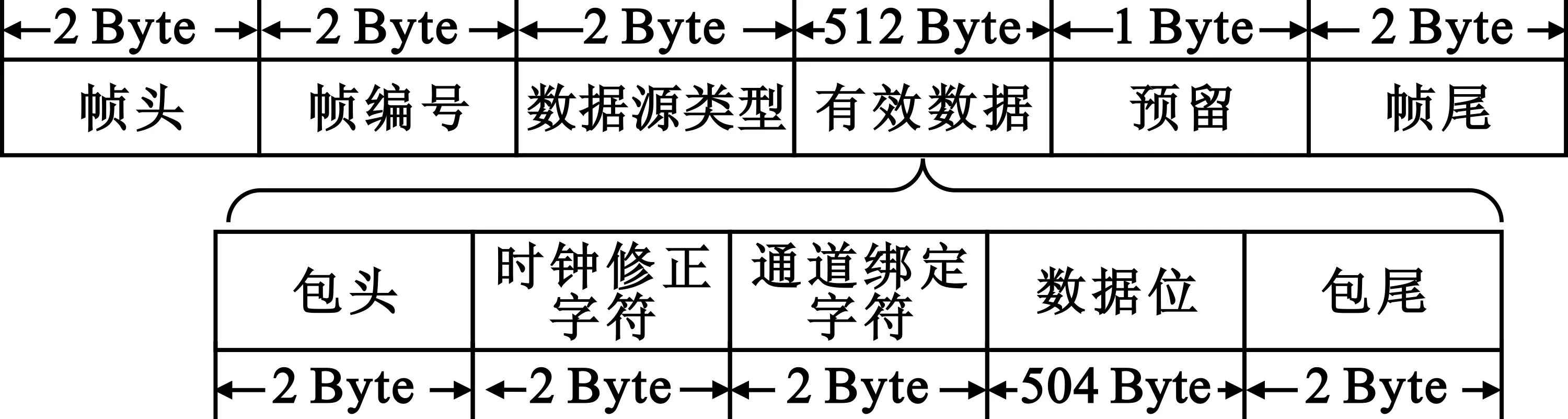

接口模块从外部SRIO接口输入的数据经转换后,通过GTP接口送入存储模块的GTP接口中。目前数据记录系统中常用的数据传输协议为SRIO或PCIE,其打包效率分别为92%~94%与82%(有效数据256 Byte下),在待传输数据较大时,两种标准协议将带来较大的延迟与传输效率降低,使星上记录系统可有效记录时间降低。因此,需设计一种低开销、可将任意传感器输入数据打包的自定义帧格式,以提升系统效率。

为保证来自天线孔径、图像传感器等数据源的数据能在统一格式下进行记录,对数据接口的格式编写了自定义协议。自定义协议形式如图3所示,由帧与包为单位组成。经计算,自定义协议的包效率(即数据位与包长之比)=504 Byte/521 Byte≈96.7%。

图3 自定义数据帧格式

3.4 抗单粒子效应与备份切换设计

3.4.1 关键数据TMR与电路级抗单粒子设计

对于关键数据,为防止辐照等原因对数据造成损坏而影响系统运行或任务执行,采用硬件TMR。在3个Nand Flash存储模块中划分出同样大小的空间作为可靠存储区,在文件写的过程中,主控模块同时对3个存储模块进行写操作,保存3份以增加可靠性;在回放过程中,主控模块对3个存储模块可靠存储空间的数据进行判决输出,根据判决结果,将出错的信息经过纠正后重新写回。系统采用EDAC故障检测点+ECC纠错编码和动态周期刷新3种手段综合应对单粒子翻转效应,并将3种方法对应的FPGA电路进行模块化设计,形成标准单元,如图4所示。其工作原理如下:

(1)主控模块通过SelectMAP接口对各模块FPGA进行配置信息回读检测或周期重刷新;

(2)MCU对关键器件的电流、电压信息进行检测,若发现电流异常则对相应模块复位,若异常情况严重则断电,以防闩锁,并进行自恢复控制;

(3)FPGA内部设置软件EDAC故障检测点、ECC纠错编码,实时监测FPGA内部运行状态,发现严重错误则对系统进行复位操作。

图4 抗单粒子翻转关键电路结构图

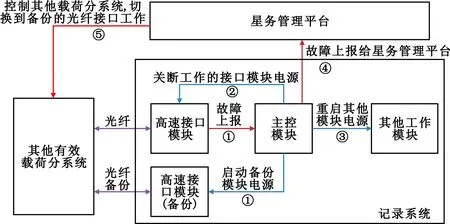

3.4.2 备份切换设计

本记录系统可靠性增强的冗余技术主要指在空间环境下记录系统模块内的器件发生不可恢复的故障(即功能失效)时,则进行相应的故障恢复策略。可以总结为两类:模块发生部件级故障时,则通过模块内的冗余措施(如接口冗余)或降额保证正常工作;模块整体失效时,将导致记录系统不能工作,则切换到备份模块工作。

以高速接口模块为例,记录系统工作时,高速接口模块内部控制模块实时检测故障,检测光纤接口、DDR2、GTP串行总线、RapidIO接口通信是否正常,且电源供电也能够实时检测。若发生故障,则通过CAN总线将故障上报给高速接口模块。高速接口模块发送命令,关断接口板电源,启动备份高速接口模块的供电电源。然后在存储主控模块的控制下,对所有工作的板卡进行重新复位。切换流程如图 5所示。

图5 故障切换流程示意图

区别于其他模块的切换,主控模块的切换会导致存储数据的目录信息丢失,从而导致之前存储的内容全部丢失。因此,主控模块及其备份板的目录信息需要及时进行同步更新,保证切换后目录信息仍然存在。所有存储任务的信息均存储于主控模块的MRAM存储器中,为保证主控模块与备份主控板中存储的目录信息同步,采用实时同步刷新的方式。当主控模块工作时,备份的主控模块CPU和MRAM也处于工作状态。当存储任务结束后,将任务信息存储于主控模块,同时通过CAN总线将信息传输到备份主控模块,更新备份主控模块的MRAM,从而保证主控模块工作切换时存储任务的目录信息不会丢失。

4 系统验证与分析

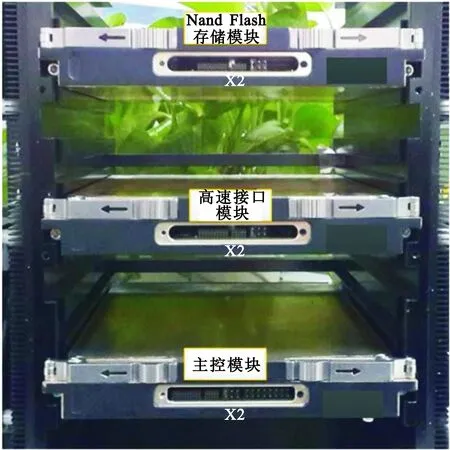

为验证本系统的基本性能,建立了测试平台,其实物图如图6所示。对记录系统进行了记录与回放的传输误码率测试;对关键数据进行了TMR备份存储与故障注入动态重构的测试。测试条件如下:PC机操作系统为Windows 7 64 bit,CPU为Intel(R) Core(TM) I7-3770K@3.4 GHz,内存为32 GB,Vivado HLx版本为2015.4,示波器型号为Lecroy(R) SDA 813Zi。被测系统由存储设备、远控测试软件组成,远控测试软件部署于测试机(PC机,含RapidIO仿真节点卡,通过PCI-E接口与CPU进行通信),通过千兆网与RapidIO交换设备分别与固态记录设备互连。测试系统组成如图7所示。

图6 星载综合数据固态记录系统原理样机实物

图7 测试系统组成框图示结构图

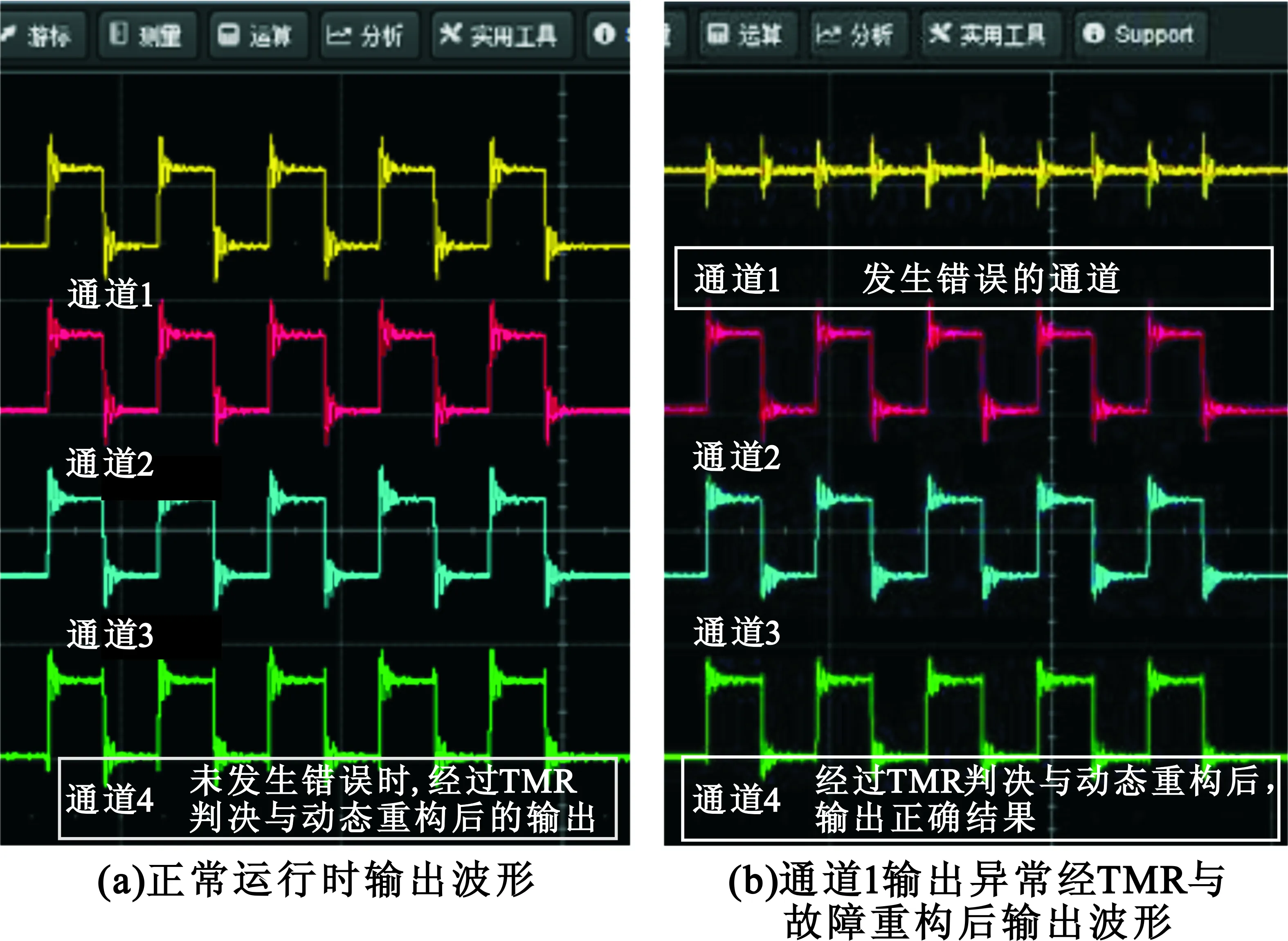

通过修改配置内容的方式来模拟单粒子翻转效应,结果如图8所示。图8中示波器通道1观测的是TMR中存储模块1的备份数据输出,通道2观测的是TMR中存储模块2的备份数据输出,通道3观测的是TMR中存储模块3的备份数据输出,通道4观测的是经过TMR判决与动态重构后判决器的数据输出。图8(a)内为系统正常运行时输出的波形,图8(b)为关键数据区发生错误时(通道1输出异常),经过TMR与故障重构后的数据输出波形。对比图8(a)与(b)中通道4的波形可以看出,当单个冗余设计故障时,启动配置控制器对数据错误对应的动态区域进行重配置,最终输出正确的结果。

图8 使用配置回读动态重构与TMR的测试结果

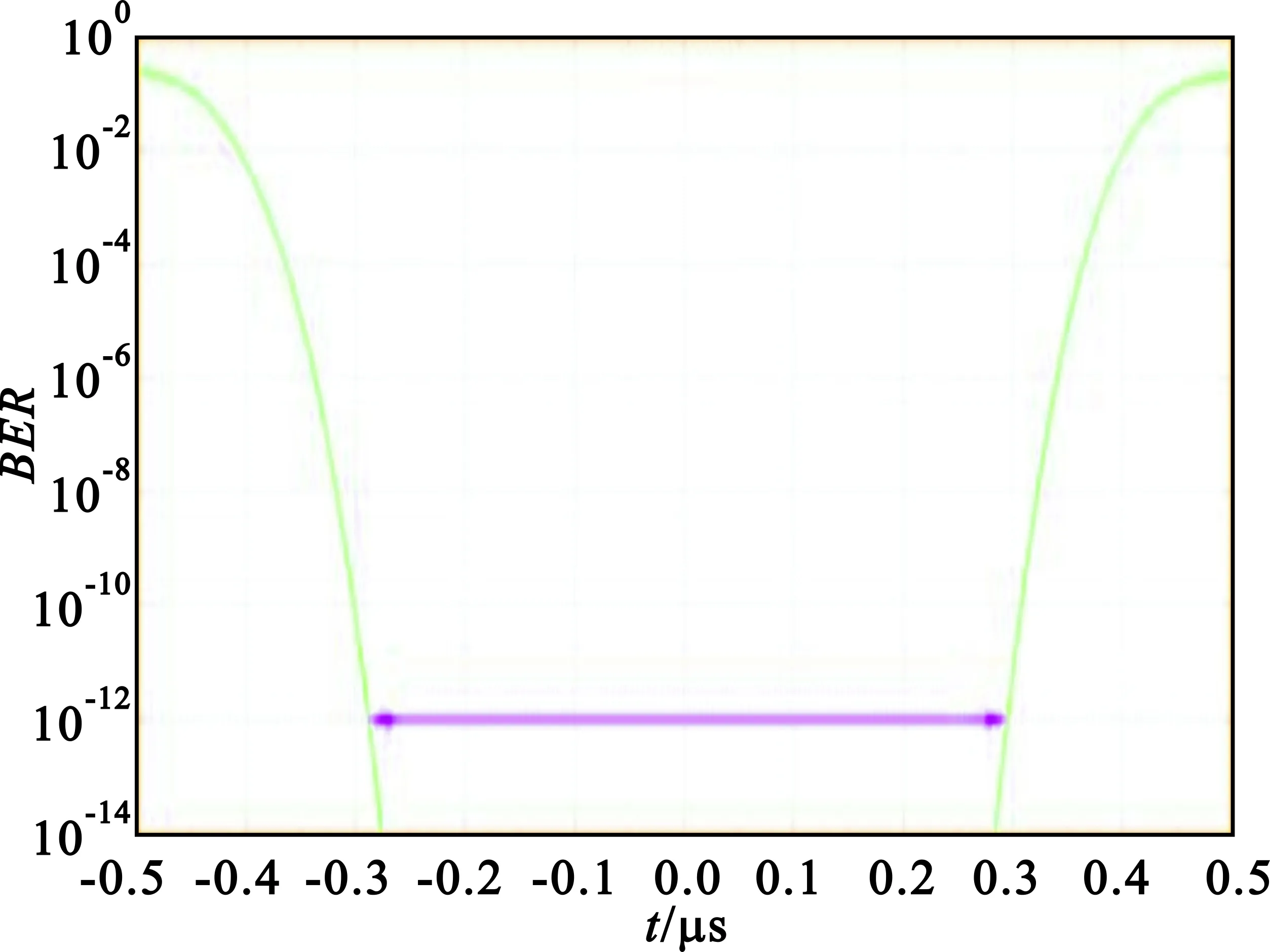

通过PC机以太网接口向综合数据固态记录系统发送数据记录指令,将Nand Flash存储模块写满,随后断电后再上电,将数据读出,以验证记录与回放数据的正确性、速度与误码率。经过48 h拷机测试,结果表明,记录与同时回放速度分别达到16 Gbit/s与8 Gbit/s,具体性能如表1所示。由图9的眼图与误码率浴盆曲线可以看出,记录系统自定义协议高速传输误码率为10-12。由表2可知,传输速度可稳定在约16 Gbit/s;包开销较低,包效率约为96.7%,性能超过目前常用的RapidIO(92%~94%)总线以及PCIE(82%)总线的包效率,达到系统使用要求。

(a)眼图

(b)浴盆曲线

数据量/Gbit记录时间/ms记录速率/(Gbit·s-1)回放时间/ms回放速率/(Gbit·s-1)0.531.415.9262.87.961.062.315.97125.37.982.0125.116.00249.78.013.0187.416.01374.58.01

5 结 论

本文重点针对卫星存储设备的整体设计,改变了传统星载存储系统以各个独立模块为基本单元构建系统设计的方法与思路,采用多元数据综合化存储体系,设计了一种星载综合化海量数据存储系统,存储容量达到36 Tbit,记录与同时回放速度分别达到16 Gbit/s与8 Gbit/s,传输误码率为10-12。本系统具有如下特点:

(1)引入4级流水线方式控制Flash阵列,有效提升了存储速度,节省了芯片使用数量;

(2)在统一的自定义协议控制下,可将图像传感器、微波孔径与载荷数据源进行传输与存储,提高了数据传输效率与标准化程度;

(3)采用了三模冗余、配置回读与部分重构和EDAC数据纠错等容错机制,通过综合化设计的主控模块对系统内各模块实现健康管理与故障恢复功能,减缓空间辐射环境对存储数据的影响。

与Sentinel-2卫星上存储系统MMFU相比,存储器容量提升了5.33倍,记录与回放速度分别提升了96.3%与14.3倍,包效率与传统的SRIO及PCIE协议相比分别提升了4.7%与14.7%,可以作为通用存储系统以满足航天应用需求。

[1] 宋琪,李姗,朱岩. 针对Flash存储特性的航天器大容量固态存储技术[J].电子设计工程,2015,23(4):169-175. SONG Qi,LI Shan,ZHU Yan. Key technologies of Flash-based solid state recorder for aerospace applications[J].Electronic Design Engineering,2015,23(4):169-175.(in Chinese)

[2] 张峰. 基于Nand flash阵列的高速存储技术[J].电讯技术,2013,53(1):68-71. ZHANG Feng. High-speed large-capacity recording based on Nand flash arrays[J].Telecommunication Engineering,2013,53(1):68-71.(in Chinese)

[3] 张峰,吴钦章,任国强. 基于SATA的高速CCD存储方案设计[J].半导体光电,2010,31(5):782-786. ZHANG Feng,WU Qinzhang,REN Guoqiang.A high-speed method of CCD image data storage system based on SATA[J].Semiconductor Optoelectronics,2010,31(5):45-48.(in Chinese)

[4] 王烨,张峰,李燕斌. SATA高速存储的FPGA实现[J].电讯技术,2012,52(11):1801-1804. WANG Ye,ZHANG Feng,LI Yanbin. A high-speed recording system of SATA based on FPGA[J].Telecommunication Engineering,2012,52(11):1801-1804.(in Chinese)

[5] 宫婧,王文君.大数据存储中的容错关键技术综述[J].南京邮电大学学报(自然科学版),2014,34(4):20-25. GONG Jing,WANG Wenjun. Fault tolerance technology for big data storage[J].Journal of Nanjing University of Posts and Telecommunications(Natural Science Edition),2014,34(4):20-25.(in Chinese)

[6] JIANG G Z,HAN B,GAO Y B,et al.Review of 40-year earth observation with Landsat series and prospects of LDCM[J].Journal of Remote Sensing,2013,17(5): 1033-1048.

[7] ARVIDSON T,GOWARD S,GASCH J,et al.Landsat-7 long term acquisition plan: development and validation[J].Photogrammetric Engineering and Remote Sensing,2006,72(10): 1137-1146.

[8] SASADA T,ICHIKAWA S,SHIRAKURA M. Mass data recorder with ultra-high-density stacked memory for spacecraft[C]//Proceedings of 2005 IEEE Aerospace Conference.Big Sky,MT,USA:IEEE,2005:1-8.

[9] SHIMADA M. JAXA earth observation programs digest[J].IEEE Geoscience and Remote Sensing Magazine,2014,2(2):47-52.

[10] DURNA M,URHAN H,TURHAN O,et al.A new generation on-board computer and solid state data recorder suitable for spacewire platforms[C]//Proceedings of 2007 3rd International Conference on Recent Advances in Space Technologies.Istanbul,Turkey:IEEE,2007:429-432.

[11] STAEHLE M,CASSEL M,LONSDORFER U,et al.Sentinel-2 MMFU: the first European mass memory system based on NAND-Flash storage technology[C]//Proceedings of 2011 Data System in Aerospace(DASIA 2011).Albuguerque,USA:ASTRIUM,2011:90-94.

[12] 陈斌,沈卫华,朱岩,等. 嫦娥二号卫星大容量存储器设计[J].航天器工程,2011,20(5):99-104. CHEN Bin,SHEN Weihua,ZHU Yan,et al.Design of solid state recorder for Chang'e-2 orbiter[J].Spacecraft Engineering,2011,20(5):99-104.(in Chinese)

[13] BLANSETT E L,KALB J L,THAYER G E,et al.Sandia-Xilinx Virtex FPGA SEU experiment on the international space station[J].Accident;analysis and prevention,2010,44(1):97-103.

A Comprehensive Data Solid State Recorder Based onNand Flash Memory for Spacecrafts

YANG Haifeng,CHAI Lin,HU Jianping

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

In order to realize the high-speed,large capacity,high reliability data recording system under the condition of the limited resources of satellite platform,the FPGA+CPU is chosen as the core control unit,and the system uses the Nand Flash as solid state memory chips. To address the problem that the traditional dual plane operation and parallel expansion have limited storage speed and more chips,the 4-stage pipeline is introduced to control the Flash array. To solve the low data transmission efficiency of standard transmission protocol,a user-defined high-speed serial transmission protocol is designed. To reduce the influence of the space environment on the data storage,such tolorance mechanisms as triple modular redundancy(TMR),configuration read back and partial reconstruction are introduced. Test of a prototype demonstrates that the storage capacity is up to 36 Tbit,recording and playback speeds reach 16 Gbit/s and 8 Gbit/s,respectively,and the error rate is 10-12,the transmission packet efficiency is 96.7%. This comprehensive data solid state recorder can be adopted as a universal storage system to meet the demand for aerospace applications.

satellite payload;solid state recording system;Nand Flash memory;field-programmable gate array(FPGA);triple modular redundancy(TMR)

10.3969/j.issn.1001-893x.2017.06.017

杨海峰,柴霖,胡建平.基于Nand Flash的星载综合数据固态记录系统[J].电讯技术,2017,57(6):716-723.[YANG Haifeng,CHAI Lin,HU Jianping.A comprehensive data solid state recorder based on Nand Flash memory for spacecrafts[J].Telecommunication Engineering,2017,57(6):716-723.]

2016-11-22;

2017-04-06 Received date:2016-11-22;Revised date:2017-04-06

中国西南电子技术研究所技术创新基金项目(H15017)

TN802

A

1001-893X(2017)06-0716-08

杨海峰(1985—),男,四川成都人,2008年于西南交通大学获通信工程专业工学学士学位,2014年于中国科学院光电技术研究所获工学博士学位,现为工程师,主要研究方向为航天器有效载荷总体技术、航天综合化电子系统、大规模相控阵、微波光子系统及测控通信系统总体技术等。

Email:haifeng_ioe@163.com

*通信作者:haifeng_ioe@163.com Corresponding author:haifeng_ioe@163.com,柴 霖,胡建平