基于CCSDS协议的中频信号源设计与实现

谷雨 王成华 朱秋明 钱太阳 王芳

摘要:针对深空通信的复杂环境,设计了一种基于CCSDS协议的中频信号源系统,可产生多种基于CCSDS协议的深空通信信号。该系统上位机采用LabWindows虚拟仪器开发环境,通过PCI接口与集成了DSP和FPGA单元的信号板卡互联,采用正交调制算法,在不改变硬件电路的情况下实现多种调制方式和参数。经测试,该系统输出精准、稳定,各项参数均符合设计要求,可实现对CCSDS协议的信号模拟。

关键词:深空通信;CCSDS协议;中频信号源;虚拟仪器;正交调制

中图分类号:V423.4+5;P228.4 文献标识码:A 文章编号:1673-5048(2017)02-0071-06

0引言

随着通信技术的不断进步,人类对深空探测的范围和技术要求不断提高,对通信质量的要求也越来越高,传统的地面无线通信模型无法适应深空通信环境。随着越来越多的国家加入到深空探测的活动中,人类在深空探测中更加需要统一的标准来实现多航天器之间的通信和控制。因此,NASA、ESA等主要空间国家联合组织成立了空间数据系统咨询委员会(CCSDS),迄今为止已有200多个空间任务采用了该协议体系进行遥测遥控、科学数据、图像等信息的传输,是未来深空探测通信的发展方向。

本文介绍了一种基于CCSDS-211系列通信协议的用于深空通信的信号源,该信号源所产生的中频调制信号的各项参数均参考CCSDS-211系列通信协议,符合深空通信应用环境,适用于深空通信系统的研究和开发。

CCSDS-211系列协议规定了6种调制方式,分别为BPSK,QPSK,OQPSK,GMSK,FM和PM,以及12种数据速率,分别为1Kb/s,2 Kb/s,4Kb/s,8 Kb/s,16 Kb/s,32 Kb/s,64 Kb/s,128Kb/s,256 Kb/s,512 Kb/s,1 Mb/s,2 Mb/s。该信号源根据协议规定全部实现了以上调制方式以及数据速率,以供深空通信研究使用。此外,为了适应不同的信道带宽,还提供了3种滚降系数,分别为0.25,0.5,0.75。该信号源载波频率为70MHz,配合混频器使用可将输出提高到UHF频段,供更多实验研究情况使用。

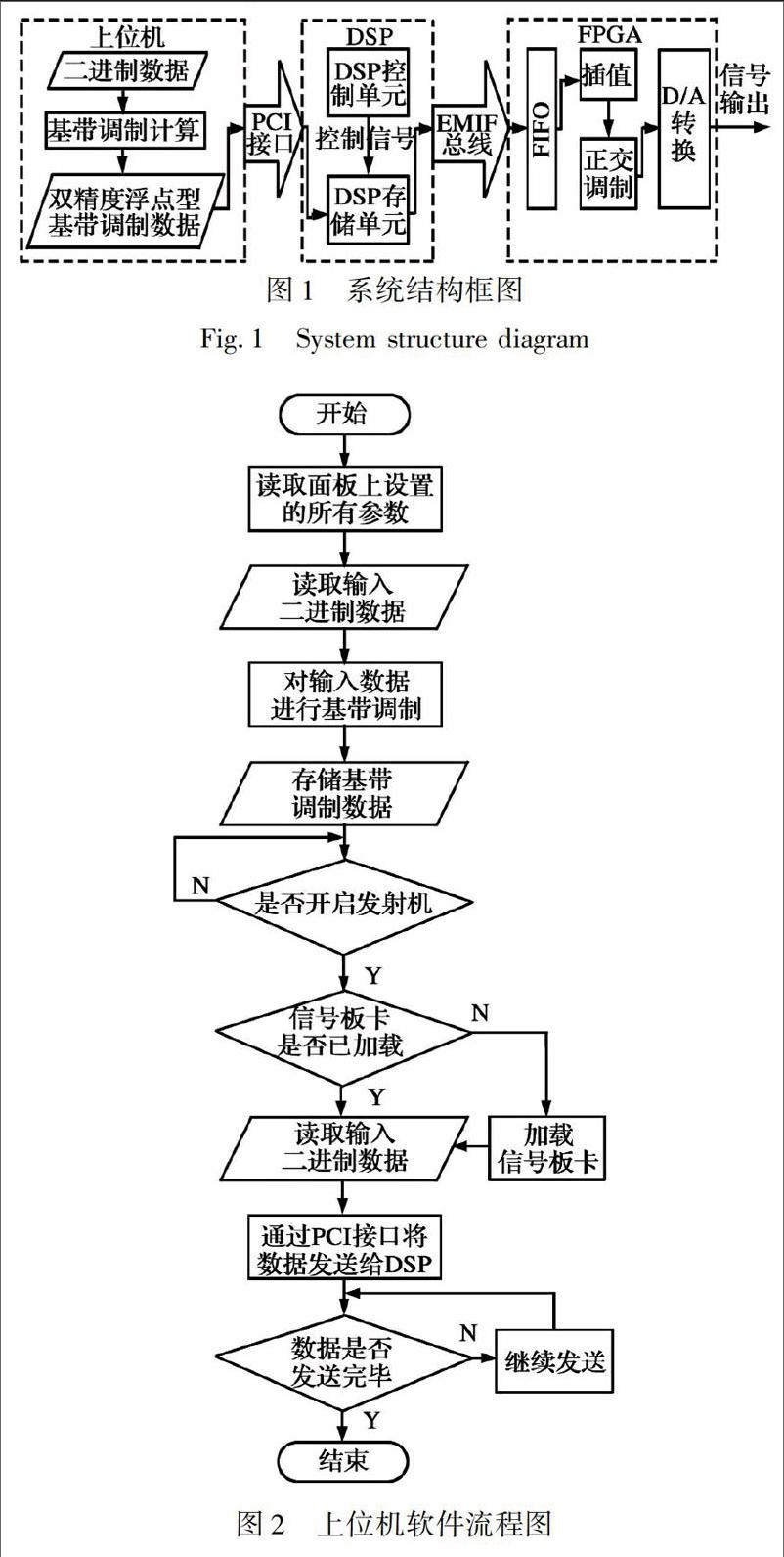

系统由上位机软件和硬件信号板卡两部分组成,数据源经过软件的计算后通过PCI接口传递至信号板卡,经过上变频后通过D/A转换模块得到模拟信号,如图1所示。其中上层软件安装在工控机中,DSP,FPGA,D/A转换模块等位于信号处理板卡上,通过PCI接口与上位机相连进行数据通信与控制。

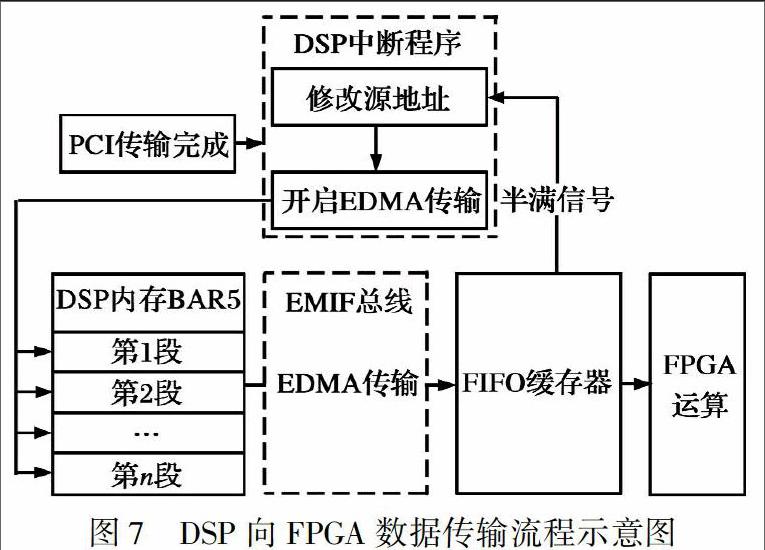

上位机软件起到对整个系统的控制作用,相当于传统硬件信号源的操控面板,同时还进行部分计算工作。因此,系统软件采用适用于虚拟仪器开发的LabWindows/CVI环境编译实现。上位机软件算法流程如图2所示。

在上位机中,用户可以选择输入数据,配置信号源的输出参数,如调制方式、数据速率等。当软件启动后,先读取设置的各项参数和输入数据文件。输入的二进制数据经过脉冲成型、基带调制和插值等运算获得I,Q两路的基带调制数据。此时的数据为双精度浮点数型,需对数据进行定点化转换为16位的short int型的整型数据,以便信号板卡处理。上位机软件调用WinDriver驱动,将这些数据通过PCI接口传递到信号处理板卡上DSP模块控制的存储单元中,再将这些数据通过EMIF总线传输给信号处理板卡上的FPGA单元,经过FPGA运算电路,即可得到所设置的中频信号的模拟量输出,信号源循环发送用户输入的数据直至关闭信号源。

2系统关键技术

2.1调制算法

由于系统需要实现多种调制方式,因此,为了不改变硬件结构且能实现多种不同的调制方式,系统采用了正交调制算法,见图3。在正交调制的过程中加入插值滤波器,可通过改变插值倍数来变换数据速率,以实现12种数据速率的切换。平方根升余弦滤波器可通过脉冲成型实现无码间干扰的通信,同时还可实现3种不同的滚降系数。

QPSK信号可以看作是对两个正交的载波进行多电平双边带调制后再叠加所得的信号,其正交调制的表达式为

(1)式中:I(t)为I路基带调制信号;Q(t)为Q路基带调制信号;载波角频率ωc=2πf。对于本系统,载波频率fc=70 MHz;采样频率fc=160 MHz。

QPSK调制时,先将输入的二进制序列转换为I,Q两路的双极性码,然后对该双极性序列进行脉冲成型和插值滤波,使I,Q两路基带信号采样率达到16 Mb/s。两路基带信号再分别与两路正交的载波相乘,相加后即可得到QPSK调制信号。

BPSK调制时,Q路输入全Q,就可以在不改变硬件电路的情况下,在正交调制系统中实现单路的幅度调制。OQPSK调制时,只需在两路信号经过平方根升余弦滤波器后,将Q路信号延迟半个码元周期,再进行插值滤波、上变频并相加。

GMSK调制即高斯最小频移键控,在MSK(最小频移键控)调制器之前插入一个高斯低通预调制滤波器。GMSK的正交调制表达式为

通常将B与Ts的乘积作为设计高斯滤波器的重要参数,本系统采取BTs=0.3的高斯滤波器进行预滤波。GMSK正交调制时,将二进制码元数据转换为双极性码后通过高斯滤波,再通过插值滤波将数据插值到16 Mb/s,并經过积分获得相位信号φ(t),此相位信号分别取余弦值和正弦值,即分别为I,Q两路的基带信号,经过上变频和相加即可获得GMSK调制信号。

对于FM调制,系统采用先对双极性码进行BPSK调制,再进行FM调制的方式,其表达式为

对于PM调制,系统采用先对双极性码进行BPSK调制,再进行PM调制的方式,其表达式为

2.2多数据速率

根据CCSDS-211协议,系统需要实现12种数据速率,可以通过插值的方式实现,插值分为两个部分,首先在上位机软件中将数据的采样率插值到16 Mb/s,然后再在FPGA中对数据统一进行10倍插值,得到160 Mb/s的数据。这样FPGA从FIFO缓存器读取数据时可一律采用16 Mb/s的时钟读取。在软件内插值时,插值的倍数越低,使得同一符号内的数据点数越少,在同一时间内FPGA读取相同数据数的情况下,FPGA所获得的符号速率就会越高,即数据速率越高;反之,插值倍数越高,数据速率越低。插值倍数N可表示为

在上位机软件内也采用两级插值滤波方式,将二进制码元转换为双极性码后,依次通过脉冲成型滤波器和插值滤波器,脉冲成型也是一个插值的过程,可在消除码间干扰的同时将数据插值到所需的数据速率。通过这种两级插值的方式可获得更高的插值倍数,系统第一级插值采用平方根升余弦滤波器或高斯滤波器,第二级插值采用积分梳状滤波器(CIC滤波器),如图5所示。

平方根升余弦滤波器具有消除码间干扰的功效,本系统有8倍和16倍两种插值倍数以及0.25,0.5和0.75三种滚降系数的6种不同参数的平方根升余弦滤波器。CIC插值则采用2倍、4倍、8倍、16倍、32倍、64倍、128倍、256倍、512倍、1 024倍共10种插值倍数。通过这些不同插值倍数的级联组合,获得不同的插值倍数,使得插值后的数据在FPGA的FIFO中以16 Mb/s的时钟读取以后所得到的数据速率与所设置数据速率一致。对于GMSK调制,需要先经过8倍插值的高斯滤波器,然后再通过CIC插值滤波器。

例如,BPSK,FM和PM调制2M数据速率时,只需要对二进制码进行8倍脉冲成型;1K数据速率时,先通过16倍脉冲成型滤波器,然后再通过1 024倍CIC插值滤波器,即可通过级联获得16 384倍插值。对于QPSK和OQPSK,由于系统采用正交调制,需要在I,Q两路进行插值,因此插值倍数为其他调制方式同速率下的2倍。

2.3硬件系统设计

系统硬件部分由DSP和FPGA两个模块组成,DSP模块与上位机之间通过PCI接口连接,DSP模块与FPGA模块之间通过EMIF总线连接,DSP起到数据搬移的作用,同时传递控制信号。

通过DSP的桥接将连接上位机的PCI接口和连接FPGA的EMIF接口通过映射联系起来,实现不同速率、不同位宽的接口间数据的有效互传。上位机与DSP以EDMA方式通过PCI接口传输数据,其数据传输过程如图6所示。上位机通过中断向DSP内存BAR0写入三个控制信息:待传输数据块起始地址、数据块长度、传输开始标志位。传输开始标志位的初始值为0,当上位机将传输开始标志位修改为1后,DSP跳转到传输开始中断内,配置EDMA传输参数,读取待传输数据的起始地址、长度,计算EDMA传输次数以及最后一次传输长度,设置首次EDMA传输的源起始地址、目的起始地址以及数据长度,EDMA首次传输开始。PCI接口总线的位宽为32位,因此传输完的数据以32位整型存储在DSP内存中,每个数据包含2个数据点。当传输完成后,DSP进入EDMA传输完成中断,根据传输次数和每次传输长度修改源起始地址和目的起始地址,再次配置参数进入第二次EDMA传输。当最后一次EDMA传输完成后,DSP跳转到向FPGA进行数据传输的中断。

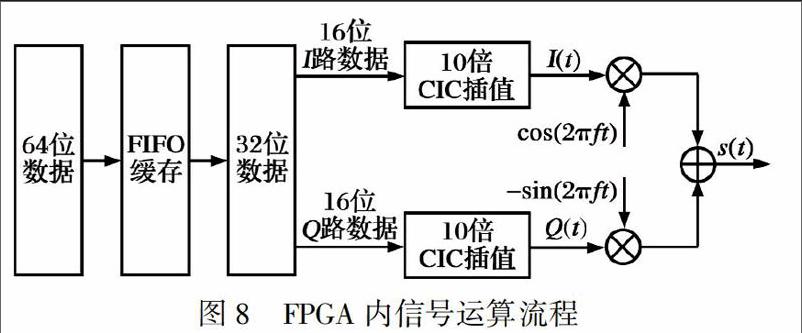

向FPGA的EDMA数据传输通过EMIF总线来进行,具体传输过程见图7。当上位机向DSP的传输完成后,DSP跳入向FPGA传输数据的中断程序中,配置EDMA传输参数,设置传输源地址、目的地址和数据长度并开始第一次传输。FPGA的FIFO缓存器写入深度为4 096,写宽度为64 bit,即最大可写入32 768字节的数据;读取宽度为32bit,半空控制信号触发值为1 500,即当数据少于6 000字节时,DSP会收到FIFO半空中断信号;DSP每次EDMA传输数据量为20 000字节。当FIFO中有数据以后,FPGA便开始从中读取数据,当FIFO中数据少于半空信号触发值时,DSP收到半空信号进入下一次EDMA传输中断,开始传输下一段数据再发送20 000字节的数据,此过程一直循环直至收到停止信号。当需要关闭发射机时,置发射机开闭参数PCS_EDMAStart值为2,此时DSP停止向FPGA传输数据的EDMA传输中断,信号源便不再产生信号。

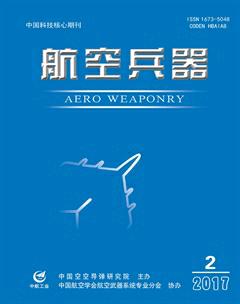

PCI总线宽度为32位,EMIF总线宽度为64位,因此,将FIFO的输入位宽设为64位,输出设为32位。数据从FIFO读出后,将每个32位数据取低16位即为I路信号,高16位为Q路信号。然后分别对两路信号进行10倍CIC插值,得到采样率为160 MHz的信号。再将两路信号分别与载波频率为70 MHz、采样频率为160 MHz的正余弦信号相乘并相加,即得到经过正交调制的中频调制信号,其在FPGA模块的运算流程如图8所示。该中频信号经D/A模块,即得到循环发送的模拟中频信号输出。

3测试结果

测试系统主要由一台工控机组成。中频输出信号可外接示波器和频谱仪,还可以接入混频器,将该中频信号源的输出提高到UHF频段,以模拟深空环境下的通信信号。

通过示波器和频谱仪对输出信号进行测试,输出信号的时域和频域波形如图9所示,由上至下依次为BPSK,QPSK,0QPSK,GMSK,FM,PM调制的时域波形和频谱图。经测试,信号时域波形包络平滑稳定,无毛刺;信号频谱图符合调制方式特征,主瓣宽度與数据速率和滚降系数相符合,且输出稳定可靠,符合设计指标和参数要求。

4结论

系统采用LabWindows/CVI环境进行开发,缩短了开发时间,降低了开发难度,提高了系统的可操作性。另外,系统采用正交调制方法,当需要对系统功能进行调整时,底层硬件系统无须进行任何改动,只需适当升级上位机软件,有效提高了系统功能的灵活性。