基于FPGA的AFDX交换机内嵌ES处理模块的设计与实现*

刘 达,王 勇,李炳乾,张 琦

(1.空军工程大学航空航天工程学院,西安 710038;2.解放军95357部队,广东 佛山 528226)

基于FPGA的AFDX交换机内嵌ES处理模块的设计与实现*

刘 达1,王 勇1,李炳乾1,张 琦2

(1.空军工程大学航空航天工程学院,西安 710038;2.解放军95357部队,广东 佛山 528226)

在航空电子全双工交换式以太网(AFDX,Avionics Full Duplex Switched Ethernet)的交换机中,内嵌终端节点系统(ES,end system)处理模块是连接外部终端与调度模块之间的关键部分。基于ARINC644规范第7部分,提出符合该规范的AFDX交换机内嵌ES处理模块的设计方案,采用软硬件协同设计方法对ES处理芯片进行设计与实现,并搭建平台进行测试验证,测试结果表明,所设计的ES处理模块能够达到ARINC664协议性能要求。

航空电子全双工交换式以太网,交换机,终端节点系统,现场可编程门阵列,软硬件协同设计

0 引言

随着计算机技术、通信技术和网络技术的高速发展,为了满足各种复杂飞行条件下安全飞行,必须提高机载数据总线传输的可靠性和稳定性。ARINC664规范是航空电子技术委员会审议通过的新一代机载以太网标准,该规范第7部分定义了一个名为航空电子全双工交换式以太网(AFDX,Avionics Full Duplex Switched Ethernet)的高确定性、高可靠性的机载数据交换网络[1]。AFDX作为一种新型的数据总线,传输速率可达100 Mbit/s,已成功在空客A380飞机上率先使用。随着我国“大型飞机”项目的启动,研制出我国自己的新型机载数据通信网络平台已成为一个紧要而迫切的任务[2]。其中,AFDX交换机内嵌ES功能是对AFDX网络进行配置管理的关键。

本文在深入理解ARINC664协议基础上,结合AFDX交换机实际设计情况,提出一种交换机内嵌ES处理模块的设计方案,该芯片主要基于FPGA进行设计,并采用软硬件协同设计方法对其硬件部分和软件部分进行详细说明,通过搭建测试平台对ES处理模块进行性能测试,测试结果表明所设计的ES模块符合ARINC644规范。

1 AFDX网络

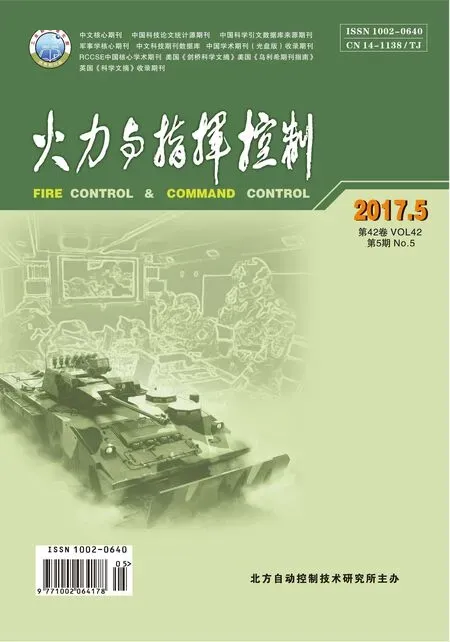

AFDX的拓扑结构为星型,由交换机、AFDX终端系统和AFDX互连线等几部分组成,如图1所示。为了保证系统的冗余特性,每一个终端系统与一个交换机之间不仅有一条直接、双向的连接,同时还与另一个交换机之间保持第2条双向连接。端系统与交换机之间或两交换机之间都通过全双工链路连接。每台交换机连接端系统的数量由交换机的端口数和实际情况决定。拓扑结构如图1所示[3]。

图1 AFDX拓扑结构图

交换机是AFDX网络的核心组件,主要承担数据交换任务。其中,内嵌ES模块是AFDX交换机设计中的一个重要模块,它提供了一种交换机与外界通信的途径,提供了对信息包的协议封装,对AFDX网络配置管理和端口定义等功能。另外内嵌ES功能也为其他上层应用提供统一应用接口[4]。

2 FPGA的选型

在本设计中,考虑到交换机内部运行环境的特殊性和复杂性,对芯片的工作温度和稳定性要求很高,普通商业级的FPGA无法胜任,必须采用工业级的FPGA。STRATIX II系列FPGA具有丰富的逻辑和布线资源、大量的存储器资源、支持各种标准的I/O,可以满足接口卡的资源需要。经过反复比较,最终 选 用 了 Altera公 司 的 STRATIX II系 列EP2S60F48414芯片。该器件核心工作电压为1.2 V,90 nm工艺、9层走线,高达60 440个LE,3种可供选择的内嵌RAM块,6个可编程锁相环和36个DSP模块,可完成极其复杂的时序与组合逻辑电路功能,满足了ES处理芯片的设计需要。

3 ES处理芯片总体设计

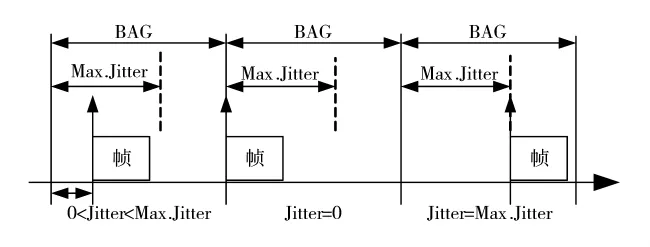

作为ES核心处理芯片,FPGA实现了AFDX协议栈特有的除冗余管理以外的全部虚链路层功能,如虚链路调度、流量整形等。ES处理芯片的组成如图2所示,本文设计的处理芯片采用了软硬件协同设计[6]的方法,包含了处理芯片的硬件分区结构和软件分区结构。

图2 内嵌ES处理芯片结构图

3.1 硬件分区设计

图2的上半部分为硬件结构,主要包括:

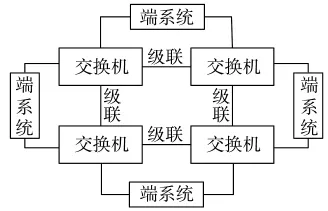

①调度器:ES虚拟链路中对虚拟链路进行整型的关键,每个虚拟链路的带宽分配需要考虑到最小带宽分配间隙(BAG)、虚拟链路可以传递的最大帧长度(Lmax)以及虚拟链路的最大抖动边界(Max. Jitter)3个条件的限制。BAG是以两个相继帧的起始位之间的间隔来确定的,范围为BAG=2k ms(0≤k≤7)。抖动是指从开始的BAG到第一个虚拟链路分配的最大分配带宽传输的帧之间的间隔。两者关系如图3所示。

图3 BAG与Jitter之间的关系

②媒体访问控制器:在发送信号时,通过CPU的调度程序和调节器的控制,负责从虚拟链路发送数据缓存中读取数据,按照AFDX协议的数据格式发送给媒体独立接口(MII)。在接收信号时,一旦收到数据,MAC通过媒体独立接口从物理层获取数据,进行AFDX协议的解析,并将其传递到冗余管理器[9]。总体设计如下页图4所示。

③NIOSⅡ处理器:NIOSⅡ处理器主要完成的功能:发送信号时,负责发送帧的指令调度。接收信号时,负责为每个流入帧确定虚拟链路并分配给帧合适的虚拟链路队列。在软件设计中,NIOSⅡ处理器必须执行以下任务:

①启动时配置系统

②调度发送帧

图4 媒体访问控制器设计

NIOSⅡ处理器将监视存储在虚拟链发送数据存储器中的各个流入虚拟链路的帧,确定发送的最优顺序(帧传输的实际时间留给调节器)。帧的调度由以下某个或多个参数确定:

●所发送的帧接收顺序;

●所服务的虚拟链路数目;

●队列下N个帧的长度和虚拟链路分配;

●每个虚拟链路队列的负荷;

●每个虚拟链路的可传输标志状态;

●每个虚拟链路带宽分配间隙计时器的值。

③接收帧的多路分解

NIOSⅡ处理器负责确定接收到的帧是否有效,以及拒绝冗余通道重复收到的有效帧。当接收到第一个有效帧并将其传递到系统后,其他同个序号的帧将被忽略。

3.2 软件分区设计

图2的下半部分是软件分区,主要包括:初始化模块、主控模块、AFDX协议控制模块、中断管理模块、存储管理模块和错误管理模块。其中,初始化模块负责初始化信息,主控模块负责对其他软件模块进行管理。AFDX协议控制模块负责控制AFDX数据帧编解码速度及各硬件模块之间的交互;存储管理模块负责对片上系统各个存储器的访问与控制;中断管理模块实现系统软硬件中断的处理;另外,通过错误管理模块监视系统的错误信息,并据此对主控模块进行相应的调整及处理。

下面主要对存储管理模块、总线模式寄存器与总线状态寄存器进行详细设计。

3.2.1 存储管理模块

主要有:①数据接收存储器:包含接收冗余管理器处理后的接收帧;

②虚拟链路接收数据存储器:包含按虚拟链路分离后的接收帧;

③虚拟链路发送数据存储器:包含通过网络发送给每个虚拟链路的帧;

④配置存储器:包含所有指定到终端的配置参数;

⑤FLASH:包含FPGA配置数据及断电时存储NIOSⅡCPU的程序及数据;

⑥SDRAM:包含NIOSⅡCPU运行时的程序、数据存储器。

3.2.2 总线模式寄存器

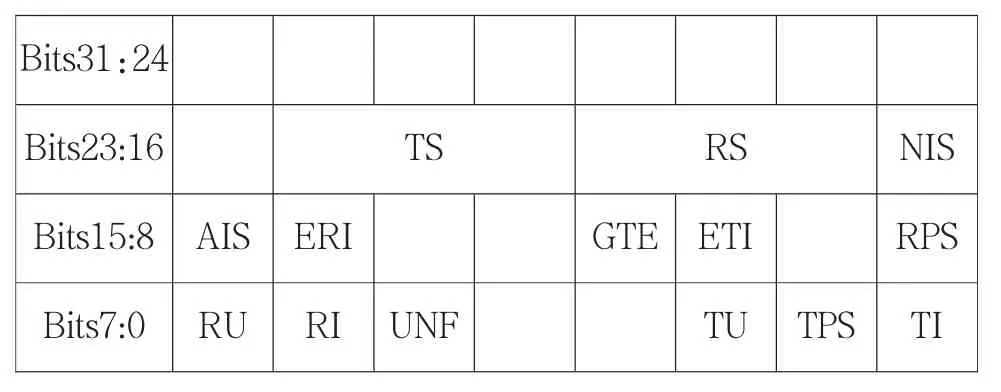

总线模式寄存器CSR0的格式如表1所示:

表1 CSR0格式

总线模式寄存器(CSR0)各个域的具体定义如下[9-10]:

①描述符字节分类方式(DBO)

DBO为1,表明总线模式为Big-endian模式;DBO为0,表明总线模式为Little-endian模式。

②传输自动轮检(TAP)

如果对TAP写入一个非零值,处在暂停状态下运行的IP核就会自动执行一轮传输描述符轮检,当描述符可用时,传输进程就会切换到运行状态。一旦描述符为主机所标识,传输进程将保持暂停状态。

③猝发传输的长度(PBL)

表示在一次DMA处理中可以传输字数的最大值。传输字数可允许的数值为:1,2,4,8,16,32。

④高/低位优先原则(BLE)

选择数据缓存时字节存储排序方式,1表示高位优先原则,0表示低位优先原则。

⑤描述符略过长度(DSL)

表明在环状结构下连续两个描述符之间字符的数目。

⑥总线调解配置(BAR)

1代表传输与接收进程再访问总线时有相同的优先级;0代表智能调解,接收优先级高过传输优先级。

⑦软件复位(SWR)

设定这一位为1会使所有触发器复位。

3.2.3 总线状态寄存器(CSR5)[11]

其格式如表2所示。

表2 CSR5格式

①传输进程状态(TS)

000:停止或复位传输指令;

001:运行,取出传输描述符;

010:运行,等待传输结束;

011:运行,从主机存储中将数据缓存传输到FIFO;

100:保存;

101:运行,安装信息包;

110:暂停,FIFO下限溢位或不可用描述符;

111:运行,结束传输描述符。

②接收进程状态(TS)

000:停止或复位传输指令;

001:运行,取出接收描述符;

010:运行,在预取下一个描述符之前等待接收信息包安装结束;

011:运行,等待接收信息包;

100:暂停,接收缓存不可用;

101:运行,结束接收描述符;

110:保留;

111:运行,将数据从FIFO转到主机存储。

③正常中断(NIS)

该 位 是 CSR5.0,CSR5.2,CSR5.6,CSR5.11,CSR5.14的逻辑或。仅当非屏蔽位才能影响NIS,对该位写1可以清除中断,写0没有影响。

④非正常中断(AIS)

该位是CSR5.1,CSR5.5,CSR5.7,CSR5.8,CSR5. 10的逻辑或。仅当非屏蔽位才能影响AIS,对该位写1可以清除中断,写0没影响。

⑤接收进程终止(RPS)

接收进程进入停止状态时被置位。

⑥接收缓存不可用(RU)

置位表明下一个接收描述符为主机所控制,而对IP核不可用。RU设定后IP核进入暂停状态,直到主机改变其对描述符的控制时才切换到接收描述符进程。

⑦接收中断(RI)

置位表明完整一帧的接收已结束,此帧已被传输到接收缓存。

⑧发送下限溢位(UNF)

置位表明再一次传输中传输FIFO已为空。传输进程切换到暂停状态

⑨发送缓存不可用(TU)

置位表明下一个接收描述符为主机所控制,而对IP核不可用。TU设定后IP核进入暂停状态,直到主机改变其对描述符的控制时才切换到发送描述符进程。

⑩接收进程终止(TPS)

发送进程进入停止状态时被置位。

4 ES模块测试

4.1 测试方案

针对ES处理芯片的设计,本文采用两个终端系统通过交换机进行数据传输,对ES模块进行测试,测试主要目的是看ES是否能发送、接收数据,波形是否正确,以及是否符合ARINC664标准规范要求等,系统测试连接方案如图5。

测试使用华力创通的 AFDX网络分析仪HWA-ATAP-4。它是一款AFDX网络数据采集分析工具,适用于AFDX网络数据流量在线采集、监测、数据记录、在线/离线分析、统计等需求,为AFDX技术研究、设计及故障定位提供必要的解决方案。对交换机的以太网电气性能验证和一致性的测试通过Agilent公司的实时示波器DSO9254A和其配备的以太网一致性测试工具包、测试夹具实现。

图5 系统测试连接图

4.2 测试过程

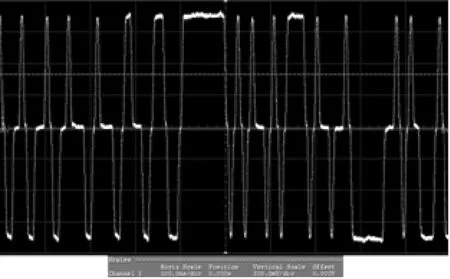

按照测试方案正确连接后,启动示波器内的以太网一致性测试软件Infiniium,并正确设置测试参数。示波器能自动完成测试并生成详细的测试报告。用示波器测得的典型波形如图6所示。

图6 ES数据传输典型波形

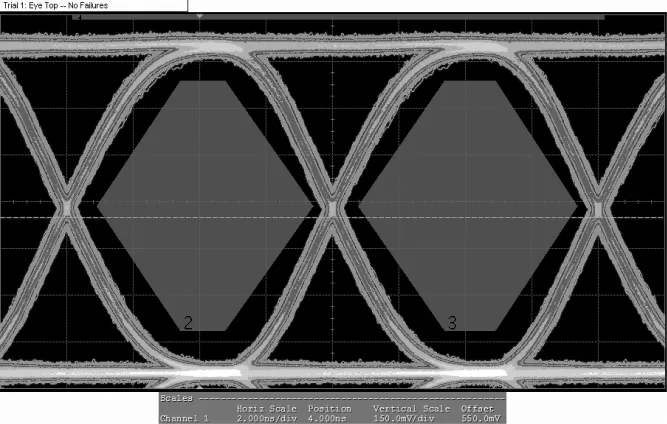

通过观察发现电压峰值略有偏大,下面先对噪声和码间串扰进行测试,观察其情况,如图7所示。

通过观察可知,眼图轨迹清晰,信号能顺利通过,总体性能良好,但“眼睛”张口略有偏大,这是由于电压偏高造成的,后期将对变压器进行设置,调整电压值。

图7 眼图测试

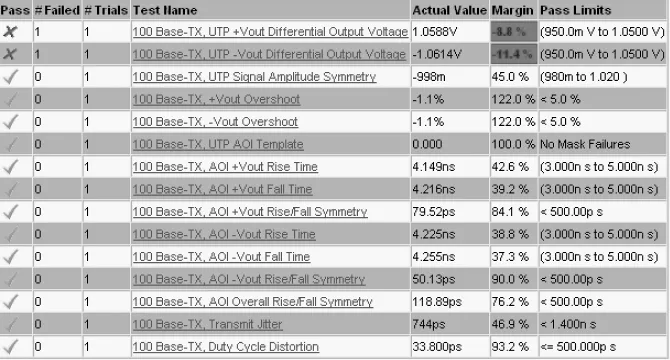

测试分析报告中,除了电压值以外,抖动、回波损耗等参数的测试都能顺利通过,结果符合预期设想,报告汇总如图8所示。

图8 测试结果总汇

5 结论

通过示波器对交换机ES端口大量的测试表明,该交换机在使用本文设计的内嵌ES处理模块的条件下能够实现100 Mbp/s的数据传输,波形符合AFDX规范。电压峰峰值略有偏大,但不影响ES模块整体性能,下一步将对电压模块进行调整,满足电压要求。

[1]支超有.机载数据总线技术及其应用[M].北京:国防工业出版社,2009:466-471.

[2]刘俊恩,张延园.嵌入式网管系统的设计与实现[J].微电子学与计算机,2009,26(7):234-236.

[3]郭利锋,王勇,白焱.AFDX交换机的队列整形调度研究[J].计算机工程,2011,37(24):58-60.

[4]张明.AFDX交换机内嵌ES的设计与验证[D].西安:西安电子科技大学,2013.

[5]王鹏,姚明旿,鲍民权.基于FPGA的航空全双工以太网交换芯片[J].计算机工程,2008,34(23):261-263.

[6]陆佳华,江舟,马岷.嵌入式系统软硬件协同设计实践指南[M].北京:机械工业出版社,2013.

[7]王绮卉.AFDX核心交换技术的研究与实现[D].西安:西安石油大学,2010

[8]尹路,王勇,郭利峰.基于FPGA的AFDX协议处理芯片设计[J].计算机工程与应用,2011,47(21):65-66.

[9]CHARARA H,FRABOUL C.Modeling and simulation of anavionics full duplex switched ethernet[C]//Advanced Indus2trial Conference on Telecommunications,Service Assurancewith Partial and Intermittent Resources Conference,2005.

[10]CHARARA H,SCHARBARG J L,ERMONT J,et al. Methods for bounding end-to-end delays on an AFDX network[C]//The 18th Euromicro Conference on Real Time Systems(ECRTS’06),2006.

[11]J.GRIE CHARARA H,SCHARBARG J L,ERMONT J,et al.Methods for bounding end-to-end delays on an AFDX network[C]//The 18th Euromicro Conference on Real Time Systems(ECRTS’06),2006.

[12]U.Analyse et evaluation de techniques de commutation Ethernet pour I’interconnexion des systemes avioniques[D].INP-ENSEEIHT,France,2004.

Design and Implementation of Embedded ES Processing Module for AFDX Switch Based on FPGA

LIU Da1,WANG Yong1,LI Bing-qian1,ZHANG Qi2

(1.School of Aerospace Engineering,Air Force Engineering University,Xi’an 710038,China;2.Unit 95357 of PLA,Foshan 528226,China)

In AFDX (Avionics Full Duplex Switched Ethernet) switch,the embedded ES processing module is the key part to connect external terminal with scheduling module.Based on the seventh part of ARINC644 standardize,the design scheme of embedded AFDX switch ES processing module is put forward,which is designed mainly with the Hardware-Software Co-design method,and the platform is built to test and verify performance.The test results show that the designed ES processing module can meet the requirements of the ARINC664 protocol performance.

AFDX,switch,ES,FPGA,hardware-software co-design

TP302

A

1002-0640(2017)05-0150-05

2016-02-18

2016-05-17

中国航空工业集团预研基金资助项目(619010601)

刘 达(1992- ),男,山东淄博人,硕士研究生。研究方向:航电计算机与网络。