基于扫描链修改的低功耗测试方案

张培明,商 进,李晓龙

(1. 黑龙江工程学院 电气与信息工程学院,黑龙江 哈尔滨 150050;2. 无锡职业技术学院 控制技术学院,江苏 无锡 214121)

基于扫描链修改的低功耗测试方案

张培明1,商 进2,李晓龙1

(1. 黑龙江工程学院 电气与信息工程学院,黑龙江 哈尔滨 150050;2. 无锡职业技术学院 控制技术学院,江苏 无锡 214121)

芯片测试过程中存在的高功耗问题是制约芯片测试发展的难题,针对此问题,提出一种新的低功耗测试方法。该方法通过插入异或门,将扫描链中的部分D触发器用T触发器代替,同时采用遗传算法对测试结构进行修改和测试向量重排序,为了保证故障覆盖率和故障仿真的正确性,对测试数据进行转换,从而降低由于节点电压跳变所导致的电平翻转次数,达到降低测试功耗的目的。根据部分ISCSAS 89基准电路的实验结果表明:该方法符合预期目标,平均功耗相对于未采用该方法前降低51.26%。

扫描链;测试向量重排序;遗传算法;低功耗测试

与集成电路技术快速发展相对应的是其测试过程中测试功耗越来越高。集成电路测试功耗主要由动态功耗和静态功耗组成[1-2]。在现有工艺条件下,电路的测试功耗主要为动态功耗,测试模式下消耗的该种功耗已经远远超过工作模式的消耗量[3]。因此,如何降低测试过程中的测试功耗,已经成为集成电路设计和制造中的关键问题[4-6]。针对这个问题,本文在可测性设计方案下,提出一种基于扫描链修改的低功耗测试方法,以解决测试和生产中面对的过高功耗问题。

1 动态功耗分析

1.1 动态功耗来源

集成电路中的功率消耗通常用下述公式[7]计算

(1)

式中:Pst为测试方式下各节点逻辑状态静止时通过漏电流引起的静态功耗,Psc为节点内部晶体管瞬间导通时引起的动态功耗,Pd为节点电压发生跳变时节点电容的充放电功耗。

上述三种功耗中,Pd在测试过程中占主导部分,约为总测试功耗的85%,这样,在测试功耗分析过程中,通常只考虑动态功耗Pd而忽略其它功耗[8-9]。

当集成电路在两种稳定状态之间变化时(即由1→0或由0→1),将产生动态功耗Pd。Pd由两部分组成,分别为充电和放电功耗PC以及瞬间的导通功耗PT,即Pd=PC+PT[10]。其中:

(2)

而

(3)

(4)

故

(5)

而瞬间导通功耗为

(6)

式中:

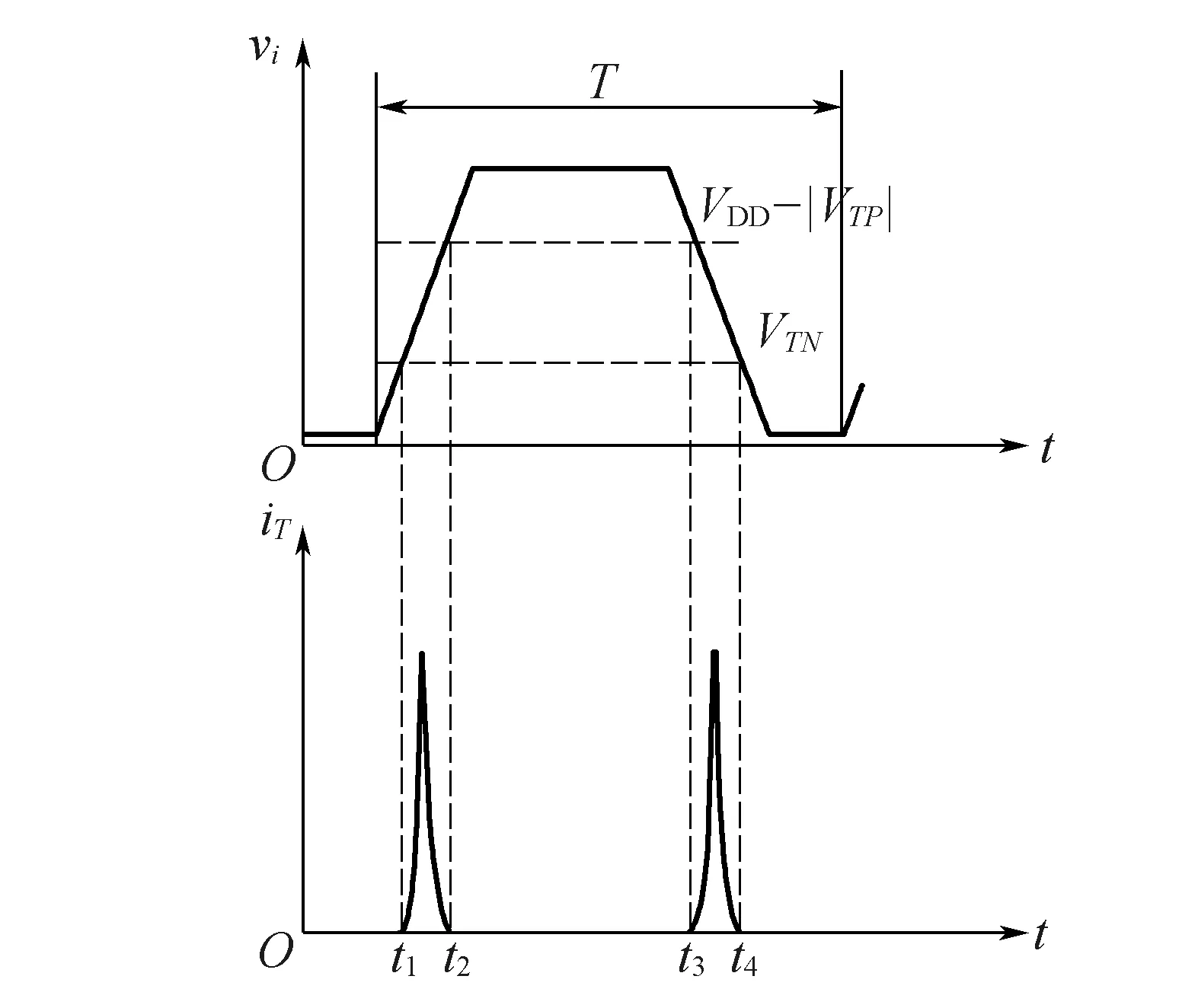

为瞬间电流iT的平均值,图1为瞬间电流iT的波形。

图1 集成电路瞬间导通电流

从图1可以看出,ITAV与输入信号的频率成正比,这样,瞬间导通功耗PT随着VDD和输入信号频率的变化而发生相应的变化。

1.2 集成电路功耗模型

根据上一节的分析可知,电路中工作电压、工作频率、节点的负载电容和节点的工作活动状态是电路动态功耗产生的主要原因。这样,当节点电压出现变化,通常根据式(7)来计算

(7)

式中:α为单个周期内节点发生跳变次数,C为节点负载电容,VDD和f分别为电源电压值和测试时钟频率。C和VDD与工艺水平相关,降低f,则会导致测试时间加长,增加测试成本,因此,降低α,即降低单个周期内节点发生翻转的次数就成为降低电路测试功耗的主要方法。测试环节中的功耗通常采用WTM模型(即有权重翻转次数)来衡量。

(8)

由式(8)可知,降低测试向量中跳变的电平数是减少测试功耗的关键,此外,翻转权重(l-j)和测试功耗有着重要关系,即应该在向量后半部分发生电平跳变。

2 基于扫描链修改的低功耗测试方案

2.1 扫描链修改原理

扫描链具有测试和正常两种功能,具体是由D触发器和多路转换器完成上述功能[11-12]。

传统的扫描单元采用D触发器实现,需要一个多路开关来完成工作状态和测试状态的改变。本文对扫描链结构加以改变,增加一个异或门,将原结构中的D触发器改变成T触发器,这种修改改变的是扫描链的长度,并不改变待测电路的功能。

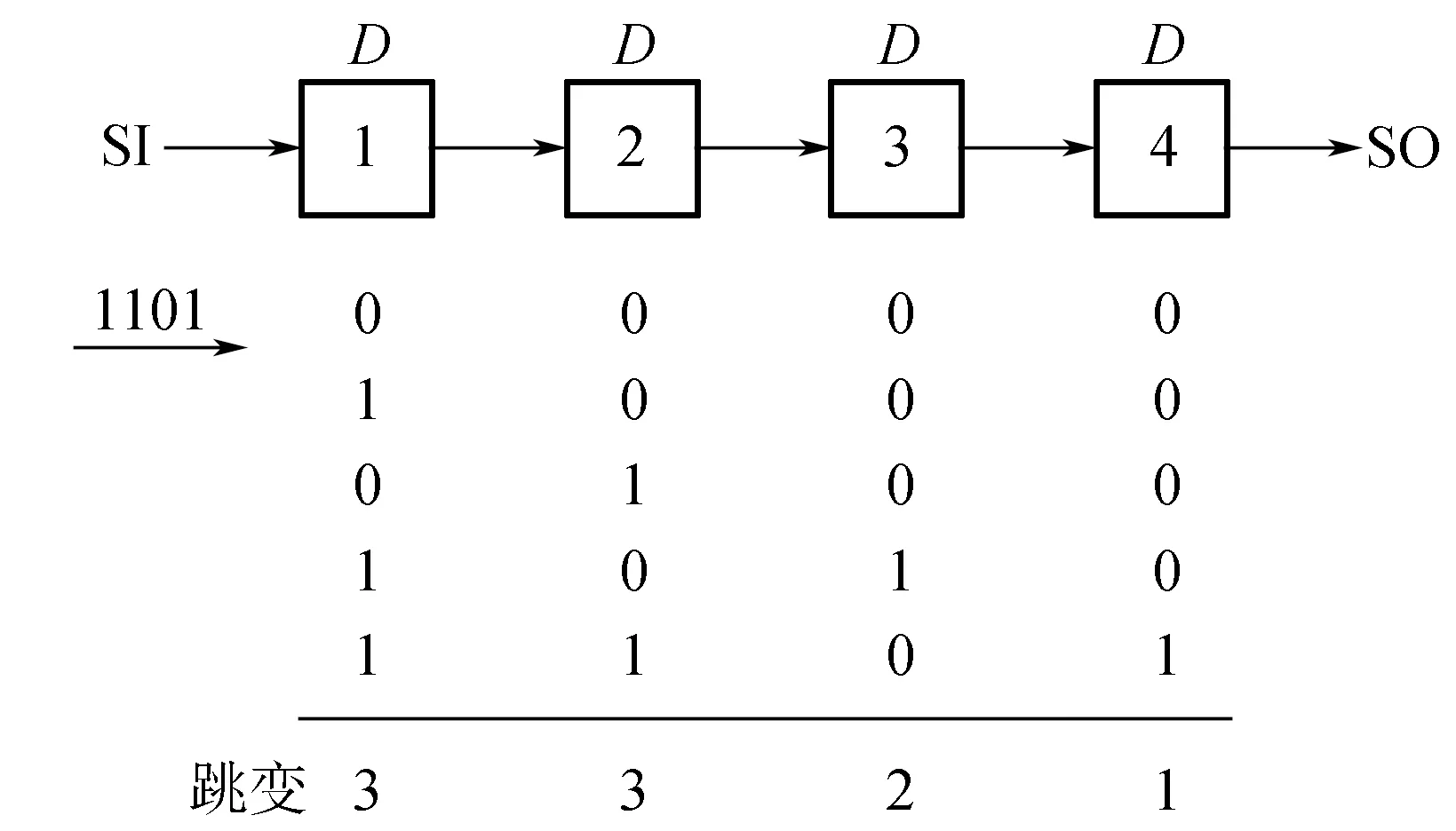

图2为由4个扫描单元组成的未修改扫描链,施加测试向量1101至其中,设扫描链原状态是0000。经过4个时钟周期,全部测试向量移入待测电路中,跳变次数之和为9次。

图2 未修改的扫描链结构

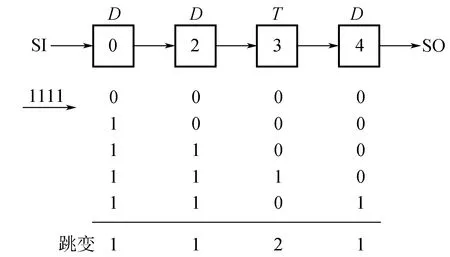

下面修改该扫描链的触发单元,将第三个D触发器处加入一个异或门,令其变为T触发器,图3为修改后的电路。图4为修改后的触发器结构。经过测算,结构改变后待测电路状态发生5次改变,相比改变前,降低了4次。如果测试向量增多,测试单元长度增加时,则测试功耗降低将会更加突出。为了使结构改变后的测试结果不变,需将原施加的1101用更新后的测试数据1111替换。

为了降低待测电路的测试功耗,可以采取降低触发器跳变次数的方法,通过修改扫描链,将部分D触发器用T触发器来代替,同时,需要修改原始测试数据,使输入待测电路中的测试数据保持不变。下面对整个过程分别逐一说明。

定义:设由n个测试向量组成待测电路测试数据集T={t1,t2,t3,…,tn},其中,每个向量由m位组成,定义两向量间的海明距离

(9)

将式(9)当成优化目标,待测电路测试功耗最小化即为其海明距离最小[13-14]。

图3 修改后的扫描链结构

图4 修改后的触发器结构

2.2 测试结构修改和测试向量重排序

采用遗传算法计算后会得到两个数列,这两个数列分别表示施加的测试向量的顺序和扫描链修改后扫描单元中触发器的类型, 0为T触发器,1为D触发器。

2.3 测试数据转换

经过上述过程后,扫描链中的部分D触发器用T触发器替代,因此,改变扫描单元里的值,但剩余扫描单元中的值与跳变概率没有变化。为了保证修改扫描链以后,待测电路的故障覆盖率和仿真结果正确性不会因结构修改而发生改变,需要根据修改后扫描链的相应位置调整输入待测电路的测试向量。

3 实验结果

将本文所提方案应用于部分ISCSAS 89基准电路中。表1列出了该方案的实验结果。

表1 方案的实验结果

从表1可以看出,本文所提方法能使测试过程中芯片消耗的功耗得到减少,比如针对电路s13207,对比没有修改扫描链之前,减少测试功耗为53.56%。在本次实验结构中,应用本方案后,测试功耗均有相应程度的下降,上述基准电路测试功耗平均减少51.26%。

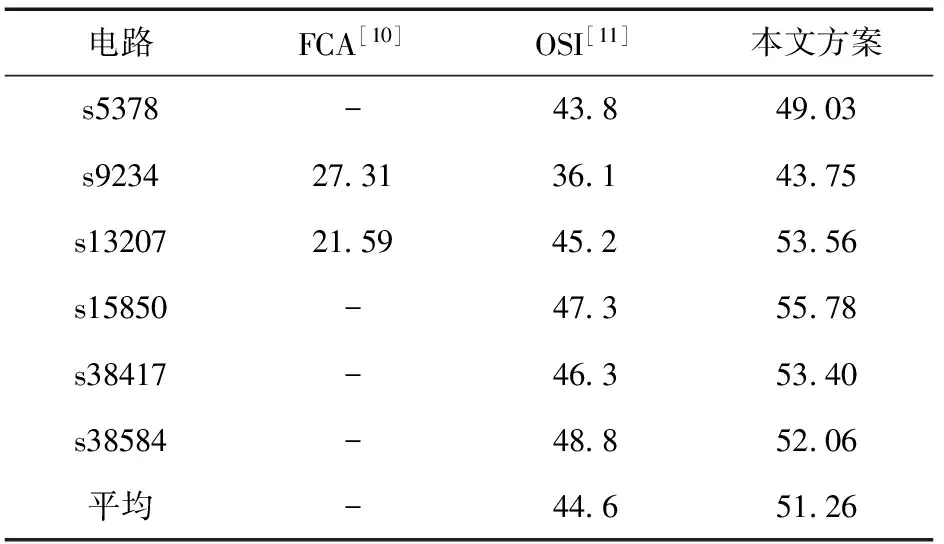

表2是本文所提方法同另外两种近似类型低功耗测试方案所做比较。从该表能够观察出本文所提方案在减少功耗效果上比表2所列方案要好。

本方法对测试结构修改后,一部分D触发器被T触发器所替代,同时加入异或门,可以使得扫描面积变大,但相对于功耗降低的程度而言,效果还是比较突出的,因此,该方案具有相应的实用价值。

表2 实验结果比较

4 结束语

为减少芯片测试过程中功率较高的问题,本文通过对扫描链进行修改来解决此问题。根据扫描链在测试过程中仅仅用来执行传递数据的任务,改变扫描链的结构不会影响电路逻辑功能的情况,本方案将组成扫描单元的部分D触发器增加多路开关以替换成T触发器,通过实验分析,这种方法以较小的硬件开销为成本,使电路测试功率减小。

[1] CIRIT M A. Estimating dynamic power consumption of CMOS Circuits [C] // Proceedings of International Conference on Computer-Aided Design(ICCAD), IEEE, 1987: 534-537.

[2] SANKARALINGAM R, ORUGANI R, TOUBA A N. Static compression techniques to control scan vector power dissipation [C] // Proceedings of IEEE VLSI Test Symposium (VTS), Montreal, IEEE, 2000: 35-40.

[3] TENENTES V, KAVOUSIANOS X. Low power test-compression for high test-quality and low test-data Volume [C] // Proceedings of 20th Asian Test Symposium, New Delhi, 2011: 46-53.

[4] LI W, LI, WU P H, and RAU J C. Reducing switching activity by test slice difference technique for test volume compression [C] // Proceedings of IEEE Circuits And Systems International Symposium, Taipei, 2009, 27(3):2986-2989.

[5] WANG J H, SHAO J B, LI Y M. Using ant colony optimization for test vector reordering [C] // Proceedings of IEEE Symposium on Industrial and Applications (ISIEA), Kuala Lumpur, Malaysia, 2009: 52-55.

[6] KUMAR S K, KAUNDINYA S. Particle swarm optimization based vector reordering for low power testing [C], Proceedings of 2th International conference on Computing Communication and Networking Technologies, 2010: 1-5.

[7] CZYSZ D, MRUGALSKI G, MUKHERJEE N, et al. On deploying scan chains for data storage in test compression environment [J], Design & Test of Computers, 2011, 27(6):46-53.

[8] GIRI C, CHOUDHARY P K, CHATOPADHYAY S. Scan architecture modification with test vector reordering for test power reduction [C] // Proceedings of IEEE International Symposium on Integrated Circuits, 2007: 449-452.

[9] PAMAR H, RUPARELIA S, MEHTA U. WTM based reordering of combine test vector & output response using dijkstra algorithm for scan power reduction [C] // Proceedings of Nirma University International Conference on Engineering (NUICONE), 2011: 1-6.

[10] GUPTA S, VAISH T, CHATTOPADHYAY S. Flip-flop chaining architecture for power-efficient scan during test application [C] // Proceedings of the 14th Asian Test Symposium, Assam, 2005: 410-413.

[11] SINANOGLU O, ORAILOGLU A. Modeling scan chain modifications for scan-in test power minimization [C] // Proceedings of International Test Conference, charlotte , IEEE, 2003: 602-611.

[12] ALMUKHAIZIM S, ALQURAISHI E, SINANOGLU O. Test power reduction via deterministic alignment of stimulus and response bits [C] // Proceedings of 12th Latin American Test Workshop(LATW), 2011: 1-6.

[13] LEE I, PARK J, KANG S. Scan chain swapping using TSVs for test power reduction in 3D-IC [C] // Proceedings of SoC Design Conference (ISOCC), 2013: 170-171.

[14] ANITA J P, WANATHI P T. Genetic algorithm based test pattern generation for multiple stuck-at faults and test power reduction in VLSI Circuits [C] // Proceedings of IEEE Electronics and Communication Systems (ICECS), 2014: 1-6.

[15] 黄明, 王聪, 梁旭. 改进型遗传蚁群混合算法求解旅行商问题[J]. 大连交通大学学报, 2011, 32(2): 86-88.

[责任编辑:郝丽英]

Low power test scheme based on scan chain modification

ZHANG Peiming1,SHANG Jin2, LI Xiaolong1

(1.College of Electrical and Information Engineering,Heilongjiang of Institute of Technology, Harbin 150050,China;2.Control Technology Institute,Wuxi Institute of Technology,Wuxi 214121,China)

Aiming at the problem of high power consumption during the test of the chip, this paper presents a low power test method based on testability design. By inserting the XOR gate, partDflip-flop of scan chain is replaced by usingTflip flops, and genetic algorithm is used to the test structure to modify and test vector reordering. In order to ensure the correctness of the fault coverage and fault simulation, test data is transformed, so that the frequency of the voltage change caused by the node voltage is reduced, and purpose of reducing the power consumption is achieved. Experimental results based on some IS89 benchmark circuits shows that the proposed method can reduce the power consumption, and the average power consumption reduction ratio is 51.26%.

scan chain; test vector reordering; genetic algorithm; low power test

10.19352/j.cnki.issn1671-4679.2017.02.010

2016-10-19

黑龙江省教育厅科学技术研究项目(12531565)

张培明(1966-),男,副教授,研究方向:集成电路可测性设计.

TP391.46

A

1671-4679(2017)02-0045-04