基于多核处理器S698PM的终端系统硬件设计

李 光,颜志宇,张天宇,黄小虎

(珠海欧比特控制工程股份有限公司,广东 珠海 519080)

基于多核处理器S698PM的终端系统硬件设计

李 光,颜志宇,张天宇,黄小虎

(珠海欧比特控制工程股份有限公司,广东 珠海 519080)

随着航天技术的不断发展和研究的不断深入,星载数据总线作为航天器中各个设备和子系统之间的“骨架”和“神经”,其对数据传输的处理能力直接影响着整个系统的性能,为此需要一种高速、可扩展、低功耗、低成本的通用通信链路接口来满足星载数据传输要求。文章主要阐述了针对星务计算机上基于S698PM的CPCI接口的Space Wire数据总线终端系统的硬件设计,为今后S698PM多核处理器和Space Wire总线在我国其他航天任务中的应用打下了良好的基础。

多核处理器S698PM;Space Wire总线;CPCI接口

0 引言

Space Wire技术是欧空局为解决星上数据传输问题而提出的一种新的高速 (2 Mb/s~400 Mb/s)、点对点、全双工的串行总线网络。Space Wire不仅具有较高的数据传输速率,而且加强了在线错误检测和恢复、故障处理和保护以及系统时间广播等方面的功能,使之更加适应航天器的空间运行环境。本文在研究Space Wire总线的基础上,分析了Space Wire总线接口终端的设计与实现,并着重分析了系统中主要组成部分的功能和设计。

1 Space Wire网络系统概述

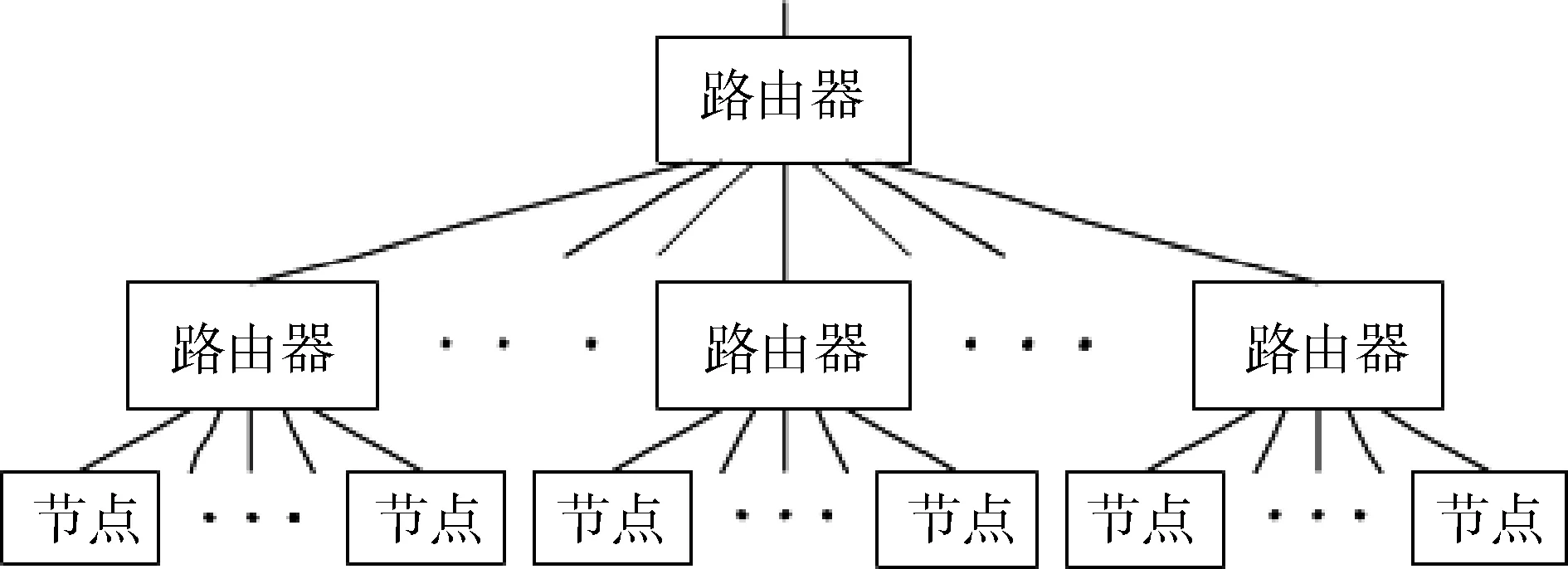

Space Wire网络采用的路由方式为动态路由,就是节点和节点之间以及节点和路由器之间没有固定的数据通道,而是根据需要进行改变,不同源节点与目的节点之间的通信数据可以通过动态路由方式共用一条链路完成交叉传输,从而通过有限的物理链路建立起大量的节点之间的“虚拟信道”;Space Wire系统由多个链路、节点和路由器组成。节点是在网络中进行包传输的源点和目的点;链路提供从一个节点到另一个节点间进行包传输的媒介。节点可以直接通过链路连接或者通过路由器连接;路由器将多个节点连接在一起,通过一定的路由机制将来自一个节点的数据包路由到其他节点上去[1]。图1为Space Wire网络示意图。

图1 Space Wire网络示意图

2 设计与实现方案

本文设计的Space Wire终端系统采用直接从模式设计,支持4路Space Wire总线通信,主要由处理器控制模块、存储器模块、Space Wire驱动模块和CPCI接口模块4部分组成。

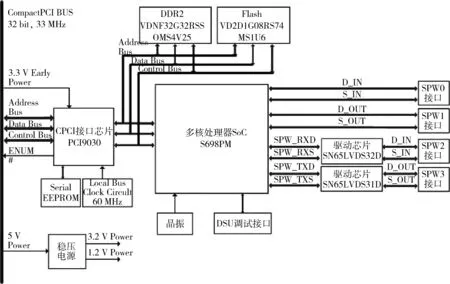

2.1 终端系统总体结构

本文设计的Space Wire终端系统硬件主要由处理器控制模块、存储器模块、SPW驱动模块和CPCI接口模块组成,图2所示为 Space Wire终端系统结构框图。此终端系统遵循ECSS-E-ST-50-12C协议规范,通过Space Wire总线接口实现各个设备与子系统之间高速、实时、确定、可靠的数据交换[2]。

图2 Space Wire终端系统结构框图

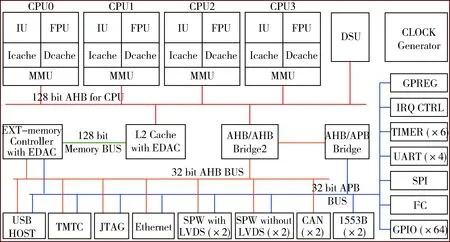

图3 S698PM芯片结构框图

2.2 处理器控制模块

本文设计的Space Wire终端系统,处理器控制模块选用珠海欧比特控制工程股份有限公司的一款多核并行处理器SoC芯片S698PM,图3为S698PM芯片结构框图。此芯片采用对称多处理架构(SMP),7级流水线,遵循SPARC V8架构标准,内部集成4个相同的高性能处理器核心和丰富的片上外设总线资源(包括Space Wire、1553B、CAN、以太网等),融入了三模冗余容错、存储器检错纠错、指令流水线重启等技术,支持RS232、JTAG、Ethernet在线调试,具有“抗辐照、高集成度、低功耗、超稳定、长寿命、小型化”等特点,为我国卫星、飞船、空间站、深空探测器等外太空电子智能系统及装备提供抗辐照、高性能、高可靠的核心处理器芯片的保障和支持。

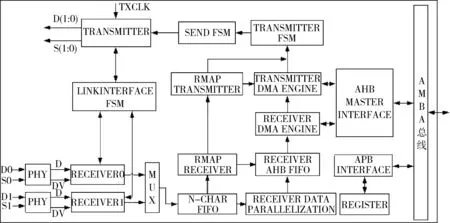

处理器控制模块主要实现Space Wire节点的数据收发、字符判别、数据流控制、链路错误检测与恢复以及与CPCI 9032通信接口通信等功能。Space Wire链路接口主要由接收器、发送器、控制器组成。下面简单介绍Space Wire 节点控制器的工作过程。图4所示为Space Wire节点控制器功能结构框图。

控制器根据外部输入的链路控制信号,复位或使能接收器和发送器,在接收器和发送器输出的状态信号基础上判断链路是否建立连接以及链路是否发生错误,在发生错误后执行错误恢复操作,重新建立链路连接。

接收器负责根据输入的数据和状态信号恢复采样时钟,并以此时钟为基准对数据信号串并转换以及判断接收到的字符类型,将判断出的字符类型送到控制器;另外,接收器负责时钟恢复、数据解析、数据错误和状态的检查等,并将检测到的错误信号送到控制器,由控制器完成错误恢复。

发送器负责波特率控制和对发送的数据进行DS编码。波特率控制允许用户在9种不同的波特率中根据需要进行切换;数据的DS编码按照相应的字符发送需求和优先级完成相应的字符发送,如果没有字符发送需求,则发送空字符以维持链路之间的链接。另外,发送器还负责数据和状态的检测,并将错误信号送到控制器,由控制器完成错误恢复[3]。

2.3 Space Wire驱动模块

Space Wire终端系统支持4路Space Wire总线通信,由于S698PM芯片内部集成4通道的Space Wire总线节点控制器,其中SPW0、SPW1内置LVDS模块,SPW2、SPW3没有内置LVDS模块,因此SPW0、SPW1只需通过链路直接连接,而SPW2、SPW3需要选用TI公司的高速差分线接收器SN65LVDS32D和高速差分线发送器SN65LVDS31D芯片作为Space Wire总线电平的转换和驱动,实现Space Wire终端系统数据与各个设备和子系统之间的数据交换。

图4 Space Wire 节点控制器功能结构框图

2.4 存储器模块

存储器模块选用珠海欧比特控制工程股份有限公司的“高性能、高可靠、抗辐照”SIP立体封装大容量存储Flash芯片VDNF32G08RS50MS4V25和DDR2芯片VD2D1 G08RS74MS1U6,主要用于指令和数据的存储、传输、分析等功能,解决了对Space Wire终端系统大容量存储器的需求。

2.5 CPCI接口模块

CPCI接口模块主要用于Space Wire终端系统的供电和上位机通信功能,CPCI接口与处理器S698PM的通信选用PLX公司CPCI9030芯片,采用直接从模式设计,通过CPCI接口将Space Wire终端系统嵌入在各个设备和子系统中,通过Space Wire网络之间的互联,实现各个设备和子系统之间的数据交换[4]。

3 结论

本文在研究多核并行处理器SoC芯片S698PM和Space Wire总线的基础上,分析了基于S698PM的CPCI接

口的Space Wire数据总线终端系统硬件设计,并着重分析了系统中各个模块的功能,此方案对今后多核处理器SoC 芯片S698PM在我国航天星务计算机及其他任务中的应用具有重要意义。

[1] 陈大羽,王琨,李涛,等,空间高速总线Space Wire节点的设计与实现[J].航天返回与遥感,2010,31(4):58-64.

[2] 欧比特控制工程股份有限公司.EMBC1000-PCISPW型Space Wire节点通讯板卡使用说明书[Z].2013.

[3] 欧比特控制工程股份有限公司.高性能32 位多核处理器SOC 芯片S698PM 用户手册[Z],2014.

[4] 陈健飞,曹松.Space Wire总线接口终端的设计与实现[J].微计算机信息,2010,26(82):123-124.

The hardware design of terminal system based on multi-core processor S698PM

Li Guang, Yan Zhiyu, Zhang Tianyu, Huang Xiaohu

(Zhuhai Orbita Control Engineering Co.,Ltd.,Zhuhai 519080, China)

With the deepening of the development of space technology and research, space-borne data bus as the “skeleton” and “nerve” between the various equipments and subsystems of spacecraft, its ability to deal with data transmission directly affects the performance of the whole system, therefore we need a high speed, extensible, general communication link interface of low power consumption, low cost to meet the requirements of spaceborne data transmission. This article mainly elaborated the hardware design of Space Wire data bus terminal system based on the S698PM CPCI interface whch is applied to the satellite computer. For the future S698PM multi-core processors and Space Wire bus application in other space missions in China laid a good foundation.

multi-core processors S698PM;Space Wire bus;CPCI interface

V19

A

10.19358/j.issn.1674- 7720.2017.09.010

李光,颜志宇,张天宇,等.基于多核处理器S698PM的终端系统硬件设计[J].微型机与应用,2017,36(9):31-33.

2017-03-30)

李光(1983-),男,本科,主要研究方向:基于SPARC架构的SOC与立体封装SIP产品的应用及宇航总线电子产品研发、设计、应用。

颜志宇(1984-),男,本科,主要研究方向:基于SPARC架构的SOC产品与立体封装SIP产品的应用及宇航总线电子产品研发、设计、应用。

张天宇(1991-),男,本科,主要研究方向:基于SPARC架构的SOC产品与立体封装SIP产品的应用及宇航总线电子产品研发、设计、应用。