JESD204B协议中自同步加解扰电路设计与实现

欧阳靖,姚亚峰,霍兴华,谭宇(中国地质大学 机械与电子信息学院,湖北 武汉430074)

JESD204B协议中自同步加解扰电路设计与实现

欧阳靖,姚亚峰,霍兴华,谭宇

(中国地质大学 机械与电子信息学院,湖北 武汉430074)

作为JEDEC最新修订的AD/DA串行传输协议,JESD204B采用自同步扰码对数据链路层原始信号进行随机化转换,有效地避免了杂散频谱产生 ,减少了物理层误码概率。本文基于经典状态机结构对JESD204B协议中自同步加扰及解扰电路进行设计实现,文章阐述了协议中自同步扰码的原理细节,提出了一种加扰与解扰状态电路的设计方案,最终对该方案进行实现、仿真与综合。仿真与综合结果表明该方案充分兼容协议控制信号,功能完全符合协议要求,增强了加解扰电路的稳定性与容错性,同时提高了电路的处理效率,可应用于JESD204B高速串行接口电路设计中。

电路设计;JESD204B协议;加解扰状态电路

JESD204B作为JEDEC国际组织于2011年修订的AD/DA采样数据传输协议[1],实现了多链路多通道串行传输的同步传输,单通道的数据传输速率达到12.5 Gbps,显著提升了数据转换器(ADC/DAC)与逻辑设备(ASIC/FPGA)之间的数据吞吐率。

JESD204B协议将加扰处理作为发送端数据链路层的首个环节,对传输层输入的帧数据进行随机化处理;在接收端方面,将解扰作为数据链路层的最后一个处理环节,还原数据。扰码的作用主要分为两个方面:其一,数据经过加扰的随机化处理,打乱连续相同字节间的相关性,避免物理层转换后的模拟信号出现杂散频谱,防止杂散频谱引起的电磁干扰,减少误码发生的概率,增加数据传输的准确性;其二,经过随机化的数据,其比特流中0、1分布更均匀,抑制了信号传输的直流分量,提高了接收端锁相环提取信号进行时钟恢复的效率。

文中遵循JESD204B协议中对扰码的原理细节,采用经典状态机结构对加扰与解扰电路进行了设计实现。在控制信号上引入了协议规定的scr_cfg 与data_en两路信号进行状态控制,提升了电路的兼容性与可移植性;在状态设计上采用状态机对同步帧放行、初值传递与数据帧加解扰过程进行有效的控制,提升了电路整体的稳定性与容错性;在性能设计上采用32路并行的方式,提升了总体的工作频率。文中将给出关键设计代码与具体仿真结果,验证所设计电路正确性与可综合性。

JESD204B作为最新的AD/DA数据高速串行传输协议,针对其扰码电路实现的技术文献较少,国内现有文献中对协议控制信号的兼容与扰码状态跳转的覆盖等问题处理不够全面[2],未能完全符合协议要求,因此本文对JESD204B接口扰码电路设计具有一定的参考价值。

1 协议原理与状态设计

1.1 自同步加扰与解扰原理

JESD204B协议采用自同步扰码,其规定的扰码多项式为1+x14+x15。自同步扰码简要原理分析如下:

1)对于某个输入比特Dn,其扰码结果Sn,则Sn=Dn⊕Sn-14⊕Sn-15,即扰码结果为:当前位Dn、前14位的扰码结果Sn-14、前15位的扰码结果Sn-15三者之和。

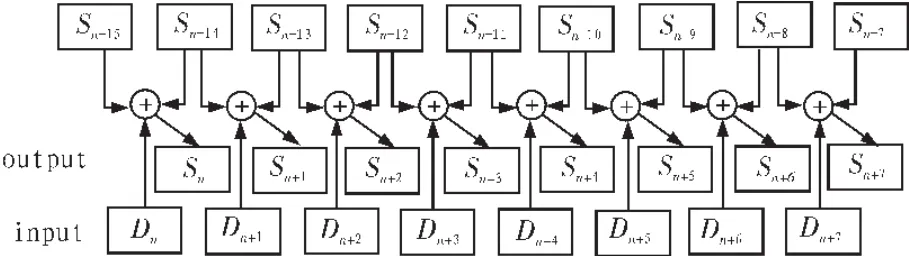

2)如图1所示,JESD204B协议数据链路层的字节长度为8bits,称为octet。1个时钟周期需要对1 个octet进行加扰,因此可将扰码多项式迭代拓展到8位并行的情况。

图1 8位并行自同步扰码

由自同步扰码的原理可知当前位加扰需要前16位的扰码结果作为计算条件。因此,最初的16个比特数据由于条件缺失,无法利用该多项式进行加扰。JESD204B协议规定,扰码初始2个octet不加扰,同时作为初值用于后续数据的加扰,因此在工作情况下自同步加扰输出应为:

解扰是将加扰数据恢复为原始数据的过程。对二进制数A、B有:A+B+B=A,因此可得出解扰的公式为:Dn=Dn+Sn-14+Sn-15+Sn-14+Sn-15=Sn+Sn-14+Sn-15,即Dn=Sn⊕Sn-14⊕Sn-15。加扰时最初的16个比特作为初值不加扰,解扰时这些比特也不应被解扰,因此在工作情况下自同步解扰的输出为:

1.2 加扰与解扰状态机设计

JESD204B发送状态机如图1所示,系统复位时处于码群同步状态(CGS),此状态发送K28.5字节[3],进行字节内比特次序的对齐;此后进入初始通道同步(ILAS)状态,发送特定的多帧序列用于多帧内字节次序的对齐,同时传输控制参数[4]。上述两个状态为同步状态,协议规定同步时任何数据均不进行加扰。

图2 JESD204B发送状态机

根据协议规定,当ILAS发送完最后一个多帧时会反馈data_en信号指示进入用户数据发送(DATA)状态。在该状态下传输层的帧数据开始进入数据链路层的加扰模块[5]。此时,加扰模块是否对数据进行加扰操作还需取决于用户寄存器中扰码使能scr_cfg是否开启,若scr_cfg置1,则进行加扰,否则不进行加扰而将数据透传[6]。

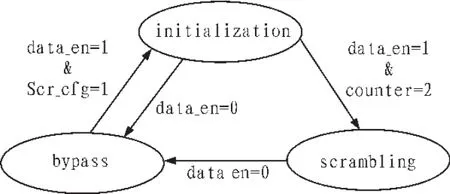

综合上述的协议分析,本设计将扰码分为3个状态阶段,如图3所示。

图3 加扰状态机

1)bypass:此状态下JESD204B发送状态机正在进行CGS与ILAS的同步,输入加扰模块的所有数据均不加扰,直接输出。此状态跳转为initialization的条件为:CGS与ILAS过程结束(data_en=1)且扰码使能开启(scr_cfg=1),若扰码使能未开启,则无需加扰,一直处于bypass状态,将数据直接透传。

2)initialization:此状态下JESD204B发送状态机刚完成同步过程,进入DATA状态。加扰模块需要进行初值传递,即前2个周期输入的octet不加扰,直接输出,同时需要对发送数量进行计数。此状态跳转为scrambling的条件为:系统处于DATA状态(data_en=1)且完成2个octet的发送 (Counter= 2);此状态跳转为bypass的条件为:系统发生了传输错误,JESD204B发送状态机重新同步,不再处于DATA状态(data_en=0)。

3)scrambling:此状态下已经完成了初值的传递,需要对输入加扰模块的每个octet进行加扰处理。此状态跳转为bypass的条件为:系统发生了传输错误,JESD204B发送状态机重新同步,不再处于DATA状态(data_en=0)。

解扰与加扰状态机结构一致,在接收端完成CGS与ILAS同步后,解扰模块进行初值接收并于2个周期后开始对数据进行解扰[7],此处不再累述。扰码状态划分实现了状态控制与数据处理的分离,减小了电路的耦合程度,避免了输入延迟等问题导致的输出波动,增强电路稳定性[8]。

2 设计实现

JESD204B协议中物理层支持单通道12.5Gbps的串行传输速率,为了满足协议要求,在加扰与解扰模块的设计中应尽可能提高处理速率[9]。在此设计中参考Analog Devices-AD9144的设计理念,采用32位并行处理的方式,增加电路面积换取较高的输出比特率[10]。在32位并行模式下,每个周期内输入为1 quad byte=4 octets=32 bits,因此对于加扰状态机而言,Initialization状态下不仅需要进行初值传递(前2个octet不加扰,直接输出),同时需要对后两个octet进行扰码[11]。此状态跳转为scrambling的条件也相应修改为:系统处于DATA状态 (data_en= 1)。类似的,解扰状态机作相同修改即可[12]。

基于上述状态与功能划分,采用Verilog HDL对加扰电路进行了实现,如下给出电路的关键代码:

解扰电路与加扰电路原理类似,实现方式相近,此处不再累述。

3 仿真分析

3.1 功能仿真

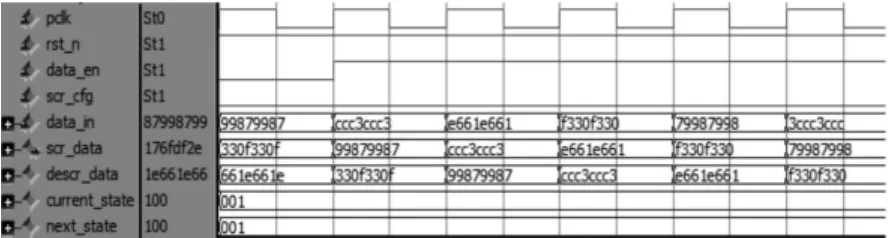

文中采用Modelsim对自同步加解扰电路进行了功能仿真,通过加解扰联调的方式验证扰码的正确性。如图4所示,其中data_in为加扰输入数据,scr_data为加扰输出数据,descr_data为解扰输出数据,scr_cfg为扰码使能开关。加扰电路正常工作时经历了3个状态的跳转:当data_en=0时,不进行加扰,同理未进行解扰;当data_en=1时,32位输入中的前16位未被加扰(前2个octet),此后所有输入均依次进行加扰。通过解扰联调,确认各个阶段的数据均被正确恢复,数据传输正确。

图4 加解扰使能时仿真

如图5所示,当scr_cfg=0,即扰码使能关闭时,各个阶段的数据均未被加扰也未被解扰,数据传输正确。

图5 加解扰未使能时仿真

如图6所示,当实际情况存在data_en信号延迟情况,即未与时钟上升沿对齐时,加扰与解扰均正常进行了处理,确保了自同步加解扰的稳定性和容错性。

图6 DATA_en存在延迟情况下的工作情况

3.2 综合结果

文中设计的32位自同步加扰电路在Synopsys Design Compiler环境下采用SMIC180工艺库进行了综合,使用了基础约束条件和导线模式[13]。综合结果如表1所示。由于采用32位并行结构,其处理速率为8位扰码器的1.72倍 ((185.76*32)/(432.90* 8)=1.72),提高了电路的实际处理速度,满足协议对加扰电路的速度要求。

表1 加扰电路综合结果

4 结束语

文中基于JESD204B协议,分析了加解扰原理,提出了一种自同步加解扰电路的设计方案,并采用Verilog-HDL进行实现。相较其它设计[2],文中设计充分兼容协议规定的所有控制信号,通过状态机的合理引入提升了电路的稳定性与容错性,采用32位并行方式提高了电路实际处理速率[14]。Modelsim仿真与Design Compiler综合表明电路功能正确,性能指标符合要求[15]。因此,本设计对JESD204B协议中的加解扰电路设计有一定参考作用。

[1]JEDEC solid state technology association.Serial Interface for Data Converters[S].JESD204B,2011: 1-78.

[2]霍兴华.JESD204B协议中扰码器设计 [J].电视技术,2014(5):31-33.

[3]张峰.基于JESD204协议的AD采样数据高速串行传输[J].电讯技术,2014(9):31-33.

[4]TuiteDon.JESD204BConvertersSimplifyASICInterfacing[J].Electronic Design,2012,60(15):21-23

[5]Del Jones.JESD204B Data Link Layer[R].Analog Devices,2013:11-12.

[6]Del Jones.JESD204B Transport Layer[R].Analog Devices,2013:7-10.

[7]霍兴华,姚亚峰,贾茜茜.JESD204B接口协议中的8B10B编码器设计[J].电子器件,2015(10):12-25.

[8]李永乾.基于8B10B编码技术的SerDes接口电路设计[D].成都:电子科技大学,2011.

[9]施根勇,黄世震.高速SPI接口在OSD中的应用[J].电子器件,2012(2):20-23.

[10]Analog Devices.Quad,16-Bit,2.8GSPS,AD9144 Data Sheet[M].2012:15-27.

[11]Analog Devices.14-Bit JESD204B,Dual analogto-Digital converter data sheet AD9680[M].2014: 22-34.

[12]Analog Devices.80 MHz Bandwidth AD6673 Data Sheet[M].2012:33-47.

[13]Synopsys.Synopsys chip synthesis workshop[M]. 2008:10-12.

[14]Synopsys.Create a Better Starting Point for Faster Physical Implementation[M].2008:15-20.

[15]Synopsys Professional Services Asia Pacific.Chip Synthesis Workshop[M].2009:22-23.

Implementation and design of self-synchronous scrambling and descrambling circuit based on JESD204B standard

OUYANG Jing,YAO Ya-feng,HUO Xing-hua,TAN Yu

(Faculty of Mechanical&Electronic Information,CUG,Wuhan 430074,China)

As a latest version of AD/DA serial transmission standard proposed by JEDEC,JESD204B uses self-synchronous scrambling to randomize the signal of the data-link layer,which is able to effectively reduce the emergence of spurious spectrums,and hence decreases possibility of bit-error.This article is aimed to using the structure of classic state-machine to design the scrambler and descrambler circuit of JESD204B Standard.The article elaborates the principle of the self-synchronous-scrambling in JESD204B standard at first,then proposes a design scheme of the scrambler and descrambler circuit,finally realizes the design and provides simulation and synthesis results The simulation result proves that this design is completely conform to the standard and enhances the stability of the circuit,in this point,it can be applied in high-speed interface circuit design that specificities in JESD204B.

circuit design;JESD204B standard;scrambler and descrambler state circuit

TN46

A

1674-6236(2017)07-0148-04

2016-03-28稿件编号:201603357

欧阳靖(1989—),男,福建泉州人,硕士研究生。研究方向:高速SerDes接口电路设计、VLSI设计等。