一种弹载数据链载波同步数字锁相环设计

王 鹏, 龚 克, 郭玉霞

(1 信阳师范学院, 河南信阳 464000; 2 中国空空导弹研究院, 河南洛阳 471009)

0 引言

弹载数据链系统是顺利实现中制导的关键组成部分,早期的数据链系统多采用模拟发射接收技术,但近年来已逐步转向数字化,再加上作战环境日益复杂,各类电磁干扰层出不穷,新型导弹对数据链系统的性能要求也越来越高[1]。

与此同时,软件定义无线电(software defined radio,SDR)技术自上世纪90年代被Joseph Mitola III博士提出以来[2],已得到了广泛认可,它的最主要特点是核心功能不再通过专用硬件来定制,而是通过软件来实现[3-4]。这使得SDR对弹载数据链尤其具有吸引力,利用同一套硬件平台即可不断适应各种新需求。因此,基于SDR理念的新一代数据链系统研制已经成为了一个主要研究热点。

传统SDR的处理核心是FPGA和DSP/CPU芯片,其中前者主要完成A/D信号预处理,后者则完成相对复杂的信息处理功能[5]。但近年来随着FPGA集成度的不断提高,FPGA的可编程资源已经有了突飞猛进的增长,许多过去只能用DSP/CPU完成的运算现在已完全可以由FPGA实现[6]。在SDR平台中仅使用FPGA完成所有功能不仅可以进一步提高系统集成度,而且可靠性和吞吐量均得到极大改善。

对全数字化的弹载数据链系统,载波同步具有极其重要的地位。如果系统设计时有单独的导频分量,可以直接通过窄带滤波的方式实现载波同步[7],但这是典型的开环控制系统,性能相对较差。为了达到闭环同步的目的,通常需要采用专用的锁相环PLL电路实现,而PLL是一种典型的模拟器件,性能参数难以保持长期稳定,而且也不具备软件可编程功能。因此有必要进行数字化,即数字锁相环,然而在数字化后如何合理的设计各环节参数,以及如何达到较高的工作频率仍是数据链乃至许多通信系统中面临的主要问题。如刘威等人设计的数字锁相环,其锁定频率范围仅为20~600 kHz[8]。苏洲等人采用Xilinx公司FPGA芯片也实现了另一种结构形式的数字锁相环[9],但采样率也仅为1 MHz,相应的载波频率范围同样很低,这样的频率范围是无法满足新一代数据链的通信需求的。谢锡海从Matlab仿真角度实现了适合飞行器使用的低速率和高速率2种BPSK载波同步系统[10],但并未考虑具体硬件实现,工程参考价值仍有待提高。

针对上述问题,文中对弹载数据链的接收平台数字化载波同步设计及实现开展了深入研究,首先从模拟PLL系统传递函数出发,对其进行离散化,推导出与之等价的离散域系统传递函数,并进行合理的定点化,重点研究离散域环路滤波器的设计准则,以数据链中常用的BPSK抑制载波系统为应用对象,采用Costas同相正交环实现了160 MHz高采样率下的宽带通信系统载波同步,可直接输出基带IQ数据,且环路工作参数动态可编程。整个设计基于SDR理念,并在Xilinx公司的Vivado开发系统上完成了综合和布局布线,经仿真测试,该数字锁相环具有同步性能良好、适应性强的优势,工作频率大大超过同类设计。

1 SDR接收平台概述

如图1所示,该SDR接收平台采用典型的宽开模式,支持MIMO处理,射频信号经过低噪放及后续放大环节后通过混频器变至固定的190 MHz中频,中频信号最大带宽为30 MHz,该中频信号经滤波后由高速ADC芯片变换至数字域,具体ADC芯片采用TI公司的ADS4449,单芯片支持4路模拟数据同时采集,最大采样频率和采样位数分别达到250 MHz和14 bit。在本设计中ADS4449的实际采样频率为160 MHz。

SDR平台的处理核心采用Xilinx公司的Artix-7系列XC7A100T-1L(图1中虚线框内部分),该器件采用低功耗28 nm制造工艺,引入了全新的Slice结构,是目前市面上性价比最高的FPGA器件系列之一[11]。需要注意的是,在开发环境选择上,ISE和Vivado均可以支持7系列器件,但ISE早已步入其生命周期的维护阶段;Vivado则是专为7系列及后续器件开发,综合、布局布线效率均远高于ISE,内建仿真器也已经可以媲美专业的第三方HDL仿真器。而国内工程师因为长期习惯于ISE下的软件开发,时至今日仍未及时转向Vivado平台,也就难以真正体会到7系列器件和全新集成调试开发环境带来的性能优势。本设计采用Vivado 2016.1完成开发,更具工程实用性和参考价值。

为了方便SDR平台与外部的信息交互,在FPGA内实现了一个Microblaze软核,工作主频同样为160 MHz,并通过AXI4总线架构的BRAM缓冲区与其余硬件可编程资源进行双向通信,此外还为Microblaze软核添加了1个UART收发器,该收发器经过Silicon Laboratories的CP2102转换为USB接口后可直接与调试上位机完成双向通信,波特率达921 600 bit/s。Microblaze的开发语言采用成熟高效的C语言,主要完成SDR平台的参数计算以及对外通信等功能。

本设计主要针对图1中的AD数据采样和载波同步展开,因同步模块的输入来源于外部AD数据,因此首先介绍AD数据采样设计,此后详细分析数字锁相环与模拟锁相环之间的联系,重点介绍面向FPGA的数字锁相环硬件实现,最后给出了性能测试结果。

2 AD数据采样模块设计

ADS4449数据输出时序为DDR模式,Xilinx公司提供了专门的IDDR原语,可以方便的以源同步方式接收该模式数据,但FPGA内部逻辑的时序驱动仍然是SDR模式,因此在IDDR处理后还必须对其进行转换。由于时钟速率很高,在数据转换时必须避免亚稳态的出现,以下说明具体的转换策略。

在IDD的工作模式选择上,采用SAME_EDGE_PIPELINED模式,使原本处于同一个时钟周期内的2组数据分别通过Q1和Q2端口在输入时钟的上升沿输出。14 bit数据共需调用14组IDDR原语,为了保证较好的时序性能,这14组I/O引脚和ADC随路时钟引脚应处于FPGA的同一个BANK内,且随路时钟应分配至具有时钟使能(clock capable,CC)功能的引脚以保证高速时钟驱动强度及走线质量,经过IDDR处理后,输出数据速率变为160 MHz,但传输时钟仍为80 MHz,在每个时钟的上升沿可输出2组数据,二者在时间尺度上相差1个采样周期。

FPGA内部全局工作时钟为160 MHz,IDDR输出数据必须同步至该时钟域,PGA时钟与ADC输出时钟为同源时钟,可使用更简单的分布式RAM乒乓缓冲代替复杂的异步FIFO实现跨时钟域交换,利用Vivado生成2块16×14 bit的简单双口RAM,RAM的写端口分别为IDDR的Q1和Q2数据,写地址为0~15循环缓冲,写时钟为80 MHz;RAM的读时钟则为160 MHz,并通过1个T′触发器反复在2个RAM的读数据端口之间切换,读地址同样是0~15循环读,为避免读写冲突,读地址比写地址至少延迟2个时钟周期以上。

3 模拟锁相环与数字锁相环

为建立模拟锁相环与数字锁相环之间的对应关系,从应用最广泛的有源比例积分二阶模拟环着手,其信号流图如图2所示。

(1)

在模拟锁相环路的主要部件中,乘法器和低通滤波器可以直接用硬件乘法器和数字FIR滤波器实现数字化,VCO对应数字域的DDS,环路滤波器则相对复杂,它需要将原模拟系统的传输函数从模拟s域映射至z域,本设计采用双线性变换实现,其映射关系见式(2)。

(2)

经双线性变换后,环路滤波器传输函数为:

(3)

(4)

式(4)对应的信号流图如图3所示。

DDS的传输函数计算相对简单,设DDS频率控制字长为W,其输出相位θ(n)与输入频率字u(n)的差分方程可表示为:

θ(n)=θ(n-1)+2π/2Wu(n-1)

(5)

对上式两边施加z变换,即可得到DDS的传输函数为:

(6)

(7)

式(7)为从离散域直接推导得到的传输函数,而如果直接对式(1)施加双线性变换,可得到离散域锁相环传输函数的另一种形式:

(8)

严格意义上,如果希望设计的数字域锁相环与原模拟锁相环等价,应该使式(7)与式(8)完全相等,即式(9):

(9)

式(9)同时满足实际上是不可能实现的,工程上必须采取合理的近似策略,为尽可能满足所有等价关系,首先应保证ωnT≫1,由于采样频率远高于环路自然谐振频率,这一条件通常可以满足。同时,传输函数极点的影响远大于零点,因此可优先保证二者的分母等价,对式(9)中的最后2行等式求解并近似可得:

(10)

式(10)建立了传统模拟锁相环设计参数ξ、ωn和数字域环路参数C1、C2之间的关系,此后即可借用模拟域设计方式完成数字锁相环设计。

4 面向FPGA的Costas环设计

由于载机发射功率有限,为了达到最远的作用距离,并尽可能提高BER性能,QAM、OFDM等民用通信中的高效调制目前并不适用于数据链系统中,实际应用中最常见的仍为BPSK和QPSK系统,其中又以BPSK的解调最为简单。因此文中也选择前者开展设计,它是典型的对极调制信号,只有对信号进行2倍频处理才可以恢复出载波分量,常用的恢复电路为平方环和Costas环路[12-13],二者性能基本相当,但后者不需要使用复杂的正弦波2分频电路,应用更普遍,对应的环路结构如图4所示。

可以看到,模拟Costas环主要利用VCO产生2路正交信号与输入信号鉴相并完成环路锁定,为了达到较好的性能,同相支路和正交支路的电路参数必须严格匹配,这在模拟电路中难以实现,但在数字域则可以达到很高的匹配度,同时还彻底消除了电路参数不稳定、工作点漂移等缺陷,因此数字化Costas环的性能要远优于模拟Costas环。文中第3节已经建立了模拟和数字锁相环参数之间的联系,因此后续Costas数字环路的设计过程已十分清晰,其组成部分与图4保持一致,只是进行了数字化,以下介绍数字域Costas环各主要部件的设计。

4.1 乘法器设计

Vivado中直接集成了硬件乘法器IP核,只需指定乘法器相关参数即可生成源文件和综合网表,由图4可知,整个环路共用到3个硬件乘法器,其中2个乘法器的特征完全一致,其主要作用实际上是完成下变频,输入数据分别是AD采样数据和DDS输出正余弦值位宽,设计中均取14 bit宽,按照第3节的分析,该乘法器全精度输出的最大数据实为225,但为减少后续处理压力,可对其进行简单的截短处理,本设计取结果的高20 bit作为FIR滤波器的输入,相当于乘法增益减少为218。由于工作频率较高,应使能乘法器的流水工作模式。

第三个乘法器的主要作用则是完成I路与Q路的鉴相,本文后续将对其进行简化,最终利用符号反转器近似。

4.2 低通滤波器设计

低通滤波器的设计是整个锁相环路的一个关键部分,首先需保证有用的基带信号无失真通过,因此通带截止频率不应小于15 MHz,此外,低通滤波还必须滤除经中频采样产生的镜像分量以及乘法器新引入的高频分量。按照带通采样定理,中频数字采样后相邻镜像分量的最小频率间隔为:

fmin=min[2fL-mfs,(m+1)fs-2fH]

(11)

将设计参数代入上式,可得最小频率间隔为30 MHz。

(12)

因此,根据前述低通滤波器设计原则,过渡带截止频率不应大于30 MHz。此后即可根据通带波动要求与阻带衰减要求完成相应FIR滤波器设计,本设计采用Matlab的FDATool完成等波纹线性相位FIR滤波器设计,并将滤波器量化位数也设置为14 bit,其归一化频率响应如图5所示。

Matlab生成的浮点滤波器系数默认增益均为0 dB,但由于滤波器系数的定点化,在全精度输出时,实际处理增益为32 768,因此输入数据位宽为20 bit,输出数据最大位宽为35 bit。

4.3 鉴相乘法器设计

理论上,鉴相乘法器仍可以通过专用的硬件乘法器实现,但由于所需位宽较大,乘法器的实现速度将受到影响,同时占用的逻辑资源也十分可观,因此可对其进行一定程序的简化[14],该思路主要利用了环路跟综时,鉴相器两路输入分别代表误差相位2Δφ的余弦cosΔφ和正弦sinΔφ的特点,由于2Δφ的值通常很小,其值可近似看作0或2kπ,故余弦值cosΔφ近似取值为±1,此时鉴相乘法就简化为简单的符号取反器,如图6所示。该简化的鉴相器不产生处理增益,故输入输出位宽仍均为35 bit。

4.4 环路滤波器设计

ωn是影响环路性能的另一个重要参数,一般地,ωn取值越小,环路快捕带越小,但同时捕捉时间也更长,而过大则会使环路由载波跟踪转为调制跟踪,因此实际选择中必须合理选择ωn,通常须保证ωn≫B/2,其中B为中频信号带宽30 MHz,本设计选择ωn=3 Mrad/s代入式(10),可得C1=0.033 8,C2=0.000 442,出于工程化考虑,在硬件实现时可采用简单的移位运算近似实现,实际中可取C1=2-5,C2=2-11。

为了进一步提高SDR平台的适应性,本设计的C1和C2均作为可变参数出现,由Microblaze软核根据不同的需求选择相应的ωn,然后再利用式(10)得到更新后的C1和C2值,并选择最接近2的负整数次幂进行近似。

4.5 DDS数字本振设计

Vivado中集成有参数化的DDS IP核组件,由于4.1和4.4中已经分别确定了DDS输出正余弦值和相位累加值宽度,因此只需要按照设计值直接生成即可。需要注意的是,Vivado中DDS对外接口采用了AXI4-Stream协议,且宽度均为字节的整数倍,因此实际生成的IP核输入频率控制字接口s_axis_config_tdata的位宽为40 bit,而输出正余弦数值则需要从端口m_axis_data_tdata(位宽为32 bit)的高低半字中分别取出。

5 硬件实现及测试

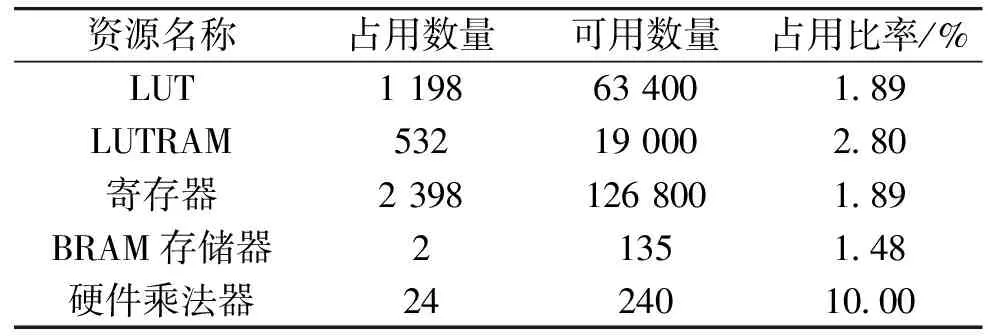

采用Verilog HDL语言完成前述4.1~4.5模块设计和顶层模块实例化,具体实现器件为XC7A100T-1L。由于工作时钟较高,必须为其施加时钟和输入输出约束,Vivado中集成了专用的约束编辑向导,在图形界面中即可方便的完成周期约束、最大最小延迟约束、多周期路径约束等。整个设计的最终资源占用情况如表1所示。

表1 全数字Costas环资源占用表

利用Vivado自带仿真器对设计进行了完整的功能仿真,当收发频差较小时,环路典型锁定值小于10 μs,比袁君等人的锁定时间减少50%以上[15],且最高工作频率大大高于现有设计[16]。相应的DDS频率控制字典型收敛曲线如图7所示。而且由于Microblaze软核的引入,该数字Costas环的捕捉性能是完全参数化的,只需要修改DDS中心频率控制字,即可满足不同中频信号的载波跟踪,而二阶环路参数C1、C2的缩放可直接影响快捕带大小和捕获时间,从而满足不同的应用需要。

6 总结与结论

在弹载数据链系统中引入SDR理念使其具备“软升级”特质,对提高导弹作战性能和生存能力均具有重要意义。文中通过严密的数学推导,建立了模拟锁相环与数字锁相环设计参数之间的联系,并针对目前普遍使用的Costas抑制载波环,设计了一种大带宽可配置数字化锁相环路,可满足不同中频、采样率、带宽的需要,最高工作频率达到466 MHz,整个设计充分吸纳SDR理念,通用性和扩展性良好。虽然该环路为某弹载数据链解调系统开发设计,但只需要做小幅修改,也可同样用于其它军用、民用通信中,具有一定的工程参考价值。

参考文献:

[1] 张俊宝, 张蓬蓬, 宋琛. 空空导弹弹载数据链技术发展浅析 [J]. 飞航导弹, 2014, 3(9): 82-84.

[2] MITOLA J, MAGUIRE G Q. Cognitive radio:making softwarer radio more personal[J]. IEEE Personal Communications, 1999, 6(4): 13-18.

[3] 楼才义, 徐建良, 杨小牛. 软件无线电原理与应用 [M]. 2版. 北京: 电子工业出版社, 2014: 8-10.

[4] 王洪, 孙清清, 肖宇, 等. 基于软件定义无线电平台的1 090 MHz频谱监测与分析方法 [J]. 计算机应用, 2015, 35(S2): 4-7.

对制备的试件进行预损伤和自修复养护,含有微裂纹的试件进行养护后,进行抗压试验,得出抗压强度,按照公式(6)计算微胶囊对含微裂纹的相似试件的强度修复率。强度修复率ηS公式:

[5] 王鹏, 连帅彬, 孙秋菊, 等. ADSP-TS101高速全双工Link收发器FPGA设计 [J]. 信阳师范学院学报(自然科学版), 2015, 28(2): 259-262.

[6] SILVA Joao, SKLYAROV Valery, SKLIAROVA Iouliia. Comparison of on-chip communications in Zynq-7000 all programmable systems-on-chip [J]. IEEE Embedded Systems Letters, 2015, 7(1): 31-34.

[7] 晏辉. 无线通信系统中载波同步关键技术研究 [D]. 成都: 电子科技大学, 2012.

[8] 刘威, 李莉, 陈海燕, 等. 基于FPGA的软件无线电同步系统设计与实现 [J]. 电子器件, 2014, 37(4): 674-678.

[9] 苏洲, 冯全源, 俞卫中. 基于FPGA的全数字Costas环的设计与实现 [J]. 微电子学与计算机, 2013, 30(7): 72-77.

[10] 谢锡海, 姜晖. 高动态条件下BPSK信号载波的同步算法 [J]. 测控技术, 2015, 34(1): 146-149.

[11] XIANG TIAN, ZHAO LEI, JIN XI, et al. A 56-ps multi-phase clock time-to-digital convertor based on Artix-7 FPGA [C]//IEEE. 19th IEEE-NPSS Real Time Conference. Nara:IEEE, 2014: 1-4.

[12] DANDAPATHAKA M, SARKAR B C. Nonlinear dynamics of optical Costas loop with inherent time delay [J]. International Journal for Light and Electron Optics, 2015, 126(24): 5077-5082.

[13] SHOARI A, KAMAREI M, RADMAND A. Implementation of Costas loop using CORDIC algorithm for software radio applications [J]. IEEE Proceedings-Communications, 2005, 152(1): 113-118.

[14] 张欣. 扩频数字通信基带信号处理箅法及其VLSI实现 [M]. 北京: 电科学出版社, 2004: 122-133.

[15] 袁君, 冯全源, 王丹. 基于FPGA的全数字相干解调器的实现 [J]. 微电子学与计算机, 2013, 30(5): 38-42.

[16] 王旭东, 樊涛, 黄强辉, 等. 大多普勒频偏SOQPSK信号FFT引导COSTAS环载波跟踪技术 [J]. 电子学报, 2016, 44(2): 491-496.