低相噪微波取样环电路设计

作者/李维亮,中国电子科技集团公司第四十一研究所

低相噪微波取样环电路设计

作者/李维亮,中国电子科技集团公司第四十一研究所

锁相环作为一种频率合成技术已经广泛应用于本振源设计之中,本文主要介绍基于ADF4106的低相噪微波频段取样环设计,通过对引入噪声机理的分析,采用反馈回路混频降低信号噪声的方案,通过印制板电路及试验结果可得到极低的相位噪声。

低相噪;锁相环;混频技术

引言

随着频率合成技术的不断发展,将锁相环频率合成技术和直接数字式频率合成技术相结合的频率合成技术,由于兼顾了频率分辨率、频率切换时间、杂散、相位噪声等指标,得到了广泛的应用。

本文设计方案基于集成DDS芯片和锁相环芯片ADF4106,使得最终的输出频率3GHz的相位噪声能够达到<-130dBc/Hz@10kHz。

1.锁相环原理

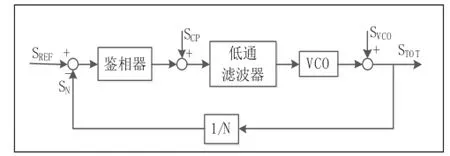

锁相环电路一般由参考输入频率源、鉴相器、低通滤波器、压控振荡器(VCO)和N分频器组成,其原理框图如图1所示。锁相环工作原理:当VCO的频率由于某种原因发生变化时,必然相应地产生相位变化。

这个相位变化与参考输入频率源的稳定相位进行比较,使鉴相器输出一个与相位误差成比例的误差电压,经过低通滤波器后,取出其中缓慢变化的的直流分量。此直流分量用于控制VCO的输出频率,将其拉回到稳定值,此时称环路处于锁定状态。

2.锁相环路噪声模型

图2 锁相环路噪声模型

锁相环的整个环路的噪声模型如图2所示。其中SREF表示参考输入信号的相位噪声的功率谱,SCP表示电荷泵引入噪声的功率谱,SVCO表示压控振荡器引入噪声的功率谱,SN表示分频器引入噪声的功率谱。

假设STOT表示整个环路总的噪声的功率谱,则有以下关系式,推导过程见参考文献[1]:

3.低相噪取样环原理分析

图3 取样环原理框图

由式(1)可得降低相噪的有效方法为降低N的值,故本文方案采用VCO输出反馈与参考混频的方法,此时N=1,使得VCO输出反馈对相位噪声的影响降到最低,基本上没有恶化VCO的输出相位噪声。

借助ADsimPLL辅助计算软件,低通滤波器设置为典型的二阶滤波器,相位裕度为45度,鉴相频率50MHz,环路带宽20kHz,可得到其环路滤波器参数为C1=330pF,R1=432Ω,C2=33nF。

4.试验结果

按照图3的原理图对PCB进行设计,制版完成后对其相噪指标进行测试,使用是德科技E5052B测试可得3GHz频率的相位噪声为-131 dBc/Hz@10kHz,满足指标设定要求。

5.结语

本文通过采用DDS与锁相环相结合的频率合成技术,在反馈回路采取混频方案,使得最终输出的微波频段频率的相位噪声能够达到指标<-130dBc/Hz@10kHz(3GHz)。为合成高相噪指标的宽带本振源提供了良好的取样环电路。

* [1]白居宪.低噪声频率合成[M].西安:西安交通大学出版社,1995.

* [2]张厥盛,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社,1995.