一种可任意扩展的多路级联采集电路设计*

吴正洋,马游春*,王悦凯,姜 德,王晓娟

(1.中北大学电子测试技术国家重点实验室,太原 030051;2.仪器科学与动态测试教育部重点实验室,太原 030051)

一种可任意扩展的多路级联采集电路设计*

吴正洋1,2,马游春1,2*,王悦凯1,2,姜 德1,2,王晓娟1,2

(1.中北大学电子测试技术国家重点实验室,太原 030051;2.仪器科学与动态测试教育部重点实验室,太原 030051)

在长距离需要对多路数据进行采集的情况下,提出了一种基于FPGA的多路级联式采集系统。本系统以FPGA为核心,实现对各路采集单元的命令控制和数据传输控制,并且各采集单元相互独立、所采集的数据单独存储。实验测试结果表明,各路采集数据能够可靠传输到读数单元。各采集单元以级联方式连接,可在采集点自由增减采集单元,实现任意路数据的采集与存储。

数据采集;任意扩展;级联;FPGA

在数据时代,数据采集已经遍及了各个领域,尤其是多路采集在工程上应用极为广泛。在许多测控系统中,经常会需要对多路信号进行采集、传输、存储与处理[1]。目前常用的多路采集系统主要是由读数单元与多个采集单元直接连接,由读数单元同时接受多路数据,并且通常需要对多个信号进行实时采集,同时为了保证数据的一致性,必须同时对数据进行采样[2]。这样不仅对读数单元要求较高,而且线路复杂,当各采集点之间的距离较远时,长线连接也降低了传输的可靠性[3]。

级联连接是一种在网络上常用的连接方式,将两台或两台以上的交换机通过一定的方式相互连接,根据需要,多台交换机可以以多种方式进行级联。多台设备的级联一般形成总线型、树型和星型的级联结构。在实际应用中,这种连接方式的优点在于:当终端机的数量发生变化时,可任意的调配终端,而无需对主机进行调整。

本文提出的多路采集方案就是利用了这一连接方式,将每个采集单元一对一的连接起来,在传输数据时,并不是每个采集单元直接向读数单元发送数据,而是通过层级传输的方式,最终传输到读数单元。并且每个采集单元相互独立,均配备有独立的FLASH芯片,不依赖读数单元即可独立完成高速数据的采集,同一时间只能有一个采集单元可以向读数单元发送数据,读数单元轮流接收各个采集单元的数据,然后将数据存储到U盘中。

1 系统结构

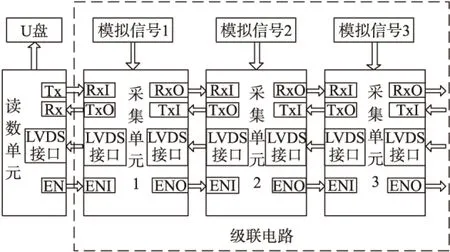

根据设备的功能实现和各部分的技术要求,再结合通信协议和设备的后续功能扩展需求,对系统关键电路进行了总体设计。级联式多路采集系统结构图如图1所示。该系统总体上由读数单元、若干个采集单元、信号源和U盘存储器组成,以FPGA为核心的采集单元完成对模拟信号的采集、处理、缓存与发送,每个采集单元在硬件上结构相同,读数单元同样以FPGA为核心,完成对信号的接收与存储,各单元之间以串行的方式传输数据。为提高系统的可扩展性,还设计了备用LVDS接口,在需要更高的传输速度时使用[4]。

图1 级联式多路采集系统结构图

2 硬件设计

系统硬件电路使用Altium Designer09软件进行设计,读数单元板与采集单元板都采用4层印制电路板。读数单元板主要核心电路是FPGA和CH378L外围架构电路和电源模块电路,采集单元的主要核心电路是FPGA模块、AD采集模块、FLASH模块和电源模块。

2.1 读数单元硬件设计

为了实现系统的功能,读数单元结构主要包含FPGA模块、CH378L模块、USB接口以及信号输入输出接口。读数单元结构图如图2所示。

图2 读数单元硬件结构图

读数单元采用Altera公司Cyclone Ⅳ系列的EP4CE15F17C8作为FPGA控制芯片。采用南京沁恒电子有限公司的CH378L芯片作为U盘控制芯片,该芯片内置USB固件与海量存储协议,能直接将采集的数据存储于大容量U盘中[5],利用CH378L设计U盘存储器外围电路简单,且成本较低。将U盘作为存储介质,以较低的成本实现了海量存储,同时U盘可方便地拆卸与更换,数据交换方便,适用于各种现场应用环境[6]。FPGA与CH378L的电路原理图如图3所示。

图3 FPGA与CH378L连接原理图

2.2 采集单元硬件设计

为了后期可任意增减采集单元数量,每个采集单元采用相同的硬件设计。采集单元的结构如图4所示。采集单元电路主要由FPGA模块、AD芯片、FLASH芯片以及输入输出接口组成。设计时将数字电源与模拟电源采用分区覆铜,并用一点接地的布线方式,将数字地与模拟地有效的隔离开,避免电源和数字部分对模拟地电位产生浮动和干扰[7]。

图4 采集单元硬件结构图

采集单元也采用相同的FPGA芯片;FLASH采用三星公司的K9WAG08U1M,空间大小为1 G×8 bit;AD转换芯片采用ANALOG DEVICES公司的AD7983芯片,该芯片是一个16 bit的模数转换器,数字信号以串行的方式输出到FPGA端口,并以ADR444作为电压参考芯片,实现AD转换功能,在16 bit的采样位宽下,可实现2 Mbyte/s的采集速率。AD模块的电路原理图如图5所示。

图5 AD模块电路连接

图6 读数单元工作流程图

3 软件设计

系统软件由读数单元控制程序和采集单元控制程序组成,采用VHDL硬件描述语言进行编程。

3.1 读数单元软件设计

读数单元的工作流程图如图6所示。初始化完成通讯端口的设置后,读数单元轮流接收各个采集单元的数据。读数单元发送对第N个单元进行采集数据的命令后,使使能端EN有效,然后开始接收第N个单元的数据,若数据未通过校验则发送重新读取数据的命令,完成接收经校验确认数据有效后通过USB接口将数据存入U盘中,然后开始读取下一个采集单元的数据。

读数单元在接收不同采集单元的数据时,会在U盘中为每个采集单元建立对应名称的文件,同一个采集单元的数据会在该文件中连续存储。

3.2 采集单元软件设计

采集单元工作流程图如图7所示。采集单元初始化后开始采集数据并存储到发送缓冲区,待接收到读数单元发出的命令,若确认为读数命令,则判断地址,若N等于本机号,并且使能端口EN有效,则采集单元进入发送数据状态,发送缓冲区的数据到第N-1号单元;若N小于本机号,则采集单元进入传输数据状态,接收第N+1号单元发送来的数据并发送给第N-1号单元,最后传输到读数单元;若N大于本机号,则忽略命令,等待下一条命令到达。

图7 采集单元工作流程图

3.3 通信协议

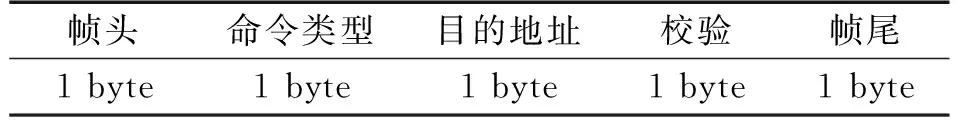

根据系统设计,读数单元与采集单元之间的通信协议自行设定,命令只由读数单元向采集单元发送,数据只由采集单元向读数单元发送,命令帧有请求发送数据、确认发送成功、请求重发数据这3种形式[8]。命令帧的定义如下:

帧头命令类型目的地址校验帧尾1byte1byte1byte1byte1byte

帧头和帧尾可自行定义,本系统将帧头设定为0XF0,将帧尾设定为0XF8。

命令类型用0X00、0X01、0X02分别表示请求发送数据、确认发送成功、请求重发数据命令,采集单元中FPGA判断命令类型的代码如下:

process(command)

case command is

when“00000000”=>

send_data<=‘1’; --发送数据

when“00000001”=>

datadone<=‘1’; --数据已接收并有效

when“00000010”=>

resend_data<=‘1’; --重新发送上一帧数据

when others=>

null;

end case;

end process;

目的地址根据采集单元的序号进行设置,如需让第9个采集单元发送数据,则目的地址为0X09,第9号采集单元将进入发送数据状态,将本机的缓存数据发送到第8号采集单元,第1号到第8号采集单元将进入传输数据状态,将TxI端接收的数据从TxO端发出,最后由1号采集单元发送给读数单元。采集单元中FPGA判断地址的代码如下:

process(address)

if address=“00001001”then

state<=state1; --进入发送数据状态

elsif address<“00001001”then

state<=state2; --进入传输数据状态

else null;

end if;

end process;

最后采用和校验的方式进行校验。

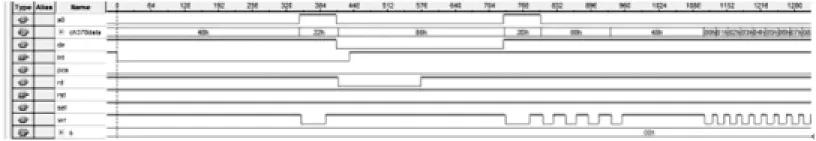

4 系统验证

根据上述的系统设计,采用VHDL语言在QuartusⅡ 12.0开发平台下进行仿真验证。利用QuartusⅡ12.0自带的SignalTapⅡ逻辑分析仪在Altera 的Cyclone Ⅳ器件上进行在线仿真。使采集单元发送递增的模拟信号,将读数单元的FPGA进行在线仿真得到如图8的波形图。

图8 SignalTapⅡ在线仿真图

如图8所示FPGA向CH378L发送请求,再声明数据长度后开始发送递增的模拟信号。

根据实际验证,可以看出FPGA向VH378L发送的数据完整有效,实现了采集单元到读数单元的可靠传输,符合设计要求。

5 结束语

本设计以FPGA为核心,在不需要将每个采集单元都与读数单元连接的情况下,使用级联的连接方式,将各个采集单元一一串联起来,减少了读数单元的连接节点数,并且所有采集单元的结构与电气连接均相同,在后期遇到需要增减采集点,或者某一采集点需增减采集路数,使用本设计方案,可以快捷的解决以上问题,在实际工程应用中具有一定的实用性。

[1] 岳孝忠,裴东兴,王健. 基于USB3.0接口高速数据采集系统的设计[J]. 电子器件,2015,38(1):140-143.

[2] 侯朝勇,胡学浩,庄童. 基于FPGA的多路同步实时数据采集系统[J]. 电子技术应用,2009(10):103-105,108.

[3] 王立恒,任永峰,李圣昆,等. 基于FPGA的多路采集测试系统设计[J]. 电测与仪表,2009(2):20-24.

[4] 常高嘉,冯全源. 基于FPGA的高速数据采集系统的设计与实现[J]. 电子器件,2012,35:615-618.

[5] 南京沁恒电子有限公司. CH378技术手册[S]. 2013(5):1-2.

[6] 向阳,熊瑛,全腊珍. 基于U盘存储的多通道温度记录仪[J]. 机电产品开发与创新,2009,22(2):51-52,42.

[7] 侯进振,占涛,毛乐山. 基于CH375的智能数据采集卡[J]. 现代电子技术,2010(10):143-145.

[8] 刘鹏. 基于51单片机串口通讯的多路采集系统[J]. 计算机光盘软件与应用,2012(1):57-58.

Design of Multiple Cascaded Acquisition Circuit Extended Arbitrarily*

WUZhengyang1,2,MAYouchun1,2*,WANGYuekai1,2,JIANGDe1,2,WANGXiaojuan1,2

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China; 2.Key Laboratory of Instrument Science and Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China)

In the case of long-range multi-channel data acquisition,a FPGA-based multi-channel cascaded acquisition system was presented. This system used FPGA as the core to control the command and data transmission of every acquisition unit,the collected data were stored separately. Experimental results showed that,all the collected data could be reliably transmitted to the reading unit. The acquisition unit was connected in cascade mode,it could increase or decrease acquisition unit arbitrarily in the patch,and realize arbitrary ways of data collection and storage.

data acquisition;arbitrary extension;cascade;FPGA

项目来源:国家自然科学基金项目(61275166);山西省自然科学基金项目(2014011021-3)

2016-02-25 修改日期:2016-03-12

C:7210

10.3969/j.issn.1005-9490.2017.02.016

TP274.2

A

1005-9490(2017)02-0342-04