一种航天型号软件RS422接口数据通信能力的测试装置

李晓燕 张恕明 李玉敏 翟景升

(中国科学院上海技术物理研究所,上海 200083)

装配·检测

一种航天型号软件RS422接口数据通信能力的测试装置

李晓燕 张恕明 李玉敏 翟景升

(中国科学院上海技术物理研究所,上海 200083)

为了保证基于RS422接口的软件数据通信能力,介绍了一种测试装置。该装置以FPGA测试板卡(下位机)与计算机(上位机)相结合,通过调节波特率、通信数据帧格式、通信数据包之间时间间隔等,实现型号软件数据通信能力的检测。

RS422接口;数据通信能力;FPGA测试板卡

1 引言

航天型号电子系统软件需要综合考虑通信速率、可靠性、抗干扰、兼容性、可扩展性等要求,目前串行总线通信在航天电子系统中的应用非常普遍,其中平衡通信接口RS422在航天系统、自动化控制系统等领域获得了广泛应用[1]。航天型号软件通过RS422数据通信接口实现产品在轨工作状态的控制、接收地面数据注入以及通过遥测参数下传产品的工作状态,进行故障诊断和在轨维护。航天型号软件通过FPGA实现RS422接口通信,一般不直接采用IP核,而是通过端口模拟实现。因此为了适应复杂的应用环境,保持通信线路的健壮性非常重要。地面开展故障模拟是全面软件测试的必要保证,在软件数据通信功能的测试中,需要模拟通信链路上可能的各种异常情况的输入激励,并考核软件的设计余量,充分检验软件RS422通信接口的纠错容错能力。

从航天型号软件的测试需要出发,提出一种针对RS422通信协议的测试装置,该装置具有波特率可调、通信数据格式可调、数据长度可变等功能,可全面有效地测试RS422接口软件的数据通信适应能力。

2 系统框图和功能简介

测试装置的系统框图如图1所示。其工作原理为:测试装置的构成分为两部分,计算机(上位机)和FPGA测试板卡(下位机)。FPGA测试板卡和上位机计算机的连接是通过异步串行通信接口RS232。上位机与下位机的通信内容主要包括三个部分:a.计算机向FPGA测试板卡发送其接收待测设备数据的波特率、数据位宽、校验位等配置信息;b.计算机发送待处理的故障数据至FPGA测试板卡,数据包括发送的数据内容以及数据帧格式;c.待测设备发送数据的读取是通过FPGA测试板卡处理之后发送到计算机进行显示。

FPGA测试板卡和待测设备之间的连接接口为RS422异步串行全双工通信接口。FPGA测试板卡建立起计算机与待测设备之间的数据通信测试,实现对待测设备软件RS422接口数据通信能力的检测。

3 基于Python的上位机程序设计

该装置测试命令的发送和测试数据的存储和显示是由人机交互界面上位机完成的,上位机界面和功能采用Python工具语言编写。借助Python工具主要实现两个功能,显示控制界面和串口通讯。在Python中分别添加wxPython控件“wx”和串口实现控件“serial”以支持功能实现。

3.1 上位机界面

如图2所示,串口设置包括COM口设置(下位机连接计算机的接口),波特率、数据位、校验位、停止位设置。其中波特率的设置是以文本框输入的形式,这种设计目的是可以给特定波特率加入不同程度的偏移量,使得波特率偏移测试更加全面。发送窗口的设置可以根据测试需求发送不同长度,不同数据内容的数据包,同时可以调节数据包之间的发送时间间隔。

3.2 上位机与FPGA测试板卡之间的通信

上位机与FPGA测试板卡之间的通信是通过RS232接口实现的,Python具有成熟的异步串行通信控件serial支持RS232通信的实现。上位机与FPGA测试板卡之间的数据帧格式为:1位起始位,8位数据位和1位停止位,通信的波特率为115200b/s。

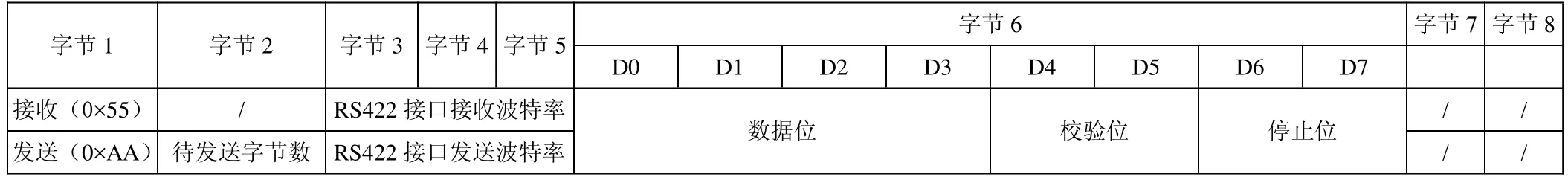

表1所示为上位机与测试板卡之间的通信数据包格式:一组数据包含8个字节,第1个字节是表示发送的数据是用于接收配置还是发送配置;第2个字节表示若为发送配置,拟发送的数据包数据个数,如果是接收配置此字节为0;第3、4、5字节表示发送接收的波特率;第6字节低四位表示发送接收数据帧的数据位,D4和D5表示接收和发送的校验位,D6和D7表示停止位位数。第7、8字节在发送配置信息时是没有意义,默认为0。上位机发送的故障注入数据也是以8个字节为一组数据以115200b/s的波特率发送至测试板卡,如果发送的字节数不是8的整数倍,以0填补空字节。

表1 FPGA测试板卡与计算机通信数据包格式

上位机接收来自测试板卡的数据,接收数据显示在通信界面的接收窗口。接收的数据同样以文本的形式存储在计算机内。

4 FPGA测试板卡

FPGA测试板卡主要有四个功能模块:a.接收来自上位机的发送接收配置信息;b.依照上位机的接口配置信息接收被测设备数据;c.对上位机的发送配置命令进行处理后发送数据至被测设备;d.向计算机发送接收到的被测设备RS422接口传输数据。

4.1 上位机配置信息解析

FPGA测试板卡在开始与被测设备通信之前,首先需要解析来自上位机发送的配置信息,获取与被测设备建立通信的依据。下位机接收到的上位机发送的配置信息共有 8个字节,接收的第 1个字节为“01010101”表示是接收配置,“10101010”表示后续是发送配置。若为接收配置,读取字节3、4、5、6配置相应RS422接收数据帧格式和波特率。若为发送配置,读取第2个字节作为接收上位机发送数据的依据,依据字节3、4、5、6配置相应的RS422接口发送数据帧格式和发送波特率。第1个字节既不是接收标志也不是发送标志,如果FPGA接收到的发送配置发送数据位未接收完整,那么作为待发送数据,FPGA根据发送配置再处理接收到的待发送数据,否则数据包无效不做处理。

FPGA测试板卡与待测设备通过RS422接口进行通信的数据帧配置,包括数据位、校验位、停止位的配置以及数据帧传输的波特率配置。图5所示为RS422异步接口的数据帧格式。其中,一帧数据包括起始位、数据位、校验位和停止位[2]。其中起始位(低电平)是表示通信的开始,起始位是必不可少的。起始位之后是数据的有效数据位,通常数据位由5、6、7或者8位组成。数据位之后是校验位,检验分为寄校验和偶校验,也可以没有校验位。最后是停止位(高电平),停止位的长度可以是1、1.5和2。

4.2 波特率生成单元

串行通信收发双方必须约定相同的速率进行串行通信,通过改变接收波特率,可以检测被测设备软件的波特率偏移容错能力。最常见的传输率有9600b/s、115200b/s等,航天软件中一般要求波特率偏移量在±1%范围内,都可以正常接收数据。

FPGA接收到的上位机波特率设置不能直接用于RS422数据接收发送,FPGA需依据上位机的波特率配置对时钟源进行不同系数的分频生成波特率时钟频率,再用于RS422接口的发送和接收控制。本设计采用FPGA时钟生成波特率时钟频率,系统外部全局时钟频率为50MHZ,波特率分频计算公式为:

通过FPGA系统外部全局时钟频率生成的RS422通信波特率存在误差。如图5所示,在波特率偏移±1%时,采用50MHz时钟源产生的波特率时钟频率的误差较大,100MHz时钟源时误差减小,当时钟源达到150MHz时,分频时钟微小偏移量的误差可以忽略不计。因此,为了软件通信能力测试的准确性,本文采用150MHz作为FPGA的主时钟[3]。采用的硬件是Cyclone系列FPGA(EP1C6T144C8),拥有2个锁相环(PLL),可以进行灵活的倍频和分频,能够将系统外部50MHz时钟倍频到150MHz[4]。

表2 波特率分频系数产生的误差

4.3 FPGA接收RS422接口数据

为使FPGA程序清晰,RS422数据接收采用状态机实现,图4所示为RS422接口数据接收状态机。接收状态机一共有五个状态,等待起始位(r_start)、监测起始位有效性(r_start_c)、等待接收(r_wait)、接收数据暂存(r_sample)、接收停止位(r_stop)。

系统上电复位后进入等待起始位状态(r_start),一旦起始位接收到低电平信号,进入起始位监测状态(r_start_c),时钟计数器开始计时。为了使接收数据更加稳定,接收模块接收数据时采用中间采样的方法。当时钟计数器计时等于半分频系数时,起始位仍为低电平,进入数据接收状态(r_wait)。进行计数,等待计满分频系数,进入数据位采样状态(r_sample),同时判断采集的数据位是否已达到数据帧的长度。进入数据位采样状态(r_sample)之后进行数据采集暂存,完成后无条件进入等待数据接收状态(r_wait),等待下个数据位的到来。若判断数据位达到了数据帧长度,进入接收停止位(r_stop),等待停止位接收完成后,状态转回等待起始位(r_start),等待下一帧起始位。

图5所示为数据接收的仿真结果图。

4.4 FPGA通过RS422接口发送数据

FPGA串行数据发送设计相对简单,发送实现的状态机如图6所示。

发送状态机共有六个状态,空闲状态(s_idle)、起始位(s_start)、数据位发送等待(s_wait)、数据位读取发送(s_excute)、校验位发送(s_check)、停止位发送(s_stop)。

发送允许标志位无效时,状态机处于空闲状态(s_idle)。当发送允许标志置位,状态及进入发送起始位(s_start),发送起始位低电平,进入数据位发送等待状态(s_wait),计时时钟开始计数。在发送等待状态(s_wait),当时钟计数等于分频系数时,进入数据位发送状态(s_excute);当数据发送位数等于上位机发送的数据位配置时,如果发送数据有校验位进入校验位发送(s_check),否则进入停止位发送(s_stop)。当在发送执行状态(s_excute),读取发送数据位到RS422发送端口,完成后无条件进入等待发送(s_wait)。当在校验位发送状态(s_check),发送数据位计算后获得的校验位值,并开启时钟计数器,当计时等于分频系数时发送停止位。进入停止位发送(s_stop),FPGA发送高电平到RS422发送端口,开启停止位状态时钟计数器,计数器的计时依据上位机发送配置计1、1.5、2个分频系数。发送完成后进入空闲等待(s_idle),等待发送允许标志位置位。

5 结束语

本文所设计的软件RS422接口数据通信能力测试装置,用户不再受传统测试板卡的约束,可以根据软件性能测试的需求,给常用的RS422接口串行数据波特率加入偏移。通过设置数据帧和数据包的数据格式,测试软件的数据通信故障处理能力。并且能够随意设置数据包之间的传输速率,测试软件的数据接收刷新能力。

本文所设计的数据通信能力测试装置能够全面有效地测试航天型号软件RS422接口数据通信的适应能力,后续可以扩展到其他航天型号软件通信协议,如常用的CAN、1553B等。

1 李斯贝,谭超,高山,等.星上RS422接口电路的建模与仿真[J].航天器工程,2011,21(1):109

2 索义芳,高飞,孙磊.基于FPGA的差分RS422串行收发模块的设计实现[J].微计算机信息,2010,26(12):125~126

3 蔡德胜,方寿海.一种高可靠性的计算机与FPGA串行通信的实现[J].现代电子技术,2011,34(19):85~86

4 梁九鹏,李永亮,郑佳.FPGA器件中PLL的设计应用[J].无线电工程,2007,37(9):62

Testing Device for Data Communication Capability of RS422 Interface inAerospace Software

Li Xiaoyan Zhang Shuming Li Yumin Zhai Jingsheng

(Shanghai Institute of Technical Physics of the ChineseAcademy of Sciences,Shanghai 200083)

In order to guarantee the capability of the data communication of software based on RS422 interface,a testing device is introduced.The device consists of a FPGA card(slave computer)and computer(master).The detection for the data communication capability of aerospace software with RS422 interface is realized by adjusting the baud rate, data frame format and time interval in data packets.

RS422 interface;data communication capability;FPGA test card

李晓燕(1990-),工程师,生物医学工程专业;研究方向:FPGA软件测试。

2016-12-05