低电源电压带隙基准电路设计

魏榕山,钟美庆

(福州大学 物理与信息工程学院,福建 福州 350116)

低电源电压带隙基准电路设计

魏榕山,钟美庆

(福州大学 物理与信息工程学院,福建 福州 350116)

提出一种应用于低电源电压供电的带隙基准电路的解决方案。通过增加升压模块解决电流模带隙基准电路只能应用于1 V电源以上电压的难题。文中在0.8 V电源电压供电下设计带隙基准电路。对电路进行理论分析与设计,采用SMIC 0.18 μm CMOS工艺模型,通过Cadence公司Spectre工具对所设计电路功能与性能进行仿真验证,仿真结果表明,在-45~125 ℃温度范围内,输出电压变化为2.085 mV,温漂系数为10.6 ppm达到了设计要求。

带隙基准;低电源电压;升压电路

带隙基准电路可以在一定温度及电源电压变化范围内提供稳定的电压或电流,其广泛应用于各类模拟电路、数模混合电路以及片上系统中,其精度直接影响整体电路的性能。各类高精度高性能集成电路中必须引入带隙基准电路。

传统结构的带隙基准电路提供基准输出电压约为1.26 V,其所需电源电压更高[1-2]。即使低压结构带隙基准电路对电源电压的要求一般需要在1 V以上[3-4]。

但是随着CMOS制造工艺的特征尺寸变小,特别是随着电池式供电设备的使用,为了实现低功耗电路的目的,片上电路系统的供电电压越来越低,低电源压带隙基准电路的设计刻不容缓[5]。

本文通过仿真并分析低电压下带隙基准电路设计难点及原因,提出了一种应用于电源电压下的实现带隙基准电路的解决方案,即使用Doubler电路对超低电压进行倍压,然后用该电压给带隙基准电路进行供电,实现带隙基准电压输出。

2 低压结构带隙基准电路

带隙基准基本原理是通过一个与温度呈负相关系数的电压VBE与另外一个与温度呈正相关系数的电压ΔVBE按照一定比例相叠加,得到一个与温度不相关的电压VREF。其中,VBE是晶体管连接成二极管形式的基极-发射极电压,具有负温度系数;ΔVBE是两个双极晶体管在不同电流下的基极-发射极电压差,具有正温度系数[6]。

传统结构的带隙基准电路带隙基准电压为

VREF=VBE+17.2VT

(1)

其中,VT为热电势;VREF约为1.26 V。式(1)决定了传统结构的带隙基准电路不适合用在低电源电压情况。

为了在低电源电压下得到稳定的电压参考源,1999年,Banba等人在JSSC杂志上发表了一种适合低压工作的电流模结构电路文章,也称为Banba结构,得到了广泛应用。图1是电流模式带隙基准电路的原理图[7]。三极管Q1和Q2发射结面积比为1:N。Q1、Q2、R1、R2、R3、M1、M2及运放A组成了带隙基准的核心电路。运放工作在深度负反馈状态,其正向、负向输入端处于箝位状态,使A点电压和B点电压相等,即

VA=VB

(2)

VA=VBE1

(3)

VB=VR2=VBE2+VR

(4)

这样通过电阻R3上的电流为

(5)

通过电阻R2上的电流为

(6)

保证M1、M2、M3的宽长比一致并处于饱和区,各支路的电流相等。输出基准电压为

VREF=IR4×R4=(IR2+IR3)×R4

(7)

要使输出基准电压与温度无关,即对式(7)求偏导数,令其为零。将式(5)和式(6)代入,得

(8)

图1 Banba结构带隙基准电路

上述结构经在低电源电压时有较多应用,但是其并不能适用于超低电源电压供电情况[8],如电源电压为0.8 V甚至更低。因为:

(1)双极性晶体管的的基极发射极电压在低温情况下具有较高的电压。图2为SMIC 0.18 μm工艺中双极性晶体管在恒定电流1 μA的情况下的基极发射极电压随温度变化曲线。从图中可知基极-发射极电压在-40~125 ℃范围内可能高达820 mV;

图2 基极发射极电压随温度变化

(2)在上面的原理分析中,其中一个关键假设是M1、M2、M3的宽长比一致,并处于饱和区,使各支路的上的电流相等,这就需要使这3个晶体管具有良好的匹配关系。在超低电源电压供电时,晶体管的过驱动电压过小,会导致M1、M2、M3的镜像电流误差显著加大,严重影响带隙基准电路的性能。

3 Doubler电路

Doubler电路可以实现对电源电压进行倍压输出,如图3所示[9-10]。

图3 Doubler电路

图4 时钟时序

当S1为1时,MN1和MN3导通,MP1和MP3截止,电源给电容C1充电;当S1为0时,MN1和MN3截止,MP1和MP3导通,C1给Cout充电,输出电压约为2倍电源电压。同理当S2为1时,MN2和MN4导通,MP2和MP4截止,电源给电容C2充电;当S2为0时,MN2和MN4截止,MP2和MP4导通,C2给Cout充电,输出电压约为2倍电源电压,实现倍压功能。

4 电路仿真与验证

从上文的分析中可知,在超低电源电压供电时,带隙基准电路的设计是个严峻的挑战。本文提出一种应用于电源电压为0.8 V的带隙基准电路,并验证其功能。本设计采用SMIC 0.18 μm工艺,用Candence软件进行仿真验证。

先对0.8 V的电源电压通过Doubler电路进行倍压。低压电源通过Doubler电路后,其输出电压幅度约为2倍的电源电压大小,该电压能够满足大部分带隙基准电路要求。本次设计用此电压为Banba结构带隙基准电路供电,如图5所示[11]。

图5 总体结构

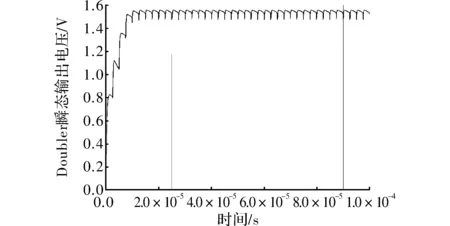

图6为本次设计Doubler电路驱动带隙基准电路时的瞬态输出电压曲线。Doubler电路输出电压经过一段时间后基本稳定,输出电压平均值为1.548 V,纹波峰峰值为81.3 mV,纹波频率为2倍时钟频率。

图6 Doubler瞬态电压输出曲线

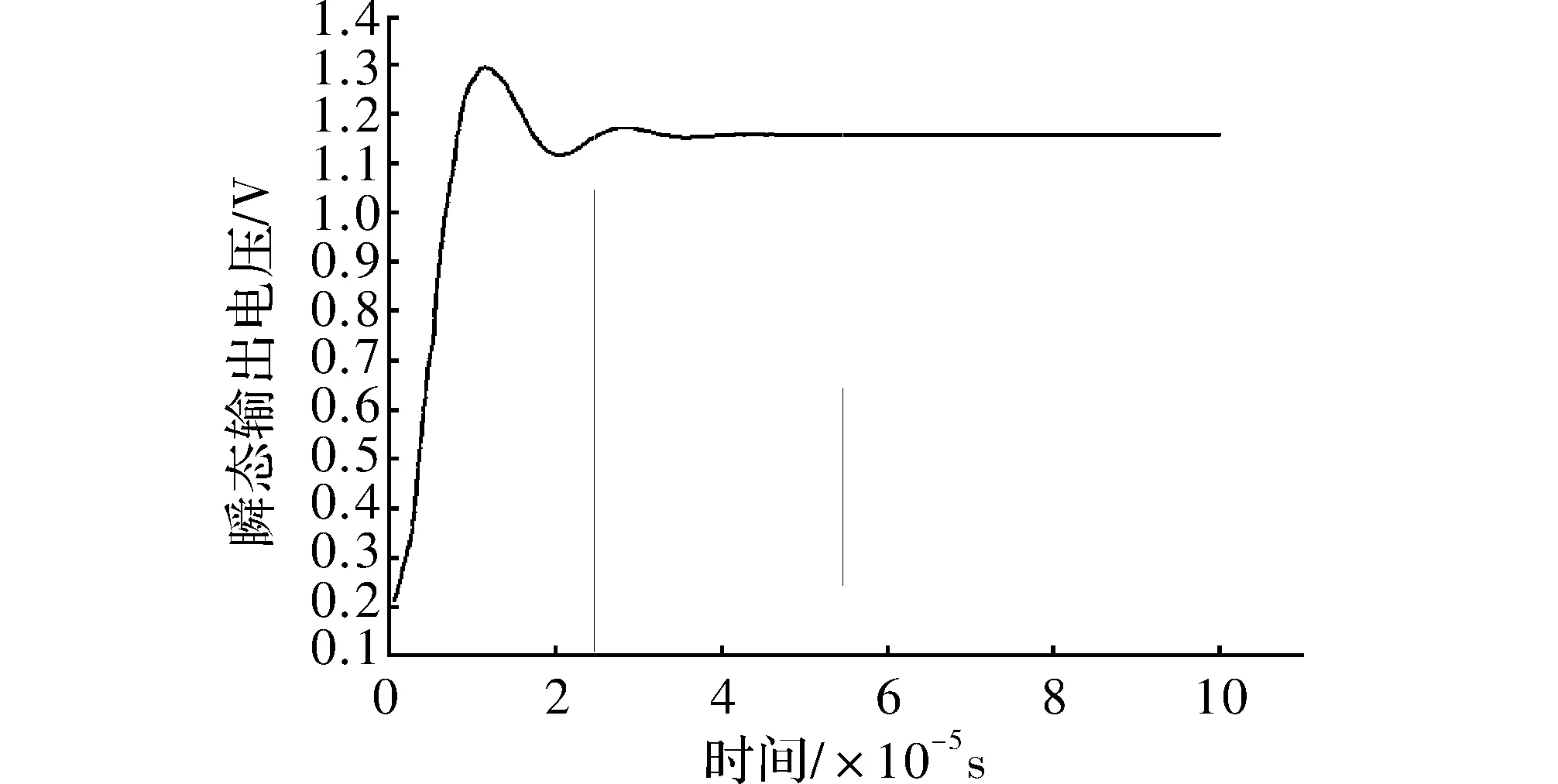

用Doubler输出的电压为Banba结构带隙基准电路供电。保证M1、M2、M3管具有较大的过驱动电压,实现较高的PSRR,可以抑制Doubler输出电压的纹波。图7为采用Doubler供电时带隙基准电路瞬态输出曲线。从图中可知在电路稳定后,基准电压上也存在随2倍时钟频率周期变化的波动,但变化幅度控制在205 μV范围以内,不影响大多数时候的应用。图8为采用Doubler供电时,输出基准电压随温度的变化曲线。从图4可知最大温漂为2.085 mV,即10.6 ppm。

图7 瞬态基准电压输出曲线

图8 基准电压输出温度曲线

表1给出了本设计与文献[12~15]的性能比较。从表中可以看出,本文提出的方式能够保证带隙基准电路基本性能,且满足较低电源电压输入的应用,符合设计预期与初衷。文中选取的电源电压是0.8 V,但是实际上,该方式可以对更低的电压进行倍压,然后选择低压结构的带隙基准电路进行基准电压输出,有更广泛的应用。

表1 带隙基准电路性能比较

5 结束语

文中提出一种应用于低电源电压带隙基准电路的解决方案,且在0.8 V的电源电压供电下,对该方案进行仿真验证。仿真结果表明,该方式能够满足低电源电压下带隙基准电路应用,具有较强的实际应用参考价值。

[1] Brokaw A. A simple three-terminal IC bandgap reference[J].IEEE Journal of Solid-State Circuits,1974,9(6):188-189.

[2] 幸新鹏,李冬梅,王志华.CMOS带隙基准源研究现状[J].微电子学,2008,38(1):57-63.

[3] Vittoz E,Neyroud O.Alow-voltage CMOS bandgap reference[J]. IEEE Journal of Solid-State Circuits,1979,14(3):573-579.

[4] 秦波,贾晨,陈志良,等. 1V电源非线性补偿的高温度稳定性电压带隙基准源[J].半导体学报, 2006,27(11):2035-2039.

[5] 杨永豪. 一种低电压CMOS带隙基准源的分析与设计[J].电子科技,2005(12):20-23.

[6] Razavi B. Design of analog CMOS integrated circuits[M].New York:McGraw-Hill,Inc,2001.

[7] Banba H, Shiga H, Umezawa A, et al. A CMOS bandgap reference circuit with sub-1-V operation[J].IEEE Journal of Solid-State Circuits,1999,34(5):670-674.

[8] Becker-Gomez A, Lakshmi Viswanathan T, Viswanathan T R. A low-supply-voltage CMOS sub-bandgap reference[J].IEEE Transactions on Circuits & Systems II Express Briefs,2008,55(7):609-613.

[9] Favrat P, Deval P, Declercq M J. A high-efficiency CMOS voltage doubler[J].IEEE Journal of Solid-State Circuits,1998,33(3):410-416.

[10] Roscoe N M, Judd M D. Optimization of voltage doublers for energy harvesting applications[J].Sensors Journal IEEE,2013,13(12):4904-4911.

[11] 杨喆,姚素英,徐江涛.一种用于升压型DC/DC变换器的低压带隙基准源[J].微电子学,2007,37(1):105-108.

[12] 陈文韬,邓婉玲,黄君凯. 一种高精度二阶温度补偿带隙基准电路设计[J].固体电子学研究与进展, 2014(5):470-475.

[13] Andreou C M, Koudounas S, Georgiou J. A novel wide-temperature-range, 3.9 ppm/ C CMOS bandgap reference circuit[J].IEEE Journal of Solid-State Circuits,2012,47(2):574-581.

[14] Zhou Z K, Shi Y, Huang Z, et al. A 1.6-V 25- A 5-ppm/ C curvature-compensated bandgap reference[J].IEEE Transactions on Circuits & Systems,2012,59(2):677-684.

[15] 刘春娟,王永顺,刘肃. 高精度低噪声基准电压源的设计[J].固体电子学研究与进展,2011,31(6):624-629.

Design for a Low Supply Voltage Bandgap Reference Circuit

WEI Rongshan, ZHONG Meiqing

(School of Physics and Information Engineering, Fuzhou University, Fuzhou 350116, China)

A solution applied to low supply voltage bandgap reference circuit was proposed. It aimed to solve current mode bandgap reference circuit that can be only applied to 1 V supply voltage problem by increasing the booster module. This paper took a low supply voltage of 0.8 V as an example to design the bandgap reference circuit. The SMIC 0.18μm CMOS process model was used to design circuit and the Cadence Spectre tool was used to simulate the circuit function and performance.The simulation results showed in a temperature range of -45 ~ 125 ℃, the output voltage variation range was 2.085 mV, which meant the drift coefficient was 10.6 ppm.

bandgap reference;low supply voltage;booster circuit

2016- 03- 03

国家自然科学基金资助项目(61404030)

魏榕山(1980-),男,博士,副教授。研究方向:微纳电子器件与集成电路设计。钟美庆(1990-),男,硕士研究生。研究方向:集成电路设计。

10.16180/j.cnki.issn1007-7820.2017.01.010

TN432

A

1007-7820(2017)01-034-04