基于FPGA的探地雷达数据采集系统设计

程昌彦,李太全

(长江大学 物理科学与光电工程学院,湖北 荆州 434020)

基于FPGA的探地雷达数据采集系统设计

程昌彦,李太全

(长江大学 物理科学与光电工程学院,湖北 荆州 434020)

基于探地雷达数据采集系统对数字化集成化的需求,提出了一种基于FPGA的数据采集系统的设计方案,用于采集探地雷达回波信号。FPGA直接通过控制精密延时芯片MC100EP196对采样脉冲进行延时调整,控制采样脉冲的延时步进,系统最大采样率理论值达到100 GS/s,并且时窗可以任意调整。给出了设计方案,对系统的工作原理和特点进行了详细的说明。通过与示波器对比以及分析采集测试效果图,得到稳定有效的数据,实际采样率达到20 GS/s,证明了系统的可行性。

探地雷达;等效采样;延时芯片;高速数据采集;MC100EP196;AD9629

0 引言

探地雷达是一种有效的浅层地质勘探仪器,该仪器多为冲击型探地雷达,其回波是一个宽度为纳秒或亚纳秒级的窄脉冲[1],在电路上难以实现对此快速的信号直接采样分析,现多以等效采样方法采集雷达回波[2]。等效采样需要一个精确的时间步进取样脉冲,产生该脉冲的方法有快慢斜波信号法[3],通过比较器产生相位步进的取样脉冲,也有使用电容充放电原理的方法[4],这些方法借助比较器产生取样脉冲,容易受到电源电压、噪声干扰等影响产生时钟抖动,降低模数转换的信噪比,特别是对高频信号的取样,信噪比下降更加严重。还有使用多片ADC交替采样的原理[5-6],但需要占用更多的布局空间和成本,对时钟同步性要求也较高。本文提出的方法是直接通过控制数字延时芯片产生步进延时来等效采集雷达回波[7],通过FPGA调整时窗,是一个集成化的数字系统,具有结构简单、成本低、调节控制方便和抗干扰性强等优点。

1 等效采样原理

常用的等效采样有随机等效采样和顺序等效采样,随机等效采样的触发点与采样脉冲之间的时间间隔是随机的,而顺序等效采样则是步进增加的[8],本设计采用顺序等效采样的原理。顺序等效采样原理如图1所示。

设待测信号为S(t),该信号为周期重复信号,周期为T,则S(t)=S(nT+t)。令采样周期为Ts=T+Δt,在t=0时采样取得信号S0=S(0),在t=T+Δt时取得信号S1=S(T+Δt)=S(Δt)。依次类推,在t=n(T+Δt)时取得信号为Sn=S(nT+nΔt)=S(nΔt)。最后得到样品序列S0,S1,S2…Sn。显然,这些样品与周期Δt的实时采样结果相同。若以Δt为周期的采样满足采样定理,则上述的等效采样就能够取得S(t)的完整信息[9]。决定采样率的大小的关键在于能否得到足够小的Δt。在探地雷达系统中,发射机的触发信号是一个重复信号,接收到的回波也是在一个时窗中的重复信号,雷达回波信号可以看成是相对于启动脉冲的重复周期性信号,所以用顺序等效采样的方法来分析雷达回波信号是一个可行的方法。

图1 等效采样原理

2 数据采集系统设计

由图1可知,数据采集系统中提高采样率的关键就是如何得到精细稳定的延时Δt。可控延时芯片MC100EP196具有最小步进延时10ps的精度,通过控制10位数据输入端口,可在0~1024ps内调节延时量。其最大等效采样率理论上可达100GS/s,完全满足雷达回波数据采集系统对采样率的要求。

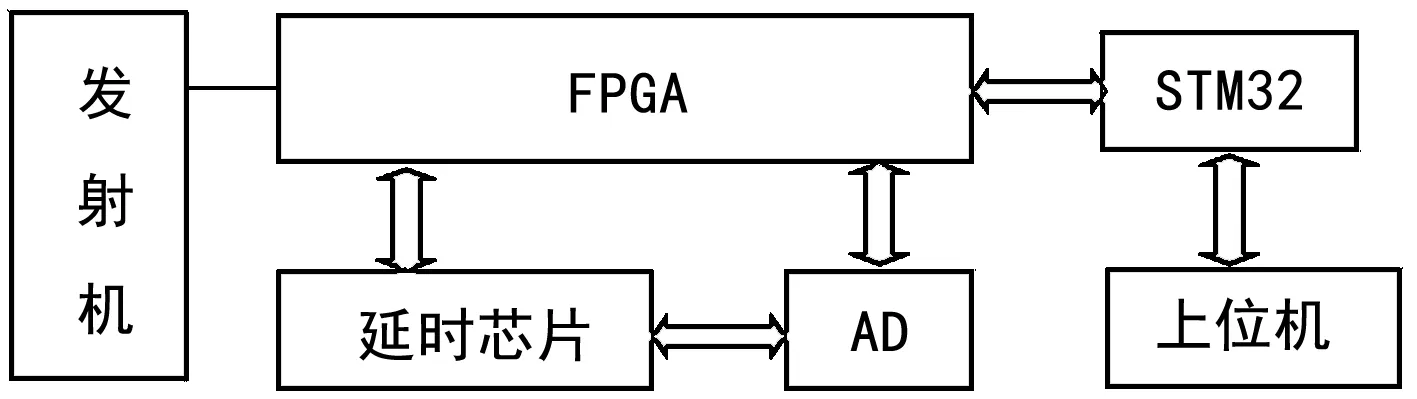

数据采集系统结构如图2所示,其中控制延时步进和时序同步是设计的关键。

图2 数据采集系统结构

数据采集系统主要由FPGA、可控延时芯片MC100EP196和12位模数转换器AD9629组成。双口RAM存储AD9629采集的数据,时基控制模块控制整个系统的时序同步,读控制模块和写控制模块实现双口RAM的读写,由时基控制模块保证读写时序的同步。DCO为AD9629的数据输出时钟信号,每采集到一个数据DCO产生一个脉冲信号,写控制模块通过DCO读取AD9629的数据到双口RAM。ARM控制器一方面连接数据与上位机之间的通信,由上位机通过启动命令启动系统工作;另一方面将采集到的数据通过USB传输到上位机。

在启动脉冲的作用下,时基控制部分开始工作,由同一个100MHz时钟源通过计数器分频产生2路脉冲Tri_clk和Delay_clk。Tri_clk脉冲作为发射机发射脉冲源的触发脉冲,Delay_clk脉冲经过MC100EP196精确延时后作为数据的采集脉冲,触发脉冲与采集脉冲的时间间隔为:

Δts=ta+N×Tc+nΔt。

(1)

式中,ta是为了补偿2个脉冲之间的固有延迟,用于调整直达波的位置;Tc=10 ns,是100MHz时钟源的周期;Δt是MC100EP196的精确延时步长。通过调整n可以调整Δts的精细时间,调整N实现Δts的10ns步进。

脉冲Delay_clk通过MC100EP196的精细时间调整由输入控制信号D_port[0∶9]控制,设D_port[0∶9]的值为Delay_reg,初始值为0,写控制模块检测到DCO脉冲后使能写信号w_en,将数据存入双口RAM中,并且双口RAM的存储地址增加一个单位。采集下一个点时Delay_reg值增加Delay_step,直到Delay_reg值为1 000时完成了一次10ns时窗的精确采样。

数据采集过程的时序示意图如图3所示,启动脉冲和Tri_clk频率都为200K,Delay_clk为25M,Tri_clk是一个相位可调整的脉冲信号。当Delay_reg的值达到最大值1 000时数值清零,完成了一次10ns时窗的采样,此时为了扩大时窗,Tri_clk相位向前调整一个10ns,进行下一个10ns时窗的采样。通过不断的调整Tri_clk,使最终的采样时窗范围以10ns步进可调。因为时基控制是由同一个时钟经过计数器分频得到的,所以三路脉冲信号满足同步关系。

图3 时窗调整时序

改变Delay_step的值,可以改变采样率,假如Delay_step的值为1,那么Δt以最小步进10ps进行采样,即达到最高采样率100GS/s,Tri_clk的频率只有200K,时窗动态调整范围大,所以该系统是一个采样率高,时窗调节范围大的数据采集系统,非常适合应用于像探地雷达这样需要高采样率、时窗调节范围大的数据采集系统中。

3 测试结果分析

数据采集端接上发射机触发脉冲输出端,直接测量触发脉冲的波形,采样率调整到10GS/s,时窗为100ns,测量结果如图4中实线所示。安捷伦宽带数字示波器测量结果如图4中虚线所示,两者测量的结果基本吻合。将发射机触发脉冲输出端和数据采集端输入端分别接偶极子天线,采样率调整到20GS/s,时窗为100ns,测试2根天线直接耦合的结果,测试效果如图5所示,从图5中可以明显看到回波信号耦合情况。由测量结果可知,本设计的数据采集系统可以实现对探地雷达对回波信号的采集。

图4 采集系统输出和示波器测试比较

图5 探地雷达测试效果

4 结束语

前端采集电路设计和制作电路板时应注意对高频信号的处理以及抗电磁干扰的措施[10-12],采样率越高,系统对时钟稳定性要求越高,任何外部干扰和内在因素都可能造成时钟抖动过大,导致测量精度误差[13-14],使用高性能的时钟芯片可以有效降低时钟抖动。系统达到100GS/s最大采样率还需要后期改善,但20GS/s的采样率已足够满足探地雷达对回波采样精度的要求。高速数据采集系统在探测仪器应用中意义重大,本文设计并实现了最大等效采样率达到20GS/s的数字化数据采集系统,成功地采集了探地雷达回波信号,装置稳定可靠,结构简单,所用器件很少,成本较低,在采样率和时窗的调整上具有灵活性的特点,可广泛应用于脉冲超宽雷达和一些对便携式数字化以及对低成本有要求的数据采集系统。

[1] 郭宜龙.探地雷达脉冲源和数据采集系统[D].成都:电子科技大学,2013:9-12.

[2] 李太全,陈 威.地质雷达测控系统的FPGA实现[J].自动化仪表,2014,4(21):18-20.

[3] 屈义萍,刘四新,徐晓林.脉冲探地雷达回波信号数据采集的设计[J].电子设计工程,2010,4(22):58-60.

[4] 马 凯,王彦文.可编程数字控制精密延时电路设计[J].中国测试,2014(1):93-94.

[5] 黄武煌,王厚军,叶 芃.一种高速全波形采集与高精度定位技术研究[J].仪器仪表学报,2013,34(1):73-79.[6] 秦国杰,刘国满,高梅国,等.一种时间交替ADC时间失配误差自适应校正方法[J].仪器仪表学报,2013,34(12):2 730-2 735.

[7] 李太全,孙先松.基于SOPC组件的高精度可编程延时电路[J].微计算机信息,2008,24(29):291-292.

[8] 金 星,黄 伟.基于FPGA的随机等效采样模块设计[J].电测与仪表,2009,46(6):17-20.

[9] 周 维,王 赤,田 茂,等.基于等效时间采样的探地雷达回波信号采样方法研究[J].雷达科学与技术,2004,2(1):43-47.

[10] 陈 伟,黄秋元,周 鹏.高速电路信号完整性分析与设计[M].北京:电子工业出版社,2009.

[11] 谢跃雷,晋良念,欧阳缮,等.一种基于FPGA的超宽带雷达数字接收机[J].现代雷达,2014,36(1):62-65.

[12] 杨扩军,田书林,蒋 俊,等.基于TIADC的 20GS/s高速数据采集系统[J].仪器仪表学报,2014,35(4):841-849.[13] 伍翠萍.低抖动时钟稳定电路研究与设计[D].成都:电子科技大学,2008:1-5.

[14] 陈红梅,邓红辉,张明文,等.高速低抖动时钟稳定性电路设计[J].电子测量与仪器学报,2011,25(11):966-971.

程昌彦 男,(1992—),硕士研究生。主要研究方向:地质仪器。

李太全 男,(1961—),博士,副教授,硕士研究生导师。主要研究方向:地质勘探仪器、地下电磁波传播特性和目标反演。

Design on Data Acquisition System of Ground Penetrating Radar Based on FPGA

CHENG Chang-yan,LI Tai-quan

(SchoolofPhysicsScienceandOpto-electronicEngineering,YangtzeUniversity,JingzhouHubei434020,China)

In view of the requirement of data acquisition system of ground penetrating radar (GPR) for digital integration,this paper proposes a design scheme of data acquisition system based on FPGA for GPR echo signal acquisition.The FPGA is used to perform delay adjustment for sampling pulse by controlling directly sophisticated delay chip MC100EP196 to control sampling pulse delay step.The maximum theoretical value of system sampling rate is up to 100 GS/s,and can adjust the time window.The design block diagram is given,and the operating principle and characteristics of the system are described in detail.By comparing with the oscilloscope and analyzing acquisition test results,the stable and effective data are obtained,and the actual sampling rate is up to 20 GS/s,which proves the feasibility of the system.

ground penetrating radar (GPR);equivalent sampling;delay chip;high-speed data acquisition;MC100EP196;AD9629

10.3969/j.issn.1003-3106.2017.04.07

程昌彦,李太全.基于FPGA的探地雷达数据采集系统设计[J].无线电工程,2017,47(4):28-30.

2017-01-10

国家自然科学基金资助项目(41474117)。

TN959

A

1003-3106(2017)04-0028-03