基于FPGA的可调节FIR滤波器的设计与实现

郑艳芳,唐海娣,李雪宝

(1.江苏科技大学,江苏 张家港 215600;2.江苏耐维思通科技股份有限公司,江苏 张家港 215600)

基于FPGA的可调节FIR滤波器的设计与实现

郑艳芳1,唐海娣2,李雪宝1

(1.江苏科技大学,江苏 张家港 215600;2.江苏耐维思通科技股份有限公司,江苏 张家港 215600)

基于灵活自适应的空口波形技术F-OFDM(Filtered OFDM)是现代通信技术的研究热点,设计并实现可调FIR滤波器是实现该技术的核心工作之一。本文设计的基于FPGA的可调节FIR滤波器系数的自适应调整是通过控制算法对信道中的信号进行快速检测,然后将结果和滤波器的输出结果进行差值计算进行反馈调节。利用Quartus II和DSP Builder设计基于FPGA的16阶系数可调FIR滤波器,给出核心模块的设计电路图和仿真结果。仿真结果表明:基于灵活自适应空口波形技术可以在FPGA上实现,而且由于FPGA具有天然的并行性,实际的通信系统中可以采用并发模式进行,达到提高信号传送速率的目的。

可调FIR滤波器;FPGA;F-OFDM

0 引言

4G移动通信方兴未艾,业界对于5G移动通信技术的讨论已经如火如荼。作为移动通信领域“皇冠”上的一颗明珠,基于灵活自适应的空口波形技术和成倍提升频谱效率的多址技术SCMA(Sparse Code Multiple Access)成为业内人士关注的焦点,其中,优化频带资源的利用率是F-OFDM的核心。人们在研究算法优化的同时,也在关注算法的硬件实现。FPGA(Field Programmable Gate Array)在能耗、成本、运算速度等方面具有得天独厚的优势, 已经被广泛应用于各种数字信号处理和数字通信领域。本文重点研究F-OFDM核心技术之一的可调FIR滤波器,设计并实现基于FPGA的可调节FIR滤波器。

近年来,基于FPGA的数字滤波器研究已经取得了很多成果[1-14],其中文献[14]的设计理念最接近本文。然而,从现有的文献来看,并没有可供参考的用于基于自适应的空口波形技术的方法,此外,本文设计流程和侧重点与文献[14]也是不同的。本文第1节为核心模块设计,第2节为MATLAB仿真结果和系统仿真结果,第3节给出了基本结论和下一步研究目标。

1 基于FPGA的可调FIR滤波器设计

该设计总体思路是:利用输入波形的各项参数,借助MATLAB中的FDAtool工具计算出FIR滤波器所需参数,存入RAM。滤波器核心模块读取参数信息,调节滤波器的截止频率等参数,调节该模块的功能。

利用DSP_Builder开发核心滤波器模块的流程示意图如图1所示。

图1 DSP_Builder的开发流程图

最基本的FIR滤波器的系统函数为:

(1)

可以用卷积表示为:

y(n)=x(n)*h(n)

(2)

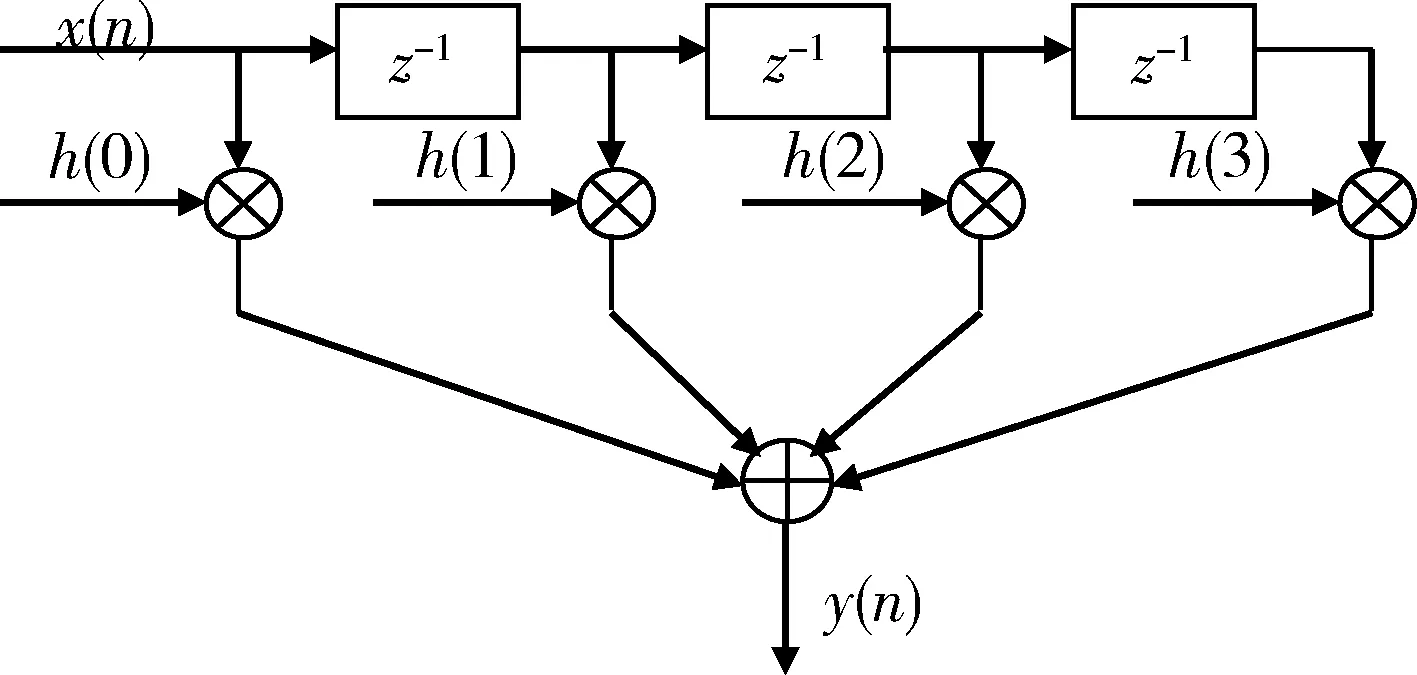

例如,一个典型的直接型4阶FIR滤波器,其表达式[11]可写为式(3):

h(n)=h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+h(3)x(n-3)

(3)

在图2中,总共存在3个延时单元、4个乘法器和一个4输入的加法器。

图2 直接型4阶FIR滤波器的信号流图

如果使用普通的数字信号处理器来实现这个4阶FIR滤波器,只能用串行的方式顺序地执行延时、乘、加操作。这必须用到多个指令周期,而无法在一个指令周期内完成。但是如果采用FPGA来实现,就可以利用FPGA指令可以并行的优点,在一个指令周期内得到结果。

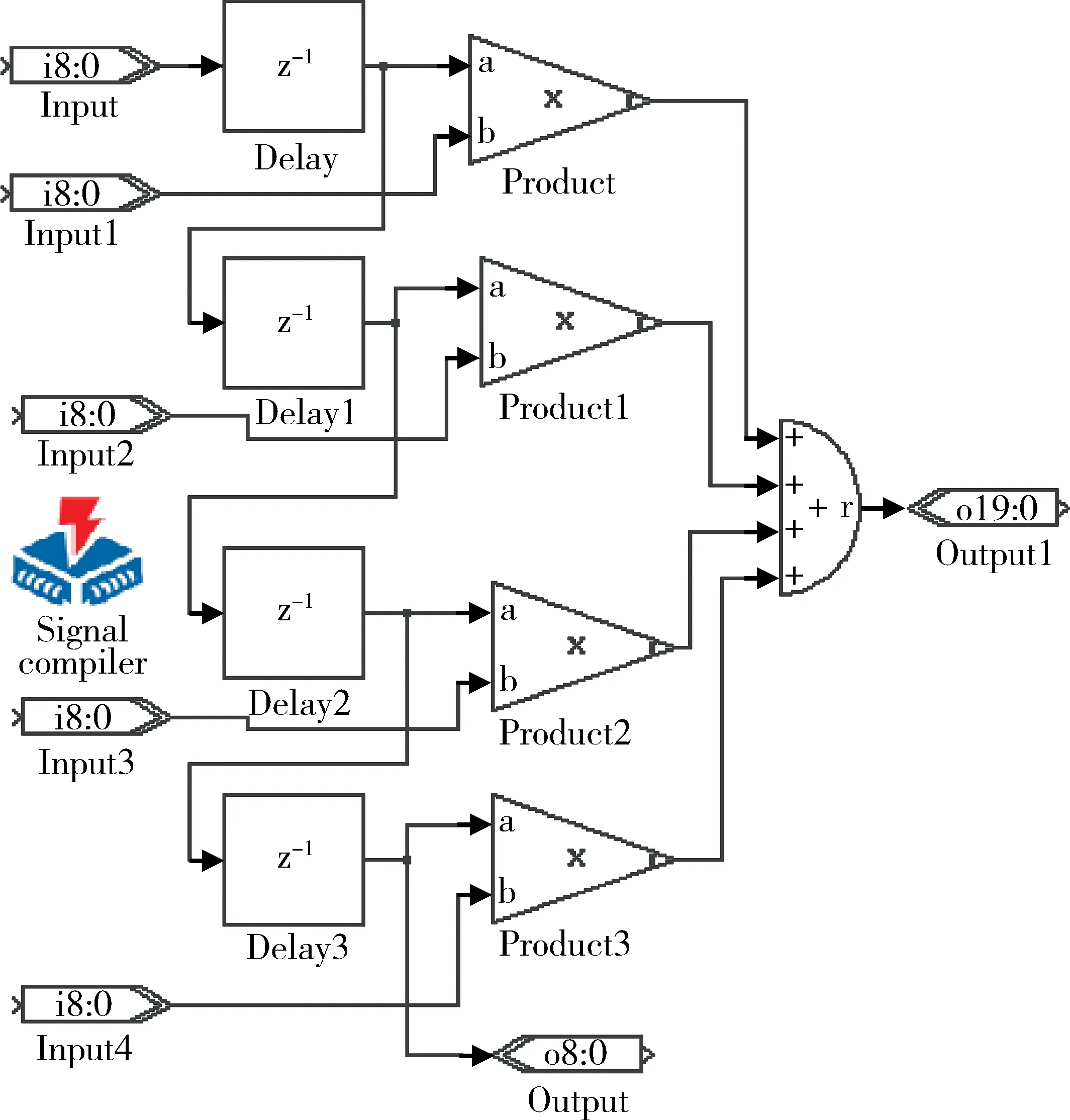

根据公式(3)和图2,可以在Simulink中用DSP_Builder里的相关器件画出一个图3所示的4阶FIR滤波器模型。

图3 4阶FIR滤波器的模型图

图3中“Delay”为延时单元,“Product”为乘法器单元,“ParallelAdderSubtractor”为加法器单元,“Input”与“Output”分别为输入输出。

(1)设计4阶FIR滤波器子系统

新建一个文件,将子系统模块(Subsystem)放入文件中,双击打开子系统模块,将上面已经设计好的4阶FIR滤波器放进去,并对端口进行修改。修改后的Subsystem模块有5个输入和2个输出,“input”与“output”都修改为“Altbus”(因为它们不再作为主输入端口,而是作为子系统的传输端口)。

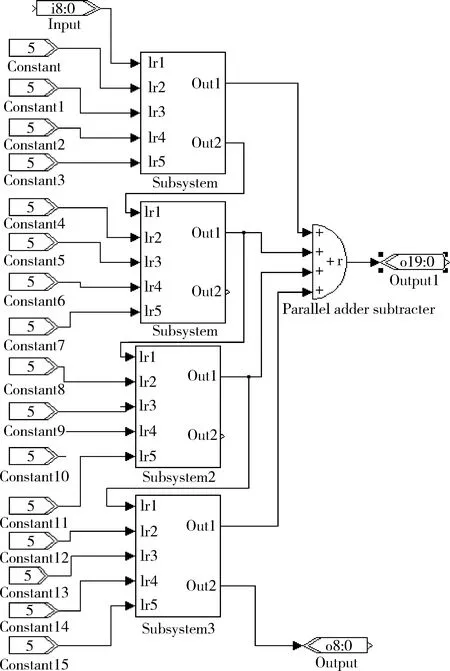

(2)设计16阶FIR滤波器

4阶子系统完成后,按照图4搭建一个16阶的FIR滤波器。其中Constant模块的初始值为5,需要另外计算,下文讲解如何计算Constant值。

图4 16阶FIR滤波器的模型图

(3)计算Constant的值

Constant的值就相当于h(n),是决定FIR滤波器具体性能的重要参数,该值为滤波器要调节的核心参数,它是通过滤波器的输出和输入信号的差值得到的。

(4)导出参数

点击左上角的File,单击Export,跳出Export界面,点击下方的Export按钮,可以将16个参数导出到MATLAB的主窗口。

(5)将参数填入FIR滤波器的模型中

在MATLAB仿真阶段,该参数可以手动输入到FIR滤波器Constant模块中,这样便完成了一个16阶低通FIR滤波器的设计。在系统设计阶段,步骤(4)计算结果会暂存在定制的RAM模块中。

2 设计验证

2.1 核心模块仿真

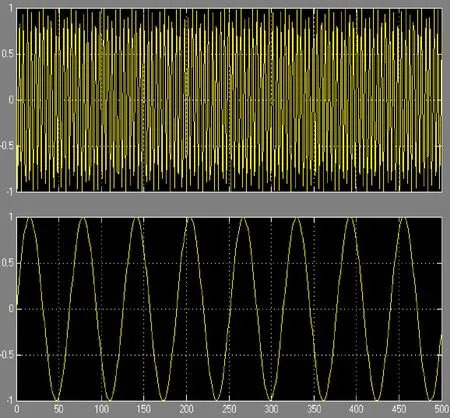

为了验证设计的16阶FIR滤波器正确与否,需要进行仿真。为此,给滤波器的输入端加上一个混合信号,混合信号包含一个40 Hz的高频信号和一个0.013 Hz的低频信号,两个信号由Add模块相叠加,再分别加上示波器模块“Scope”来显示波形结果。FDAtool设置就和上文所述相同,并将所得数据填入Constant模块中,仿真时间设为500 s。

图5的上方为40 Hz的波形,下方为0.013 Hz的波形。图6的上方为输入的混合信号波形,下方为滤波器输出波形。将两幅图比较可以明显看出,高频信号40 Hz的波形被滤除,滤波器输出的是低频的0.013 Hz的信号。

图5 输入波形图

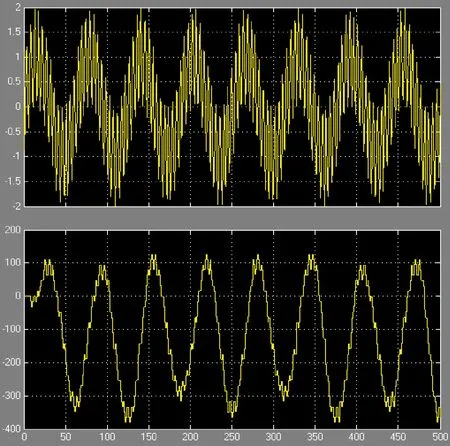

图7 滤波器的仿真结果注:clk:时钟信号;wav_signal:低频信号(目标信号);wav_noise:高频信号;wav_add:两波形叠加信号;wav_filter:输出信号

[5] 高耀鸿. 基于FPGA的FIR低通滤波器[D].长沙:湖南大学,2012.

[6] 张驰. 基于Matlab的FIR滤波器设计及FPGA实现[J]. 应用科技,2005,33(6):84-86.

[7] 孙耀奇. 基于Matlab和FPGA的FIR数字滤波器设计及实现[J]. 现代电子技术,2008(11):89-92.

[8] 张园. 基于MATLAB和QuartusⅡ的FIR滤波器设计与仿真[J]. 电子工程师,2008,34(2):25-27.

[9] 阿依夏木·力提甫. 一种基于MATLAB及FPGA的FIR低通滤波器的设计与实现[D]. 乌鲁木齐:新疆师范大学,2011.

[10] 陈雁. 用MATLAB设计及FPGA实现FIR滤波器的方法[D].北京:北京航空航天大学,2003.

[11] 宋千. 基于FPGA的FIR滤波器高效实现[J]. 信号处理,2001,17(5):385-391.

[12] 马桂芳.基于FPGA和DSP Builder的FIR数字滤波器设计[J]. 常州工学院学报,2011,24(5):23-26.

[13] 彭雪峰. 基于MATLAB与QuartusⅡ的FIR滤波器设计与验证[J]. 电子设计工程,2009,17(11):118-124.

[14] 陈虹,崔葛瑾.基于FPGA的系数可调FIR滤波器设计[J].实验室研究与探索,2008,27(6)47-50.

图6 输出波形图

2.2 系统仿真

(1)将将mdl文件编译生成VHDL语言;

(2)计算输入信号和滤波器输出的差值,将该值存入RAM;

(3)读入RAM数据,逐渐确定滤波器截止频率;

(4)仿真。

为了验证所设计的可调FIR滤波器的正确性,设计了基于上述模块的低通滤波器进行波形的仿真。两个正弦波叠加形成输入信号,一个25 kHz信号人为标记为噪声信号,另一个4 kHz作为目标信号,程序调节滤波器的截止频率到4.5 kHz。仿真结果如图7所示。由图中可知,该滤波器滤除了高于截止频率的信号部分,保留了低于截止频率的信号部分,因此滤波器功能正确。调节输入信号和截止频率后,结果也能达到如图7所示的效果。

3 结论

本文FPGA设计了一种可调FIR滤波器,利用DSP Builder结合MATLAB的优势将该滤波器的设计简化为MATLAB Simulink设计,大大缩短了设计时间。未来将进一步完善可调滤波器设计,探索基于FPGA的可调FIR滤波器在实际通信系统中的实现方法,进而提高通信系统效率。

[1] 李彬. FIR数字滤波器的FPGA实现技术研究[D]. 成都:西南交通大学,2004.

[2] 刘朋全. 基于FPGA的FIR数字滤波器的设计和实现[D]. 西安:西北工业大学,2006.

[3] 杨娜. 基于MATLAB与DSP的自适应滤波器设计与实现[J]. 微型机应用,2015,34(21):16-20.

[4] 杜勇. 数字调制解调技术的MATLAB与FPGA实现[M]. 北京:电子工业出版社,2015.

Design of adjustable FIR filter based on FPGA

Zheng Yanfang1,Tang Haidi2,Li Xuebao1

(1.Jiangsu University of Science and Technology,Zhangjiagang,215600,China;2.Navston Limited Corporation,Zhangjiagang 215600,China)

F-OFDM is one of the key hotspots in modern communication system. Designing and instrumenting the adjustable FIR filter is certainly part of F-OFDM. In this paper, we design an adjustable FIR filter based on FPGA, and its filter coefficients can vary with the running difference between the output of filter and the frequency of input signal. We design the filter based on the Quartus II and DSP builder provided by Altera. The simulation results reveal that the techniques of F-OFDM can be instrumented on FPGA. In addition, since FPGA has its own ability of natural parallel computing, improving the running efficiency would come true on the FPGA.

adjustable FIR filter; FPGA; F-OFDM

TN713+.7

A

10.19358/j.issn.1674- 7720.2017.04.009

郑艳芳,唐海娣,李雪宝.基于FPGA的可调节FIR滤波器的设计与实现[J].微型机与应用,2017,36(4):29-31,35.

2016-09-19)

郑艳芳(1986-),女,博士,讲师,主要研究方向:检测、控制相关技术在世界领先的航海、航天终端仪器中的应用。

唐海娣(1979-),女,硕士,工程师,主要研究方向:世界领先的航海通信导航技术数字化港口解决方案。

李雪宝(1986-),通信作者,男,博士,讲师,主要研究方向:大数据处理、并行计算、云计算等在世界领先的航海、航天终端设备中的应用。E-mail:lixuebao@ynao.ac.cn。