基于IIC总线的串行数据通信

吴海洲

摘要:IIC总线结构简单且易于实现,广泛应用于设备或模块间的连接。简述了IIC总线的硬件结构和串行通信控制协议,协议规定了完整的起始状态和读写时序。根据协议要求,采用控制状态机的方式设计了一种通用的IIC接口模块,介绍了读写数据过程和状态机的转换方式。经过验证,FPGA与外部设备间通过IIC总线数据传输,响应速度快,符合设计要求。

关键词:IIC总线 FPGA 状态机

中图分类号:TN402 文献标识码:A 文章编号:1007-9416(2016)11-0018-01

1 引言

串行总线是连接外部设备的一个串口总线标准,可以简化系统的硬件设计、减小设备体积、提高设备的可靠性,并且易于进行系统的更改和扩充。常用的串行总线有:IIC(Inter IC BUS)总线、单总线(1-WIRE BUS)、SPI(Serial Peripheral Interface)总线及Microwire/PLUS等。由于IIC总线的连线少并且可以直接用导线互联外部设备,许多半导体厂商都引进了此项总线技术,并推出了不少带IIC总线接口的芯片或模块。本文即论述基于FPGA的IIC总线接口,实现设备间的串行数据通信。

2 IIC总线简介

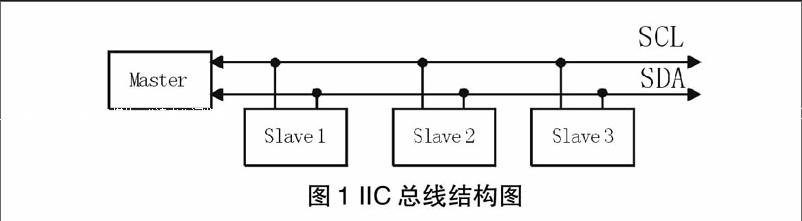

IIC总线是PHILIPS公司开发的一种简单、双向、二进制、同步串行总线,可解决各个设备间的串行通信[1]。物理上IIC总线只有两根双向信号线,分别为数据线SDA(Serial Data)和时钟线SCL(Serial Clock)。如图1所示。

IIC总线通过上拉电阻接正电源。总线空闲时,两根线均为高电平。总线上的任一设备输出低电平都会使总线的信号变低,即个设备的SDA及SCL都是线“与”的关系。每一个接入IIC总线上的设备都有其在总线上的唯一地址。每一个设备都可以作为主机(Master发起通信)或是从机(Slave应答通信)。

3 IIC总线通信控制协议

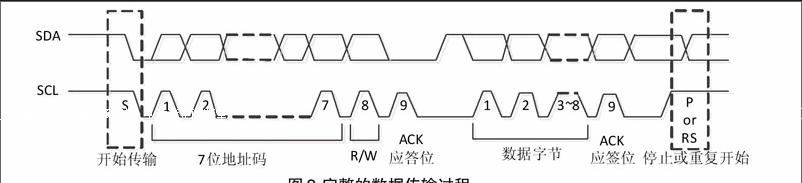

IIC通信协议是基于起止状态识别的[2],传输起始信号为在SCL为高电平时SDA出现一个从高到低的跳变沿,停止信号为在SCL为高电平时SDA出现一个从低到高的上升沿,应答信号为SCL为高电平时SDA为低电平,非应答信号为SCL为高电平时SDA也为高电平。正常数据传输bit序列时,与应答和非应答的时序相同。在其他时刻,只有SCL为低电平时,SDA才能发生变化,否则,SDA的电平需保持不变。

IIC总线的数据传输是以字节为单位进行的,在一个起止状态之间,可传输若干个数据字节,每个数据字节间有确认信号。确认信号在SDA上以每一个8bit字节后面的第9bit表示。图2表示一个完整的IIC总线数据传输过程。IIC发出起始信号后,从器件发出7位寻址地址和1位读写标志位R/W,当R/W为0时表示写状态,当R/W为1时表示读状态。有应答信号后开始传输数据,否则就停止发送,直到发送停止信号后结束数据传输过程。

4 IIC接口模块设计

本文以某FPGA及其外接设备为例,对完整的基于IIC总线的串行数据通信进行说明。FPGA和外接设备以IIC总线进行连接,FPGA为主设备,外接设备为从设备,IIC总线的控制器工作在FPGA中。IIC控制器的主要作用是发送控制命令到从设备和读取从设备的状态。主要包括三部分:控制状态机、写过程和读过程。其中读、写过程的时序需遵守IIC总线通信控制协议。

写过程:①FPGA在检测到总线空闲时,发送S信号占用总线;②FPGA给总线发送一个地址字节,其中包括7位地址信号和1位写信号(R/W信号为0);③外设检测到总线上的地址与自己的地址相同时,发送一个应答信号ACK;④FPGA收到ACK后发送第一个数据字节;⑤外设收到数据字节后发送ACK表示继续发送或其他操作;⑥重复④、⑤,FPGA发送完全部的数据后发送一个停止位P,结束写过程并释放总线。

读过程:①FPGA在检测到总线空闲时,发送S信号占用总线;②FPGA给总线发送一个地址字节,其中包括7位地址信号和1位写信号(R/W信号为1);③外设检测到总线上的地址与自己的地址相同时,发送一个应答信号ACK;④FPGA收到ACK后释放总线,开始接收第一个数据字节;⑤外设收到数据字节后发送ACK表示继续发送或其他操作;⑥重复④、⑤,FPGA接收完全部的数据后发送一个停止位P,结束写过程并释放总线。

控制状态机:根据IIC总线通信控制协议克制,IIC总线有六个固定的状态,分别为:空闲(Idle)、开始(Start)、写数据(Write)、读数据(Read)、应答(ACK)停止(Stop)。如图3所示。

①空闲状态:当无数据传输时, IIC总线处于空闲状态;②起始状态:当收到开始信号后占用总线,转入读、写数据状态;③写数据状态:串行数据传输写入外设,完成后进入应答状态;④读数据状态:FPGA读取总线上的串行数据,完成后进入应答状态;⑤应答状态:根据外设的响应情况转入停止状态或空闲状态;⑥停止状态:数据传输结束,释放总线,转入空闲状态。

5 FPGA原型验证

本设计选用的FPGA是ALTERA公司的FPGA产品EP3C80F780I7N,采用Verilog语言描述[3],在Quartus II平台上完成了系统的仿真、综合、映射、布局等。在仿真结果正确后,通过编程器下载到FPGA中进行系统调试。该模块性能稳定,响应速度快,完成了基于IIC总线协议的串行数据通信,符合设计要求。

6 结语

本文介绍了一种基于FPGA的IIC总线串行数据通信方法,用控制状态机的模式,采用Verilog语言设计完成了IIC总线控制模块,并进行了FPGA硬件验证,结果表明本设计满足IIC总线通信控制协议,设计简单,易于实现。

参考文献

[1]Philips Semiconductors. The IIC- Bus Specification[M] Version2.1,2001:6-19.

[2]董秀洁,王莉萍.基于FPGA的IIC总线控制器设计[J].中原工学院报,2014,25(1):11-14.

[3]朱诚诚,石晶晶,陈斯,张萌.基于Verilog HDL的IIC总线IP设计[J].电子器件,2015,38(6)1336-1340.