DDR2 SDRAM控制器接口的FPGA设计及实现

王 梦,蒋 峰,谢浩澜

(中南林业科技大学 计算机与信息工程学院,长沙 410001)

DDR2 SDRAM控制器接口的FPGA设计及实现

王 梦,蒋 峰,谢浩澜

(中南林业科技大学 计算机与信息工程学院,长沙 410001)

DDR2 SDRAM是第二代双倍数据传输速率同步动态随机存储器,以其大容量、高速率和良好的兼容性得到了广泛应用;DDR2芯片的控制较为复杂,为了解决DDR2芯片的驱动及功能验证问题,在介绍了其特点和工作机制的基础上,提出了一种简化的工作流程图,进而给出该控制器的总体设计、FPGA器件的引脚分配及验证方法;其中验证方法采用Verilog HDL硬件描述语言构建了DDR2控制器IP软核的测试平台,通过ModelSim软件对DDR2仿真模型测试无误后,再使用QuartusII软件的嵌入式逻辑分析仪工具SignalTap II抓取FPGA开发板实时信号;开发板上的验证结果表明:DDR2芯片初始化成功;其引脚上有稳定的读写数据;在双沿时钟频率200 MHz下,写入数据和读出数据一致。故DDR2控制器设计达到要求,且控制器接口简单、工作稳定、移植性强。

FPGA器件;DDR2 SDRAM接口;芯片驱动; 验证

0 引言

随着集成电路技术的发展,应用于军工或民用领域的图形处理、视频监控电子产品,对存储器的速度要求越来越高,可以说存储器的速度是决定系统性能的关键因素之一。而DDR/ DDR2/DDR3 系列的SDRAM动态存储器由于能在时钟的正负边沿进行读写操作,以其高速、大容量、运行稳定及高性价比等优点成为了目前存储器的主流。由于DDR2 的操作时序很复杂苛刻,造成对应的DDR控制器电路结构也比较独特。因此很多FPGA厂商基于其可编程芯片的丰富软硬件资源,如产生多路高频率时钟信号的集成PLL锁相环,支持SSTL1.8 V、TTL3.3 V等多电平的可编程I/O端口,自带的无缝连接的图形化时序约束软件工具等,设计了DDR2/DDR3存储控制器IP核。其中以ALtera公司设计的存储控制器效率最高、使用较为广泛,用户只需了解FPGA芯片引脚专用于连接DDR2/DDR3引脚的功能及存储器的工作机制,即可实现DDR控制器的设计。

基于上述分析,本文研究了 DDR2 SDRAM 的工作原理及控制器IP核解决方案, 采用altera公司的DDR2 IP核,在现场可编程门阵列芯片FPGA中实现DDR2 设计,并利用嵌入式逻辑分析仪SignaltapII软件工具验证了200 MHz双边沿时钟主频下的硬件测试结果。

1 DDR2的工作机制

1.1 DDR2的初始化

DDR2 SDRAM加电后必须按照规定的步骤完成初始化。在初始化的过程中应注意对模式寄存器(MR)和扩展模式寄存器(EMR)的配置。通过初始化可以完成对CAS延迟,突发长度,突发类型,输出驱动能力,片上端接电阻(ODT)值,伴随CAS的附加延迟,片外驱动器校准等配置。初始化完成后,DDR2 SDRAM进入正常工作状态,此时可以通过地址线指定的单元进行读写操作。

1.2 DDR2的读写操作

DDR2写操作前需要对指定段(bank)的行(row)进行激活,每个bank只允许打开1行,即只允许对打开的行进行读写操作,如果要对同一bank中的其他行进行读写操作,则必须先用预充电(precharge) 命令关闭已经打开的行,再用激活(active)命令打开需要进行读写操作的行,实际上是锁定行地址,再进行突发操作,对连续地址单元进行读写操作。

2 DDR2 SDRAM控制器的总体设计

通过对DDR2工作机制的分析可知,DDR可以实现多种操作,如上电(PowerUp)、空闲等待(Idle)、寄存器配置(MRS,Mode Register Set)、动刷新(Refresh)、 预充电(Precharge)、激活(Activate)、读/写操作(Read/Write)等[1-2]。要使这些操作按照严格的时序要求,彼此之间进行转换,需要通过状态机来实现控制,简化的DDR2工作流程如图1所示。而DDR2控制器则要在不同状态下,发布不同的控制命令对存储器进行操作,控制命令实际上是 DDR2存储器引脚信号cke、cs、cas、ras 、we的组合。

图1 简化的DDR2工作流程图

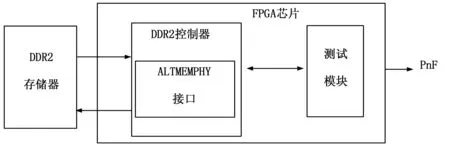

本文设计的DDR2 SDRAM控制器完成的主要功能是对Micron公司MT47H64M16型号的DDR2芯片初始化;在读写操作时将用户端单时钟沿触发的数据转换为DDR2存储器的双沿时钟触发的数据,即将DDR2 SDRAM复杂的读写时序转化为用户简单的读写时序,使用户像操作普通RAM一样控制DDR2 SDRAM。同时,控制器还要产生周期性的刷新命令来维持DDR2 SDRAM 内的数据不需要用户的干预。由于是采用Altera公司提供的IP核altmemphy 来设计,该控制器通过用户接口建立FPGA内部控制逻辑到DDR2的连接,用户不需要管理DDR2初始化、寄存器配置等复杂的控制逻辑,只需要控制用户接口的读写操作。这样可以缩短开发周期,减少设计人员的工作量,简化了系统设计。因此控制器实际上在用户与存储器间充当一个接口的作用,如图2所示。

用户只需利用quartusII的Megawizard宏功能向导选择对应的芯片型号, 总线宽度和速度级别,并设置CAS延迟、突发长度、引脚分配等参数,即可生成DDR2 SDRAM控制器, 包括HDL代码和sdc时序约束等文件。由图2控制器的逻辑框图可知,设计者可以通过控制器的用户端接口直接操纵内存控制器。控制器工作时,由用户设计端提供一个50 M的系统开发板标准时钟,控制器内的altmemphy核则产生一个100 MHz和200 Mhz的时钟信号phy_clk、ck分别给用户端、存储器端,由于控制器接口两端的工作频率不一样,故数据处理速率也不一致,用户端数据处理速率应为存储器端的两倍。例如,用户端的读写数据宽度为128位时,则依靠ck时钟上下边沿触发读写操作的存储器端的数据宽度dq为32位。当存储器信号reset复位延时一段时间,FPGA的pll锁存的时钟信号即可稳定下来后, 用户设计者只要接受到接口的反馈的init_done信号有效,即知道存储器初始化完成。至于初始化的序列命令都由控制器接口自动产生。接下来,用户设计端即可在phy_clk接口时钟的控制下通过发出读/写(read_req /writ_req)请求来写入或读出数据。由于DDR2的突发读写长度为8个字,可能用户端读写时,存储器并不一定处于空闲状态,因此要通过控制接口反馈的local_ready来判断。另外读数据存在列选择信号cas_n有效到数据读出来存在若干周期的延时,因此还需通过接口反馈的data_valid来判断存储器数据是否读出到总线上。

3 DDR2控制器的FPGA引脚分配及验证

在FPGA中,为了更好地发挥出DDR2的性能, DQS、DQ、DM等引脚都需要连接指定专用FPGA管脚[3],且对DDR引脚的分配做相关的约束。即DDR2 SDRAM都只能按照DQ/DQS组连接。一个完整的DQ/DQS组应该包含DQ,DQS和DM三类信号。以EP4CE30 F484封装为例,该FPGA共有上、下、左、右4个侧边,每个侧边又都分有2个区(bank)[4]。不同区可以用不同的IO电压,可以用不同的IO标准,同一BANK中只能用相同电压IO标准。故本设计将所有的DDR2引脚都分配在下侧边的bank3,bank4区。由于DDR2采用1.8 V的SSTL电平进行数据传输,为了实现更高的信号频率,输入信号需要和一个参考电压(VREF)进行比较输出后才被认为是实际输入,故DDR2所在FPGA 的Bank电压必须是1.8 V,所以DDR2引脚的IO电平标准设置为 SSTL-18 ClassI ,可通过在硬件电路上将FPGA芯片2个区所有的VCCIO、VREF引脚分别接入1.8 V、0.9 V电源来加以保障。

对于CycloneIV E型号的FPAG芯片,每个区有9个DQ引脚和对应的DQS(数据选通) 、DQM(数据屏蔽)引脚。DQS XY的引脚分布,如图3所示, 其中X代表DQS组的序号,Y代表这个组所在的侧边(SIDE),由图可知,左边和右边支持的DQS较少,分别只有4个,而上边和下边则较多,分别有6个。所以在选择FPGA与DDR2相连的边时,对较多的DDR引脚DQ组,应尽量约束在FPGA芯片的上侧边或是下侧边区域。另外提供给内部锁相PLL的晶振时钟clk及DDR的时钟CK、ck_n也必须采用FPGA的专用时钟引脚。而且DDR2颗粒的工作时钟使用差分时钟线ck、ck_n,能够减少共模干扰和时钟的抖动,提高了时钟信号的质量。而DDR2的地址和控制线在FPGA上没有专用管脚,可以任意使用其它普通IO管脚。 DDR2以外的管脚,如从晶振引入的时钟和全局复位信号等,只需要设定为默认的 2.5 V LVTTL(default)类型。

引脚分配好后,即可将程序下载到FPGA开发板中验证。开发板所采用的FPGA芯片型号为Cyclone EP4CE30,DDR2 存储芯片型号为 MT47H64M16,数量为两片,每片数据宽度为16 bit。软件编译工具采用 QuartusII 12.0,实时数据采集工具为quartusII自带的嵌入式逻辑分析仪SignaltapII 。

图3 Cyclone 4CE30芯片的DQS引脚分布图

DDR2验证平台结构如图4所示,主要包括DDR2 控制器和测试模块两部分。控制器由Quartus 软件的 Megacore 功能调用产生[5],其中PHY接口核保证读写过程中 DQS信号能够以精确的相位偏移发送和采集数据。测试模块主要提供读数据信号给整个验证平台。为了比较读写数据是否一致,可以将写入的数据同时放入FIFO中,然后将DDR2中读出的数据与FIFO数据进行比较。由于FIFO读写有延时,这样增加了测试程序时序控制的复杂性。而本文的测试模块则是采用线性反馈寄存器来产生伪随机的数据,该数据实际上是周期性重复出现的数据序列。写操作完成后再将数据从DDR单元中读出来时,即可直接与线性反馈寄存器的周期性数据比较。该验证平台可用Verilog HDL硬件描述语言构建,其功能可先通过ModelSim进行仿真。功能仿真时采用的DDR2模型由Micron公司提供。

图4 DDR2验证平台结构图

验证平台仿真无误后,下载到开发板,用SignalTAPII抓取的DDR2芯片数据波形如图5所示。观察到接口信号local_init_done跳为高电平时,表明DDR2已初始化成功;local_read_req 为高电平,表示DDR控制器发出读数据请求;dgen_load信号有效,则是控制线性反馈寄存器重复出现写入的周期性数据,以便比较读写是否正确。DDR反馈的local_rdata_valid有效,则表示经历了若干读周期延迟读出的数据开始出现在DDR引脚上。local_rdata为读出的数据,local_wdata为前面时间段写入的周期性数据。 比较结果则用pnf表示,其为高电平代表128位读数据都正确,即读写数据是一致的。

图5 SignaTapII实时抓取的DDR2接口的信号波形图

4 结论

通过对DDR2操作原理的分析,给出了DDR2控制器的设计及实现方法,并将DDR2控制器及其验证平台仿真通过后,下载到CycloneIV FPGA芯片的开发板上进行验证。通过逻辑分析仪工具SignaltapII抓取数据,能观察到存储器引脚上稳定的读写数据。在双沿时钟频率 200 MHz下,比较写入数据和读出数据,两者相同, DDR2控制器达到了设计要求。其工作稳定可靠,占用逻辑资源较少,且具有较高的可移植性以及简单的用户接口。在此基础上进行系统开发,将缩短系统开发周期,同时也降低了系统成本。

[1] Altera Corporation. External Memory Interface Handbook Volume 5[Z].Altera Corporation,2011.

[2] Micron Corporation. 1Gb: x4, x8, x16 DDR2 SDRAM[Z].Micron Corporation,2004.

[3] Altera Corporation. Pin Information for the Cyclone IV EP4CE30 Device (Version1.3)[Z].Altera Corporation,2014.

[4] Altera Corporation. Cyclone IV Device Handbook[Z].Altera Corporation,2011.

[5] 李 圣. DDR2 SDRAM控制器的研究与实现[D].西安:西安电子科技大学,2011.

Design and Implementation of DDR2 SDRAM Controller Interface on FPGA

Wang Meng, Jiang Feng, Xie Haolan

(Central South University of Forestry and Technology, Changsha 410001,China)

DDR2 SDRAM, as the second generation dynamic random memory, is applied widely because of its large capacity, high speed and good compatibility. Because the control of DDR2 chip is more complex, a simplified work flow chart based on its characteristics and working mechanism is proposed to solve the problem of chip driver and function verification for DDR2. Furthermore, the overall design,verification method and pin assignment of DDR2 controller in FPGA device are given. A test platform of the DDR2 controller IP core is built using Verilog HDL language in the verification method,which test successfully the simulation model of DDR2 by Modelsim software. And then the real-time signals in FPGA evaluation board are captured by adopting SignalTapII Logic Analyzer embedded in QuartusII software. The verification results in evaluation board show that the initialization of DDR2 chip is successful; pins of DDR2 chip have stable read and write data; the write data and read data are consistent under the dual edges clock with 200 MHz frequency. Therefore, the DDR2 controller meets design requirements, and it has simple interface, better stability and transplantablity.

FPGA device; DDR2 SDRAM interfaces; chip driver; verification

2016-04-02;

2016-07-22。

湖南省教育厅一般科研项目(13C1162);湖南省教育厅优秀青年项目(2015B251);中南林业科技大学校级大学生创新项目。

王 梦(1976-),男,博士,讲师,主要从事数字集成电路、半导体器件设计方向的研究。

1671-4598(2016)12-0119-03

10.16526/j.cnki.11-4762/tp.2016.12.034

TN47

A