基于FPGA的高速光幕同步系统设计与实现

徐 强,杨晓云,庄燕滨

(常州工学院计算机信息工程学院,江苏常州 213002)

基于FPGA的高速光幕同步系统设计与实现

徐 强,杨晓云,庄燕滨

(常州工学院计算机信息工程学院,江苏常州 213002)

常规光幕实现发射器和接收器双方信号的同步需要专用同步电缆来完成;针对这一缺点,提出了一种新的高速光幕同步方法,即在发射器的每个循环周期的第一通道发射光脉冲之前增加一个作为帧同步码的光脉冲段,接收端通过判断帧同步码的方式实现收发信号同步,这样便不再需要专用同步电缆,有效地节省了光幕同步系统成本;进一步地,采用新提出的高速光幕同步方法,基于FPGA技术,设计并实现了高速光幕同步系统的总体方案,硬件制作了可应用于高速运动物体的实时到位检测的高速光幕检测装置;实际工程应用表明,采用此方法的高速光幕检测装置,成本低,工作稳定可靠,捕捉与同步性能优良。

光幕;同步系统;FPGA

0 引言

光幕是一种特殊的对射式光电传感器,包含发射器、接收器和同步系统三大部分。发射器沿长度方向,每隔一定间距驱动一个红外管发出一束红外线,产生交流红外光脉冲,接收器按照相同间距安排相同数量的光接收管。工作时首先要实现发射器和接收器的信号同步,而后让发射器第一通道红外管发出光脉冲,让接收器对应的光接收管来寻找该脉冲,接着转向下一个通道,依次让所有通道的收发都完成后,再进行下一周期的工作。当一个周期扫描完成后,系统记录哪些通道光可以通过,哪些通道被遮挡,从而实现监测和测量等功能。

通常光幕收发两端的信号同步,是通过专用电缆来传递所需同步信号,以保证光幕可靠工作。在多篇文献中提出了各种光幕检测器的设计方案[1-6],也有文献提出在接收器上增加一个红外发射管,在发射器上增加一个光接收管,通过在接收端逆向发送光同步窄脉冲的方法,从而取消连接发射器和接收器的同步电缆[7]。文献[7]提出的这种无专用同步线的光幕检测器实现方案,存在下面两个问题:(1)额外增加了一对红外发射器和接收管,增加了成本和光路设计难度;(2)接收端发出的光同步脉冲使用100μs的窄脉冲,和发射器的16路红外光脉冲相同,容易误同步导致检测错误。

针对常规光幕实现发射器和接收器双方信号同步存在的缺点,提出了一种不需要专用电缆来传递所需同步信号的同步方案,有效地节省了光幕同步系统成本。进一步地,基于FPGA技术[8 10],设计并实现了高速光幕同步系统方案,硬件制作了一种适用于工程应用的高速光幕检测装置。

1 高速光幕同步方案

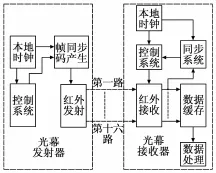

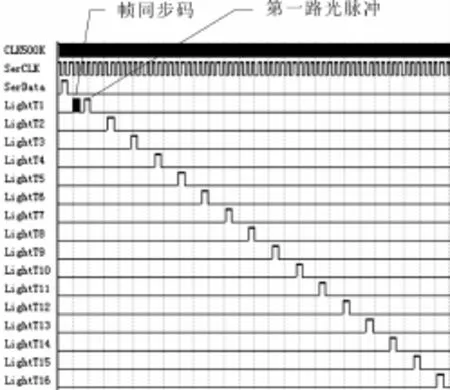

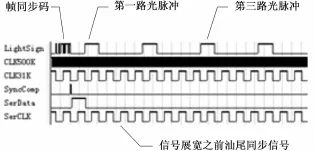

图1是本文提出的基于FPGA技术实现的高速光幕同步方案的系统框图。在光幕发射器端,新增了帧同步码产生电路,产生一个作为帧同步码的光脉冲段,并插入在每个循环周期的第一通道发射光脉冲之前;在光幕接收端,通过判断帧同步码的方式即可实现收发信号同步。相应地,光幕发射器的16路光脉冲串行工作时序图如图2所示。采用图1所示的高速光幕同步方案,从而有效地解决了发射器和接收器双方信号的同步需要专用同步电缆来完成的问题。

图1 高速光幕同步方案的系统框图

图2 高速光幕发射器光脉冲时序图

2 光幕发射器设计

由于本光幕装置在发送端和接收端之间没有使用专用同步电缆,而是在第一路发射光脉冲之前增加了一个帧同步码,来保证收发双方信号同步。确定了第一路光信号起始位置后,16路光脉冲信号以等宽形式串行工作,因此每次仅有一对发射管和接收管处于工作状态,需要判断的光脉冲也只有一路,从根本上排除了光散射而导致的级间信号干扰问题。

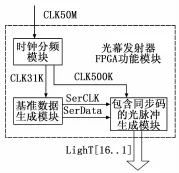

本装置中,光幕发射器核心芯片FPGA的内部功能如图3所示,由时钟分频模块、基准数据生成模块、包含同步码的光脉冲生成模块组成。

图3 光幕发射器FPGA内部框图

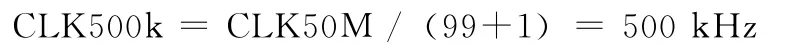

图3中时钟分频模块的主要功能是输入50 M时钟,产生两个时钟500 k Hz和31.25 k Hz。时钟分频模块的输入时钟CLK50 M来自50M的有源晶振,500 k Hz时钟输出端CLK500k连到光脉冲生成模块的时钟输入端,31.25 k Hz时钟输出端CLK31k连到基准数据生成模块的时钟输入端。时钟分频模块根据50 M晶振上升沿工作,每出现一次上升沿,七位计数总线加一,加到99后计数总线清零,计数总线最高位就是所需要的时钟CLK500k。

时钟分频模块还需要输出31.25 k Hz时钟,根据上面产生的CLK500k上升沿工作,每出现一次上升沿,四位计数总线加一,加到15后计数总线清零,计数总线最高位就是所需要的时钟CLK31k。

图3中基准数据生成模块作用是产生发射器所需要的时钟SerCLK和起始基准数据SerData,输入时钟CLK31k,来自时钟分频模块。

其工作过程如下:首先以CLK31k为时钟,进行模80计数,产生计数总线LEDCount[6..0];接下来判断LEDCount [6..0]的数值,当LEDCount[6..0]=1时,同步数据Ser-Data为1,其余任何计数状态Ser Data均为0,这样保证在每个循环周期起始出现一个瞬时高电平,输出时钟SerCLK与输入时钟CLK31k相同。

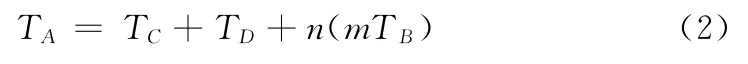

图3中包含同步码的光脉冲生成模块作用是产生16路红外发射管的导通控制信号,在第一路光脉冲之前产生16位帧同步码1001001101011101,光脉冲生成模块的输入发射光脉冲时钟为SerCLK,频率为31.25 k Hz,输入同步脉冲为Ser-Data,该信号在每周期起始出现一个瞬时高电平,这两个信号是由基准数据生成模块产生,另外还有一个由时钟分频模块产生的时钟信号CLK500k,用于同步码生成,光脉冲生成模块的输出信号是16路红外发射管的导通控制信号Light T [16..1]。

包含同步码的光脉冲生成模块的工作过程如下:首先以CLK500k为时钟,SerData为复位信号,设计停止型模64计数器,产生计数总线CLKCount A[6..0],根据CLKCount A [6..0]的数值,采用case译码语句产生串行的同步码SyncOut A。

当CLKCount A[6..0]=15时,SyncOut A=SyncData [15](同步码第15位);

当CLKCount A[6..0]=16时,SyncOut A=SyncData [14](同步码第14位);

当CLKCount A[6..0]=17时,SyncOut A=SyncData [13](同步码第13位);

依次类推。

当CLKCount A[6..0]=30时,SyncOut A=SyncData [0](同步码第0位);

然后光脉冲生成模块以SerCLK为时钟,Ser Data为复位信号,设计停止型模80计数器,产生计数总线CLKCountB [7..0];接下来判断CLKCountB[7..0]的数值,当CLKCountB[7..0]=3时,第一路红外发射管导通,当CLKCountB[7..0]=7时,第二路红外发射管导通,CLKCountB [7..0]的判断数值不断加四,依次类推,产生16路红外发射管的导通控制信号Light T[16..1],需要注意的是要在第一路发射光脉冲之前增加同步码。

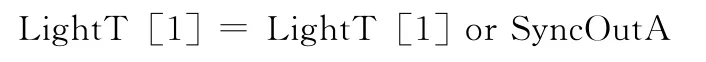

将第一路发射信号与串行同步码SyncOut A进行或运算,产生包含同步码的第一路发射光脉冲信号。

图4是包含帧同步码的第一路光脉冲时序图,是将图2中的第一路光脉冲放大,可以很清楚的看到在第一路光脉冲之前产生了16位帧同步码1001001101011101。

图4 包含帧同步码的第一路光脉冲时序图

3 光幕接收器设计

本装置中,光幕接收器使用光电池实现光电转换,产生微弱的电信号用运算放大器将其放大,经过模拟多路开关采用时分复用方式将16路模拟信号合并成一路模拟信号,将其转换为数字信号后送给FPGA。FPGA对信号进行运算处理,实现物体到位检测,输出开关信号。

本装置在发射器和接收器之间没有使用同步电缆,发射器和接收器各自根据本地晶振产生系列时钟,在没有锁相的情况下,收发双方即使采用相同程序,产生同样的时钟,也会有频率、相位上的偏差。如果以发射器时钟为基准,就会发现接收器的时钟在不断飘移。因此在没有同步线情况下,不进行锁相的话,用接收器时钟直接判断发射光脉冲,会导致大量运算错误,光幕根本无法正常运行。

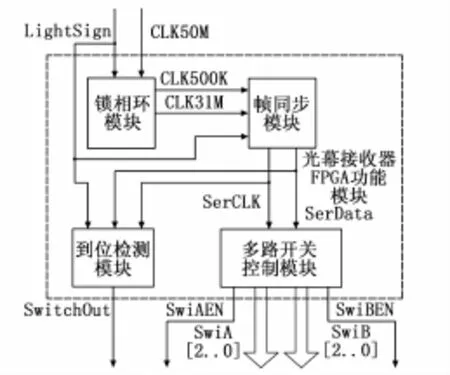

本装置中,光幕接收器FPGA的内部功能如图5所示,由实现位同步的锁相环模块、帧同步模块、多路开关控制模块、到位检测模块组成。

图5 光幕接收器FPGA内部框图

图5中锁相环模块由鉴相器、滤波器、数控振荡器组成,输入时钟CLK50M来自本地50 MHz的有源晶振,输入光脉冲信号LightSign来自模拟多路开关,经过锁相环位同步运算后,产生与发射器光脉冲相位相同的500 k Hz时钟信号CLK500K、31.25 k Hz时钟信号CLK31k。

锁相环模块的工作过程如下:首先使用两级D触发器实现鉴相器功能,光脉冲信号LightSign作为第一级D触发器的数据输入,CLK50M为第一级D触发器的时钟,第一级D触发器的数据输出连到第二级D触发器的数据输入,CLK50M反相后作为第二级D触发器的时钟,第二级D触发器的输出信号为LightSign A。第二级D触发器的输出信号LightSign A反相后与原始光脉冲信号LightSign进行与运算,就会产生光脉冲边沿信号LightSign Edge。

将边沿信号LightSignEdge经过积分器滤波后,连到数控振荡器的复位端,CLK50M连到数控振荡器的时钟引脚。数控振荡器根据50 M晶振上升沿工作,产生500 k Hz和31.25 k Hz两个时钟的过程与光幕发射器完全类似。

光幕接收器经过FPGA内部的数字锁相环模块后,就产生了与发射器相位完全相同的500 k Hz和31.25 k Hz时钟信号,并且在每个循环周期内提取16次边沿信号,实现快速锁相,这样就可以对光脉冲信号进行稳定判决。

图5中帧同步模块的输入时钟信号CLK500k、CLK31k来自锁相环模块,输入光脉冲信号LightSign来自模拟多路开关,捕捉到帧码码型信号1001001101011101,便进行n次校验,均正确后,认为收发同步,进入系统同步工作状态,输出同步数据SerData和同步时钟SerCLK。

帧同步模块包括串并转换、帧同步码提取与校验、信号展宽等。

其工作过程如下:首先对发端传送过来的LightSign信号进行串并转换等处理后,由帧码比较器来进行帧码识别。当提取到一个帧码码型 (1001001101011101)信号后,便启动校验电路工作,如果在下一周期的相同时刻又捕捉到一个帧码码型信号,就让系统进入同步工作状态,经过信号展宽处理后,多路开关控制模块开始工作。如果相同时刻没有识别到帧码码型信号,系统仍要处于失步状态,重新开始捕捉。本装置设定n =1,即连续在下一周期的相同时刻,又捕捉到帧码码型信号,则确定此信号是发端传来的帧同步码,让系统进入维持工作状态。当然连续识别次数n可以大于1,这样捕捉更可靠,但捕捉时间就会加长,可以根据实际需要来设定。

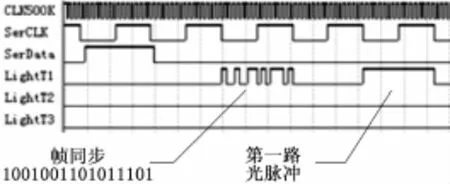

在图6中描述了光幕接收器帧同步码的捕捉时序,图6中的LightSign、CLK500k、CLK31k是输入信号,同步比较信号SyncComp明显较窄,输出的同步数据Ser Data在第一路光脉冲信号之前,输出的同步时钟SerCLK与CLK31k相同。

图6 光幕接收器帧同步码捕捉时序图

图5中多路开关控制模块的作用是产生模拟多路开关的使能信号和各通道选择信号,使模拟多路开关可以采用时分复用方式将16路模拟信号合并成一路模拟信号。多路开关控制模块的输入信号SerData和SerCLK来自帧同步模块,输出信号SwiAEN、SwiA[2..0]、SwiBEN、SwiB[2..0]分别是两片八选一多路开关的使能信号和通道选择信号。

多路开关控制模块的工作过程如下:首先以SerCLK为时钟,SerData为复位信号,设计同步复位型模80计数器,产生计数总线CLKCountD[6..0];接下来判断CLKCountD [6..0]的数值,当CLKCountD[6..0]大于0且小于31时,第一片八选一多路开关的使能信号SwiAEN为0,其余任何计数状态SwiAEN均为1;当CLKCount D[6..0]大于32且小于63时,第二片八选一多路开关的使能信号SwiBEN为0,其余任何计数状态SwiBEN均为1;设计同步触发型电路,在SerCLK下降沿时:

通过上述步骤产生了模拟多路开关所需要的使能信号和通道选择信号。

到位检测模块作用是根据光脉冲信号LightSign、来自帧同步模块的同步数据Ser Data和同步时钟SerCLK,判断运动物体是否出现,输出一个开关量信号Switch Out。

到位检测模块由单束光启停信号生成、单束光判决时钟生成、串并转换、数据累加、计数判断这些部分组成。首先确定每个光脉冲的开始和结束位置,在各个光脉冲中产生多次判决时钟;然后对单个光脉冲进行十二位串并转换,对转换后的并行码进行数据累加、大数判断,可以防止干扰,实现信号滤波;最后对有效光脉冲个数进行计数,若其等于十六,则说明接收光电池收到了十六个光脉冲,光幕发射器、接收器中间没有物体挡住,输出信号Switch Out为高电平,否则为低电平。通过上述这些步骤,实现了物体到位检测功能。

4 FPGA实现与实测波形

本光幕检测装置基于大容量FPGA芯片EP4CE22F17C8N设计,芯片容量约500万门,256管脚,在Quartus集成开发环境中使用VHDL描述[8 10]。

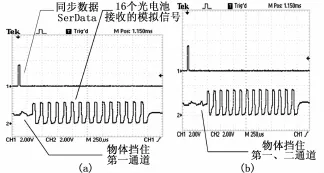

图7 光幕接收器光电池波形图

图7是示波器实际测量得到的光幕接收器部分光电池波形图,图7(a)是物体挡住第一通道的波形,光电池接收到15路有效信号;图7(b)是物体挡住第一、二通道的波形,光电池接收到14路有效信号。示波器第一通道的同步数据Ser-Data是光幕接收器经过锁相环位同步、帧同步后产生的信号,它与光幕发射器信号同步,现场运行稳定。

5 试验结果与分析

本装置收发双方信号的同步是依靠接收端的同步系统从发端送来的信号中,提取出位同步和帧同步信号,从而正确分离出16路光脉冲信号。在光幕运行过程中,系统建立时间是一个重要指标,下面对其进行分析。

位同步是采用快速锁相方式,建立时间很快,因此系统建立时间主要取决于帧同步建立时间。帧同步系统从捕捉到同步需要两个阶段:帧码码型信号识别阶段和校验阶段。

本装置一个周期有16路,即有16个时隙(设路数m=16),当系统在某一时隙捕捉到帧码码型信号后,首先要对系统处理,让刚识别到帧码所在的时隙为第一时隙(TS1);然后进入校验阶段,如果下一周期仍在相同时刻又识别到一个帧码,便让系统进入同步工作状态。

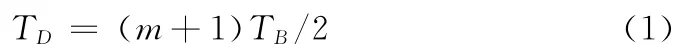

设TB为每个时隙所需时间,由于捕捉时在一个周期m个时隙的任何一个时隙位置上,均可能识别到帧码信号,因此最慢识别到帧码的时间为m TB,最快为TB,计算识别到帧码的平均时间TD:

校验的时间,决定校验次数n,本装置n=1。

设位同步建立时间为TC,计算系统总的建立时间TA:

由式(2)可见,为了缩短建立时间,一般希望校验次数n和路数m小一些,但为了提高光幕的测量精度、测量范围和可靠性,又希望n、m的数值大一些,因此设计光幕检测装置时需要综合考虑上述两方面的因素影响。

6 结束语

采用新提出的同步方法并基于FPGA制备的高速光幕检测装置,在发射器第一路光脉冲之前增加捕捉可靠、抗干扰能力强的帧同步码,光幕接收器使用位同步速度快的快速锁相环算法,16路光脉冲依次串行工作,进而利用FPGA的并行处理特性,有效地实现了高速运动物体的实时到位检测。因此,新实现的高速光幕检测装置具有现场安装方便、数据处理速度快、抗干扰能力强、升级方便等特点,可用于各种工业恶劣环境。

[1]李翰山,雷志勇,袁朝辉.立靶光幕探测性能分析与弹丸信息提取研究[J].计算机测量与控制,2010,18(8):1831-1833.

[2]王瑞峰,杨子河,孔维珍.红外光幕在地铁屏蔽门障碍物探测中的研究[J].传感器与微系统,2013,32(3):25-28.

[3]张少华,李锦明,苏树清.基于FPGA的双光幕测速系统设计与实现 [J].传感器与微系统,2015,34(2):92-94.

[4]徐 薇,杨 卫.一种红外传感器阵列探测方法的研究[J].传感器与微系统,2009,28(9):16-18.

[5]田会,倪晋平.一体化结构四组合光幕阵列测量研究[J].仪器仪表学报,2014,35(2):320-326.

[6]姜 博,梁雁冰.基于FPGA的安全光幕的设计与实现[J].现代电子技术,2010,28(3):137-139.

[7]陈 杰,秦荪榛,徐寅林.光触发同步的安全光幕设计和实现[J].南京师范大学学报(工程技术版),2013,13(2):13-17.

[8]朱玉玉,罗卫军,勾承君.基于FPGA的数字磁通计设计[J].电测与仪表,2015,52(3):107-111.

[9]丁 晟,段雄英,邹积岩.基于FPGA的GOOSE通信系统[J].电测与仪表,2015,52(18):1-4.

[10]邓岳平,肖铁军.基于FPGA的并行DDS信号发生器的设计与实现[J].计算机工程与设计,2011,32(7):2319-2323.

Design and Realization of FPGA Based High Speed Light Curtain Synchronization System

Xu Qiang,Yang Xiaoyun,Zhuang Yanbin

(School of Computer&Information Engineering,Changzhou Institute of Technology,Changzhou 213002,China)

A special synchronized cable is needed to achieve the synchronization of the signals between the emitter and the receiver in conventional light curtain.Aiming at this shortcoming,a new synchronization method is presented for the high speed light curtain,namely that an optical pulse train as the frame synchronization code is added before the first channel emitted optical pulse in each cycle period of the emitter,and the synchronization of the send and receive signals at the receiver is achieved by decoding the frame synchronization code.Therefore,the special synchronized cable is no longer needed and the cost of light curtain synchronization system can be saved effectively.Furthermore,by utilizing newly proposed synchronization method of the high speed light curtain,an overall scheme for the high speed light curtain synchronization system is designed and implemented based on FPGA technique,and thereby a high speed light curtain detector applicable to the real -time position detection of high speed moving object is made in hardware level.The practical engineering application shows that the high speed light curtain detector implementing by this method is low cost,stable and reliable in work,and its capture and synchronization performance is excellent.

light curtain;synchronization system;FPGA

1671-4598(2016)08-0294-04

10.16526/j.cnki.11-4762/tp.2016.08.080

:TM933

:B

2016-03-09;

:2016-03-30。

徐 强(1975-),男,江苏常州人,副教授,硕士,主要从事智能检测技术、嵌入式系统设计方向的研究。

杨晓云(1970-),女,江苏常州人,实验师,主要从事嵌入式系统设计方向的研究。

庄燕滨(1964-),男,教授,硕士生导师,主要从事智能信息处理、视频图像处理、模式识别方向的研究。