无线定位系统中自动增益控制电路的设计与研究

周永强

摘 要: 针对卫星无线定位系统,其民用需求加大,促使商业上对更为廉价、更低功耗的射频收发前端技术进行研究和探索。设计实现了一款用于无线定位系统的数字可编程增益控制系统,可用于IMT?Advanced新一代4G无线通信网络中。对模拟控制和数字可编程两种模式进行了系统上的分析,针对系统建立数学模型,进行了可行性研究。在设计该芯片的同时,对具体模块的不同实现形式进行了阐述,并提出了可优化的结构。

关键词: RFIC; CMOS; PGA; 数字自动增益控制; 带隙基准电压源

中图分类号: TN710?34; TM417 文献标识码: A 文章编号: 1004?373X(2016)23?0157?04

Design and research on automatic gain control circuit in wireless positioning system

ZHOU Yongqiang

(Sichuan Technology and Business University, Chengdu 611745, China)

Abstract: Since the civilian requirement of satellite wireless positioning system is increased, the cheaper and lower?power consumption RF receiving front?end technology is studied and explored for business. A digital programmable gain control system used for wireless positioning system was designed and implemented, which can be applied to the emerging IMT?Advanced new generation 4G wireless communication network. The analog control mode and digital programmable mode are analyzed systematically. The mathematical model of the system was established to study the feasibility. The different realization forms of the speci?fic module are described while designing the chip, and the optimizable structures are proposed.

Keywords: RFIC; CMOS; PGA; digital automatic gain control; bandgap reference voltage source

0 引 言

随着CMOS工艺的发展,数字电路在晶体管栅宽降低中受益最大,能够实现廉价的、大数量和快速的设计和实现。所以射频收发机中,可以考虑采用接收信号强度检测器对接收信号强度进行检测,采用限幅放大器附加全波检流器、低通滤波器实现,能够实现大动态范围内的信号强度检测[1]。通过接收信号强度检测器检测得到的信号传给数字信号处理模块进行分析。根据输入电压值,反馈数字信号给射频端和中频端的放大器模块,从而达到控制增益的目的。随着数字电路处理速度的提高,该模式下能够快速地控制增益,而且不构成模拟反馈环路,系统稳定性也极佳[2]。

本文主要对射频接收机前端中频部分的自动增益控制模块进行研究。通过对该模块国内外已有的研究成果进行总结,分析了多种实现该功能的方法。最后,设计了一种能够集成接收信号强度检测功能的数字可编程增益控制模块。信号强度检测器检测输入信号的电压强度,将得到的参考电压反馈给片外的数字信号处理器,再利用数字信号控制整个放大器的增益。该控制模式下,能够实现大范围的信号强度检测和增益控制。

1 数字可编程自动增益控制系统设计

1.1 闭合环路系统建模

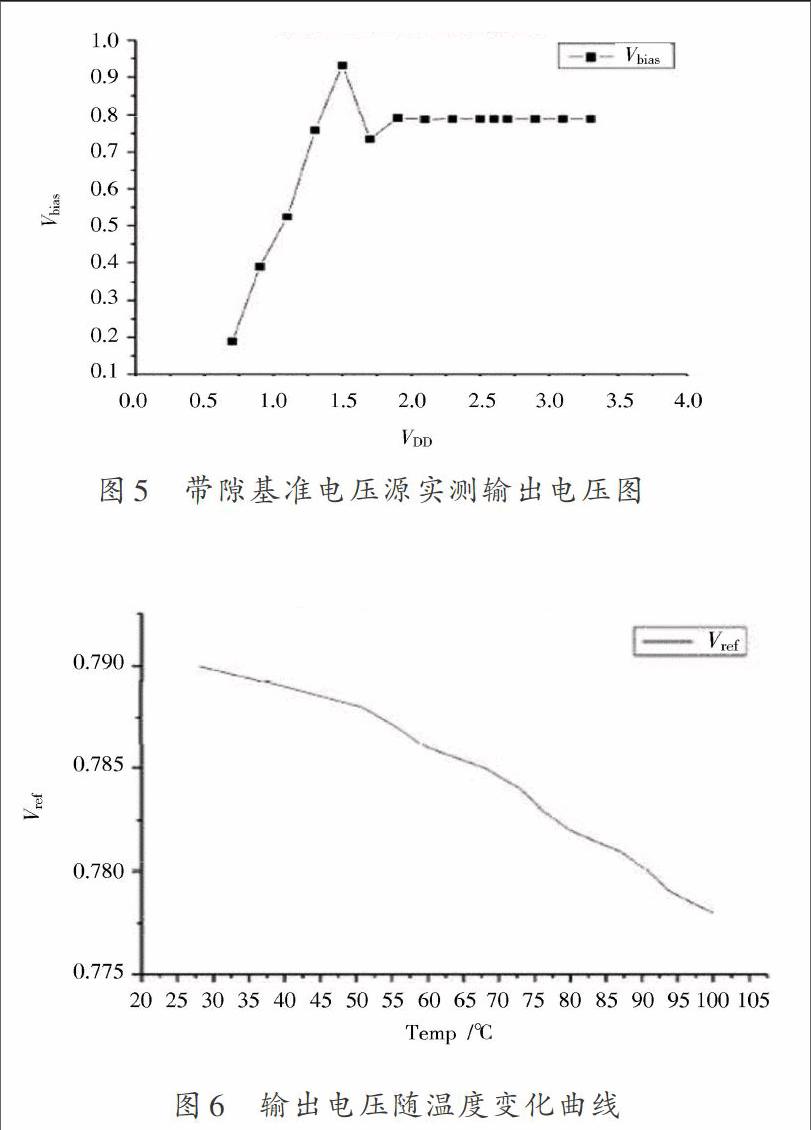

自动增益控制系统可以采用闭环或开环的模式控制。采用闭环模式时,无需额外的控制增益信号,对外围电路的需求少并且精度较好。但是系统的设计中要充分考虑到稳定性的问题,应确保在大增益下不会产生振荡,并且能检测到的最小信号强度有限。与之相对,开环系统能够在提供大增益、大带宽的前提下保证有较好的稳定性。但是,开环系统的增益控制精度往往弱于闭环系统。此次设计中,采用数字增益控制系统为开环增益控制系统。可以考虑内部集成信号强度检测电路和模数转换电路实现内部控制增益。数字自动增益控制系统采用接收信号强度检测器对接收信号进行检测。并将对应的直流信号反馈给片外的数字信号处理芯片进行进一步处理,这是一种开环设计。图1为数字信号处理芯片对接收信号强度检测得到的直流信号进行处理的流程图。

由于RSSI信号随着工艺角和温度的不同有一定的变化。可以考虑在使用前采用数字校准。初始化时,在两个或多个时钟周期内输入最大功率信号-50 dBm和0 dBm,依照下式得到其对应的最大和最小RSSI输出直流电平值。

[Vn=Vmax-(n-1)Vmax-VminNtot-1] (1)

当接收信号输入时,在时钟周期内,可以检测得到直流电平[V。]按照图1所示的逻辑对信号强度进行判断。然后根据初始化时已经储存好的逻辑查表,将控制增益的信号反馈给数字增益放大器,达到增益控制的目的。

如果需要采用内部控制模式实现增益的自动调节,可以考虑下面列举的数模混合电路模式实现。该电路实现了类似于模数转化器的功能。

1.2 放大器设计

在数字控制系统中设计了两种固定增益放大器:一种采用MOS管比值对信号进行放大;另一种采用电阻比值控制放大器增益。

第一种利用NMOS作为跨导将输入电压转换成电流,同时利用二极管连接形式的NMOS管作为负载管提供负载电阻。通过顶端的PMOS电流镜实现跨导管和负载管上分布近似相等的电流。利用长沟道模型可以分析得出:

[Av=gminputgmload=(WL)iIinput(WL)lIinput] (2)

长沟道模型认为晶体管的I?V曲线按照平方率规律,然而在亚微米工艺中,长沟道器件不再表现为理想的平方率器件。如果是理想的平方率器件,对DSI二次求导应该为常数。然而,gm的导数仅仅在一个小的区域内显示为常数。如果变大,gm由常数下降,这是由于高电场引起的,例如迁移率衰减和速度饱和。因此,为获得长沟道模型分析下的性能,深亚微米半导体工艺中需在合适范围内选择正确的过驱动电压。这点对以上这一模块的设计是十分重要的。

第二种设计的固定增益放大器利用电阻比值来获得精确增益。在集成电路设计中,电阻的绝对值在不同工艺下变化较大(误差10%~25%),但是不同电阻间的比值在很好的版图布局下能够做到比较精确(误差<0.1%)。所以能够利用电阻的比值充当增益值。输入端采用源级跟随器的结构,将输入信号引入,加到电阻上。差分信号在电阻转换成电流,起到了跨导的作用。输入端采用Cascode型的PMOS管充当电流源,而输入共源级也采用NMOS管充当供给电流源。电阻需要的电流理论上完全由这两对MOS管提供。当电压转换成电流后,通过电流镜进一步放大,最后在负载电阻上转换成电压的形式输出。理论上,该电路中得到的增益值为:

[Av=KRLOADRgm] (3)

式中:[K]为电流镜提供的增益;[Rgm]为充当跨导的阻抗;[RLOAD]为负载电阻。电路中没有引入共模反馈电路,完全利用两电阻的中点近似的共模电压对电路进行偏置。由于放大器的增益主要和电阻比值、电流镜像有关系,能够实现较好的线性度。前端输入管起到缓冲器的作用。当共模偏置电压有较大变化时,对放大器增益影响也很小。

1.3 数字控制模块设计

可编程增益放大电路系统采用多比特数字信号来控制增益。同时,为了减少对片外电路的影响,可以考虑利用串型信号来控制多比特电路。这需要针对该电路设计相对应的数字电路模块。数字模块采用3线,串联信号控制系统增益的模式。CLK为时钟信号,当其处在上升沿时触发电路;LCH为控制信号,高电平时系统不做出反应,下降为低电平时,随着时钟上升沿跳跃而向电路寄存器中读入SDI/SDO,即串联输入/输出信号。数字模块能够向整个系统中读入增益,同时也能够读出系统目前的增益大小。

增益写入模式中,CLK为时钟信号,LCH为锁存器信号,SDI为输入的控制信号,WR=1指示现在需写入数据,AD1AD2=00为有效地址,后几位为输入的控制字,控制数字模块增益。

增益读取模式中,CLK为时钟信号,LCH为锁存器信号,SDI为输入的控制信号,SDO为输出的控制信号,WR=1指示现在需写入数据,AD1AD2=00时为有效地址,后几位为输入的控制字,控制数字模块增益。利用Verilog HDL编写数字模块程序,分析多个模块实现。digital.v对系统进行总体控制;s2p.v将串联信号转成并联信号;encod.v将得到的并联信号的前三位进行解码,确定读写操作和针对的地址;rpga.v将pga中的数据读出;wpga.v将接收到的数据写入pga。

2 带隙基准电压源设计与实现

2.1 带隙基准电压源原理

带隙基准电压源的设计是利用双极型晶体管基极和发射极电压[VBE]变化具有的负温度系数,以及不同偏置电流下的两个双极型晶体管的电压差具有的正温度系数。两电压线性叠加可获得低温度系数的基准电压源[VBE。]这样就能够提供一个与电源、工艺和温度特性基本无关的直流电压。基准电压的产生中除了要避免电源、工艺和温度的不确定性外,还需要考虑输出的噪声、输出阻抗和功耗。双极型晶体管的输出电流和基级?发射级间电压的指数关系:

[Ic=Isexp(VBEVT)] (4)

通过两个相同偏置电流,并联晶体管数目比值为[1∶n,]的两个双极型晶体管间基极?发射极电势差显示出正的温度特性:

[ΔVBE=VBE1-VBE2=VTlnn] (5)

如果取两个电压之和,就有可能得到一定范围温度内与温度基本无关的基准电压。PMOS管构成电流镜,保证每条支路中的电流一致。高增益的运算放大器保证两个输入端的电压一致。通过推导,可以得到输出参考电压为:

[Vref=R3R1R1VTlnnR2+VBE1≈R3R1×1.12] (6)

在CMOS工艺中,电阻的比值能够做到较为准确。合理的配置电阻阻值的比例和双极型晶体管的面积,可以实现正负温度系数的抵消。在得到基准电压的同时,在每条支路上已经提供了一个与温度无关的电流,不过此时的电流值由于电阻的绝对值在不同工艺下的变化而产生了偏差,电路设计时,需要将该偏差进行充分考虑。再加上R?2R电流分配网络,可以由同一个带隙基准电压源提供不同的数量级,与温度、供给电压基本无关的电流。

2.2 核心模块设计

首先,需要确定两个CMOS工艺上寄生双极性晶体管取值,根据其比值和最终需要的输出电压来确定电阻的取值。

其次,是模块中运算放大器的设计。放大器的性能指标很重要,由于运放在此处为误差放大器,起到负反馈的作用。从精度上考虑,应当采用大增益的运放;但是从稳定性上考虑,应当采用的运放增益需要小。考虑到能采用CMOS 3.3 V的工艺,可以获得足够的电源电压,所以采用折叠型放大器,单级放大,充当带隙基准电压源中的放大器。这样在获得足够增益的同时,也能够得到较好的相位裕度,即系统稳定性较好。

最后,应该对电路设计开启模块。以保证在突然加电时,整个电路能够顺利的开启而不是陷入零状态。电路开启的目的是在电路中引入额外的激励。对开启电路进行分析可以得出,电路需要开启时,M2的栅压为低电位,关闭。M1的栅压为低电位,开启。从而在M3的栅上形成高电位,而电路未开启时,M3的漏端也为高电位,从而M3中流过电流,此电流流入放大器中,通过放大器中的电流镜开启整个电路。

电路开启后,M2上的栅电压拉高,导通。由于M1的宽长远小于M2的宽长比。当电路维持稳定时M2的漏源电压特别小,使得M3截止。而且同时M1和M2组成的支路消耗的电流也特别小。这样就实现了对电路进行开启后对其他核心电路没有影响的目的。

3 仿真和测试结果以及数据分析

此次设计的数字可编程增益控制模块,采用中芯国际0.18 μm混合信号CMOS工艺实现。核心模块的版图面积为170 μm×91.6 μm,含有带隙基准电压源后,面积为223.6 μm×270 μm,最终测试用的芯片面积为1 140 μm×838 μm。由于带隙基准电压源在整个射频接收发端芯片中,为公用模块,无需单独设计。核心模块实际占用芯片面积较小。采用将芯片焊接到PCB版上进行测试。

线性度是系统设计中考虑的另外一个要点,可以通过1 dB交调点和三阶互调节点描述,反映了系统能够承受的、较小失真的最大输入和输出电平。系统线性度仿真如图2所示。

在整个增益控制系统中,除了中频放大模块外,还外加集成了接收信号强度检测模块,其和片外低通滤波器一起,反馈电压信号给数字信号处理器进而对接收到的信号强度进行指示。接收信号强度指示曲线如图3所示,可以看出在较大的范围内(>50 dB),能够线性地对接收到的信号进行检测,满足此次设计的要求。

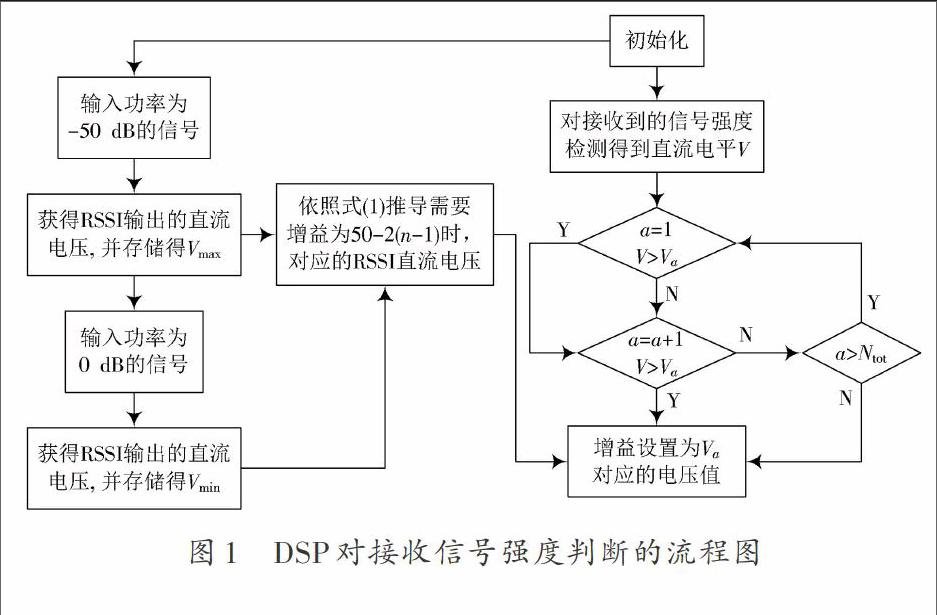

此次带隙基准电压源设计中,采用中芯国际0.18 μm混合信号全CMOS工艺中的3.3 V栅级厚栅晶体管进行设计。对带隙基准电压源进行电路图设计、前仿真、绘制版图进行后期仿真。将该模块集成到整个芯片当中,最后进行了测试。首先对电路进行直流仿真,从0~5 V间变化电源电压。电源电压在2.2~4.8 V间变化时,带隙基准电压源都能够得到较为稳定的输出电压,如图4所示。

为了确保电路能够开启,同时具有较好的稳定性,对其进行瞬态仿真。当加载的电源电压在10 μs处,0.1 μs时间内从0阶跃到3 V。可以看出输出电压能够快速开启,并实现准确的电压输出。对流片后得到的实际芯片进行测试,得到实测结果,如图5所示。发现当电源电压大于1.8 V时,能够提供0.79 V的输出偏压,与理论上仿真的0.801 V较为接近,满足需求。

同时,将芯片放入恒温箱,保持电源电压3 V不变。在变化温度的情况下,对输出电压值进行测量。所得结果如图6所示。可以发现,27~100 ℃之间,电压变化12 mV,与仿真结果相比差距较大。经过分析,认为是由于电路中电阻面积太小,所以精度不够,或者是由于工艺生产中寄生二极管不够准确所导致。

4 结 论

本文通过对CMOS工艺自动增益控制系统进行设计,归纳总结了相关的国内外在该领域上的进展和设计此系统的方法,并提出了自己的见解。从研究自动增益控制系统的拓扑结构入手,理论上分析并提出了设计中的数学模型。在通过可行性研究的基础上,对该系统进行设计。采用数字增益控制系统,并且集成了接收信号强度检测模块和带隙基准电压源偏置模块,获得了高度的集成性。

在具体模块设计上,对多种结构进行分析,提出针对不同应用领域,考虑到具体指标的折中,进行了针对性的设计。在构建电路模型、仿真的基础上,进行了版图绘制、仿真、流片,并且对其中的带隙基准电压源模块进行了实际测试,得到的结果基本和仿真结果吻合。

参考文献

[1] 吕伟,朱建军.北斗卫星导航系统发展综述[J].地矿测绘,2007,23(3):29?32.

[2] 柳良,陈泾浦.数字自动增益控制和模数转换数值抖动研究[J].现代电子技术,2013,36(15):119?122.

[3] KADOYAMA T, SUZUKI N, SASHO N, et al. A complete single?chip GPS receiver with 1.6?V 24?mW radio in 0.18 μm CMOS [J]. IEEE journal of solid?state circuits, 2003, 103(4): 135?138.

[4] DUONG Q H, LE Q, KIM C W, et al. A 95?dB linear low?power variable gain amplifier [J]. IEEE transactions on circuits and systems I, 2006, 53(8): 1648?1657.

[5] KIM T W, KIM B. A 78?dB gain range low power CMOS RF digitally programmable gain amplifier for mobile terrestrial D?TV tuner IC [J]. IEEE microwave and wireless components letters, 2006, 16(4): 185?187.

[6] KIM T W, KIM B. A 13?dB IIP3 improved low?power CMOS RF programmable gain amplifier using differential circuit transconductance linearization for various terrestrial mobile D?TV applications [J]. IEEE journal of solid?state circuits, 2006, 41(4): 945?953.

[7] TSOU S C. A low?power CMOS linear in decibel variable gain amplifier with programmable bandwidth and stable group delay [J]. IEEE transactions on circuits and systems, 2006, 53(12): 1436?1440.

[8] CEEKALA V G, LEWICKI L D, WIESER J B, et al. A method for reducing the effects of random mismatches in CMOS bandgap references [C]// Proceedings of 2002 IEEE International Solid?State Circuits Conference. San Francisco: IEEE, 2002: 392?393.