基于分布式算法的多项抽取滤波器设计

石立国++侯鸿杰++王竹刚++熊蔚明

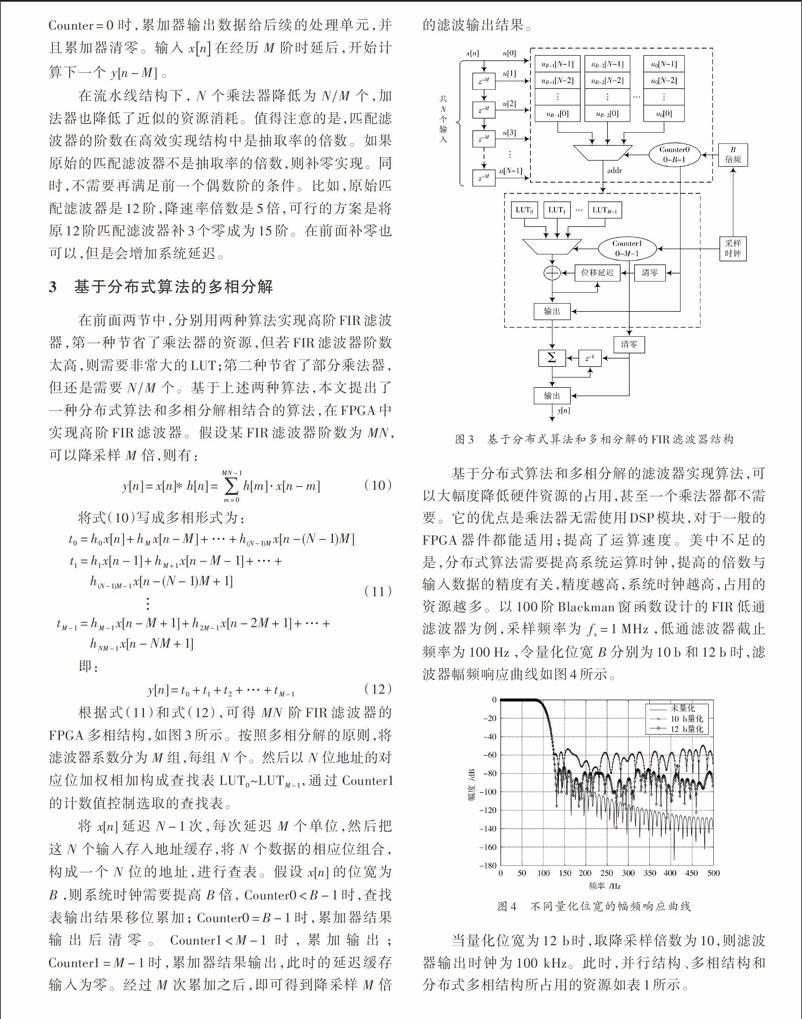

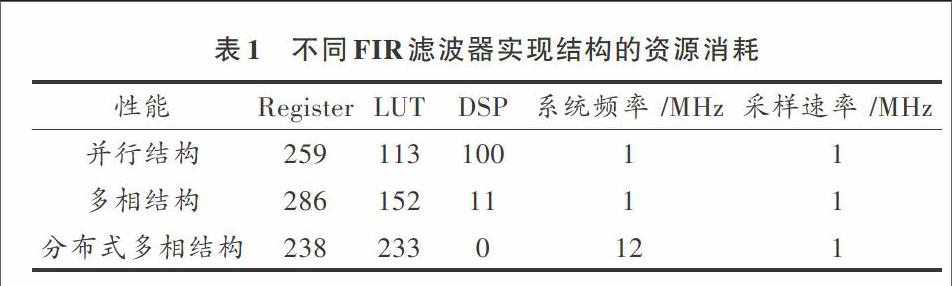

摘 要: 实现高阶FIR滤波器时,在降低FPGA硬件资源占用方面,分布式算法和多相分解技术应用广泛。详细介绍了分布式算法和多相分解技术的原理,并结合FPGA的特点提出了适用于高阶FIR滤波器的新算法,解决了分布式算法实现高阶FIR滤波器查找表过大的问题,提高了硬件资源的利用率。推导了基于分布式算法和多相分解技术的实现原理,通过ISE实现并验证了该算法的高效性。最后,给出了滤波器性能随滤波器系数量化位宽变化的关系。

关键词: FIR滤波器; FPGA; 分布式算法; 多相分解

中图分类号: TN713+.7?34 文献标识码: A 文章编号: 1004?373X(2016)23?0068?04

Design of polyphase decimation filter based on distributed algorithm

SHI Liguo1, 2, HOU Hongjie1, 2, WANG Zhugang1, XIONG Weiming1

(1. National Space Science Center, Chinese Academy of Sciences, Beijing 100190, China; 2. University of Chinese Academy of Sciences, Beijing 100190, China)

Abstract: The distributed algorithm and polyphase decomposition technology are widely used to implement the high?order FIR filter and reduce the occupancy of FPGA hardware resource. The principles of the distributed algorithm and polyphase decomposition technology are introduced in detail. In combination with the characteristics of FPGA, a new algorithm suitable for high?order FIR filter is proposed, which can solve the problem that the distributed algorithm is adopted to realize the oversize high?order FIR filter lookup table, and improve the utilization of hardware resource. The implementation principles based on the distributed algorithm and polyphase decomposition technology are deduced. The high efficiency of this algorithm was realized and verified by ISE. The relationship of variation of the filter performance with the width of the filter coefficient quantization bit is given.

0 引 言

从20世纪末期开始,小卫星以编队飞行的方式完成复杂的空间探测任务成为了热点。小卫星具有重量轻、体积小、功耗低、成本低、研制周期短等优点[1],但也有相应的不足之处,例如受重量、体积、功耗的限制,其性能也大大降低。星载的数字信号处理IC也只能应用低功耗的系列,例如Xilinx公司的Spartan 6,其片上资源尤其是DSP资源非常有限。因此,在片上数字信号处理的算法中,要尽量减少硬件电路规模,节省FPGA硬件资源,以达到低功耗的要求。

FIR数字匹配滤波器在信号解调、信号检测和时延估计中有着优异的性能,并得到了广泛的应用[2]。但随着阶数的提高,FIR数字滤波器占用的资源越来越多[3]。由于大量的乘法存在,在低功耗FPGA中实现高阶FIR数字滤波器十分困难,为解决这一问题,通常的实现方式有两种:一是采用多相分解的方式“降低”滤波器的阶数[4?5];二是采用分布式算法实现乘法操作[6?7]。本文提出了数字滤波器的多相实现结构与分布式算法相结合的方法,在实现具有相同阶数的FIR数字滤波器时,尽可能地减少硬件资源的占用。

1 分布式算法

分布式算法[7](Distributed Arithmetic,DA)于1973年由Croisier提出,是一种专门针对乘加运算的重要的FPGA技术,而FIR滤波器是一个标准的乘加运算。采用分布式算法实现FIR滤波器可以显著地减小硬件电路规模,十分方便的实现流水线处理,提高电路的运算速度。分布式算法在完成乘加运算功能时,将所有输入数据的每一对应位进行滤波器系数的预先累加形成的部分积利用LUT存储起来,然后对每一个部分积进行移位累加,从而得到最终乘加结果。

假设某[N]阶FIR滤波器的表达式为:

4 结 语

本文利用FIR滤波器的分布式算法和多相分解技术提出了一种高效的高阶FIR滤波器FPGA实现结构。采用这一算法设计的滤波器可以节省大量FPGA硬件资源,并解决了高阶FIR滤波器分布式算法实现时查找表过大的问题。给出了并行结构、多相结构和基于分布式算法的多相结构的资源占用对比,通过Xilinx SP605开发板验证了这一算法的可行性和高效性。基于分布式算法的多相结构实现的FIR滤波器带外抑制性能与滤波器系数量化位宽成正比,当滤波器系数量化位宽为10 b时,带外抑制大于50 dB;量化位宽为12 b时,带外抑制大于70 dB。

参考文献

[1] 吴国强,孙兆伟,赵丹,等.编队小卫星星间通信系统的发展和趋势[J].哈尔滨工业大学学报,2008,39(11):1699?1703.

[2] 刘凌.数字信号处理的FPGA实现[M].北京:清华大学出版社,2006.

[3] 魏灵,杨日杰,崔旭涛.基于分布式算法的数字滤波器设计[J].仪器仪表学报,2008,29(10):2100?2104.

[4] 段国栋,蒋小平,马速良,等.一种基于多相结构的高效数字下变频设计[J].电子技术应用,2014,40(4):52?55.

[5] FIALA P, LINHART R. High performance polyphase FIR filter structures in VHDL language for software defined radio based on FPGA [C]// Proceedings of 2014 IEEE International Conference on Applied Electronics. Plzen: IEEE, 2014: 83?86.

[6] MOHANTY B K, MEHER P K. A high?performance energy?efficient architecture for FIR adaptive filter based on new distri?buted arithmetic formulation of block LMS algorithm [J]. IEEE transactions on signal processing, 2013, 61(4): 921?932.

[7] HWANG S, HAN G, KANG S, et al. New distributed arithmetic algorithm for low?power FIR filter implementation [J]. IEEE signal processing letters, 2004, 11(5): 463?466.

[8] 谢海霞,孙志雄.多相抽取滤波器的FPGA实现[J].电子器件,2012,35(3):331?333.

[9] JOHANSSON H, HARRIS F. Polyphase decomposition of digital fractional?delay filters [J]. IEEE signal processing letters, 2015, 22(8): 1021?1025.

Keywords: FIR filter; FPGA; distributed algorithm; polyphase decomposition