基于FPGA/SOPC—Nios Ⅱ的人体脉搏信号的测量

蒲瑞瑞

摘要:介绍基于FPGA/SOPC嵌入技术并利用压电传感器实时采集脉搏波信号进行处理的方案,阐述了系统的设计原理。系统由脉搏采集调理电路、SOPC嵌入式数据处理、上位机界面三大部分组成,其中在SOPC数据处理部分嵌入32位Nios Ⅱ软核处理器,用于控制脉搏信号采集、处理,与上位机通讯、接受测量命令、传送结果到上位机等功能。基于FPGA/SOPC-Nios Ⅱ的人体脉搏信号的测量系统,将所有的接口电路集成在一片FPGA上,提高了系统可靠性和稳定性,系统易于升级和功能扩展,具有较高的性价比。

关键词:FPGA/SOPC;脉搏信号;调理电路;Nios Ⅱ

引言

脉搏即动脉搏动,随着心脏节律性的收缩和舒张,动脉管壁相应的出现扩张和回缩,在表浅动脉上可触到搏动,是人的四大体征之一。临床上有很多疾病,如心脏病、心血管疾病可使得脉搏与正常值不一致,所以对病人而言脉搏测量是检查身体健康状况的不可缺少的一项。

现有的脉搏测量仪器大多是以单片机、ARM、DSP為主来设计的,这三种方案在可靠性、灵活性、扩展性等方面的都存在不足之处。为此设计了一款基于FPGA嵌入式IP软核的SOPC系统,来实时测量人体脉搏,该系统解决了将IP硬核直接植入FPGA的方案时无法自由裁剪处理器而导致系统价格过高的不足,在SOPCBuilder和OuartusⅡ上根据实际需求配置Nios Ⅱ软核及外设,从而使得系统在功能特点、硬件结构、价格等方面得到平衡。

该文主要完成脉搏信号的采集调理、信号处理、Nios Ⅱ软核的搭建。

1.设计原理

用户在上位机对SOPC嵌入式系统发送测量命令,使得脉搏传感器采集人体脉搏信号,脉搏信号由于其低频强噪的特性,因此需要通过调理电路来对采集到的信号进行去燥、滤波、放大等模拟信号处理,以便得到一个有用的脉搏信号。同时,SOPC接收来自上位机的控制命令,启动A/D转换器对脉搏信号进模数转换,转换完的数字量送到SOPC内部做相应的数值分析处理,并将结果送到上位机上显示,同时存储测量结果。

2.系统的硬件设计

系统的硬件设计主要完成的是信号的采集模拟处理:对采集到的微弱的脉搏信号进行放大和滤波,滤除各种噪音信号干扰。

脉搏采集选用SC0073压电式脉搏传感器,由于脉搏信号为超低频信号,极易引入工频干扰,而且SC0073输出信号十分微弱,一般情况下只有20mv左右,需要采用调理电路对脉搏信号进行初级放大、带通滤波、次级放大,该处选用AD620和LM358作为核心元件,目的是滤除50HZ的工频干扰以及得到满足A/D转换的输入电压,硬件电路如图2所示。

3.SOPC平台的构建

系统使用DE2开发板,其核心芯片是EP2C35F672C6,提供50MHZ和27MHZ的时钟源。AD转换器采用MAX197,该芯片是多量程、8通道、12位高精度的A/D转换器,转换时间为6us,从精度、分辨率、采样率来看均符合设计需求。

图3是系统的平台设计框图,其中PLL模块利用锁相环产生SDRAM、MAX197、脉搏计数模块等模块的时钟信号。MAX197模块控制AD转换器对模拟脉搏信号进行数字量的采集。经过AD转换后脉搏数字量,通过阈值比较器得到与脉搏同周期的方波,脉搏计数模块统计60s内方波数,就可得到脉搏值。

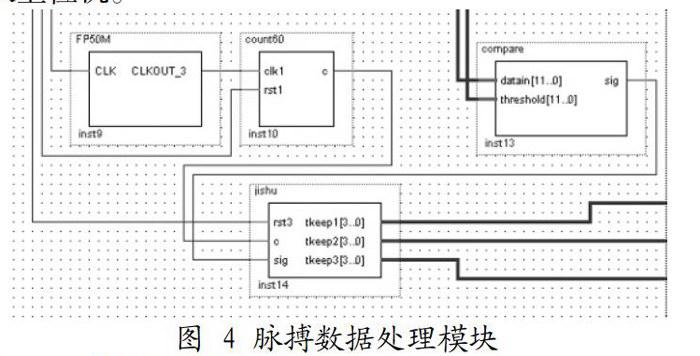

3.1脉搏测量模块

图4是利用VHDL编写的脉搏数据处理模块,其中FP50M模块和count60模块的功能是完成60s的定时器,datain[11..0]是从AD芯片输出的脉搏信号的数字量,threshold是比较器的阈值,sig是经过比较器的与脉搏波同周期的方波信号,最后对方波的计数由jishu模块完成,其中tkeepl[3..0]、tkeep2[3..0]、tkeep3[3..0]分别是计数器的个位、十位、百位,将脉搏值送入NiosⅡ处理器中进行存储和组帧送入上位机。

3.2 Nios Ⅱ软核的定制

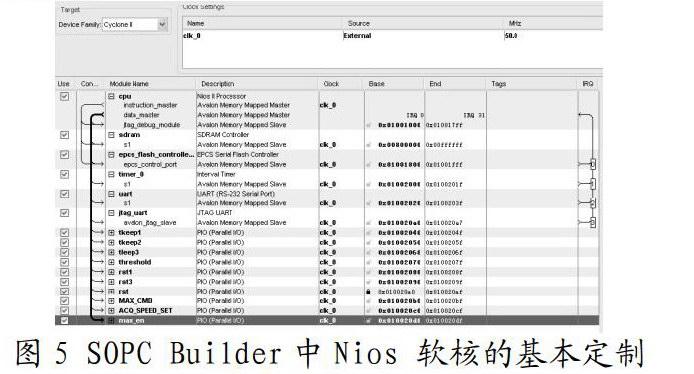

SOPC Builder是SOPC系统的开发包,用于配置Nios Ⅱ、外设、存储,生成与SOPC系统相关的监控和软件调试平台。

NiosⅡ处理器是整个系统的核心,可根据系统的实际需求,从SOPC Builder组件库中选择IP模块、存储器、CPU、外围接口,配置生成一个高度集成的SOPC嵌入式系统。系统的定制的SOPC系统如图5所示,包括NiosⅡCPU、UART接口、SDRAM接口、EPCS接口、JTAG UART接口、定时器以及一些自定义PIO接口,在添加这些内核的过程中可以根据系统要求配置芯片,把与系统不相关的硬件不集成到系统里,这样就可以减少SOPC系统的硬件资源,并降低系统功耗。

从图5可见NiosⅡ配置如下:

NiosⅡCPU:软核有3种类型,为了调试方便,本系统采用NiosⅡ/f型。UART接口用于接收,发送串行数据。SDRAM组件用来存储容易丢失的数据、文件,配置为为数据位16位,4个BANK,12位行地址,8位列地址。EPCS器件可用来存储程序代码以及管理FPGA的配置数据,并在上电时自动完成对FPGA的配置。JTAGUART组件为CPU的调试模块,在Nios IDE中进行软件调试时需此组件才可以进行在系统调试。其余定义的PIO组件包括,脉搏数据输出接口、控制AD转换的端口等。

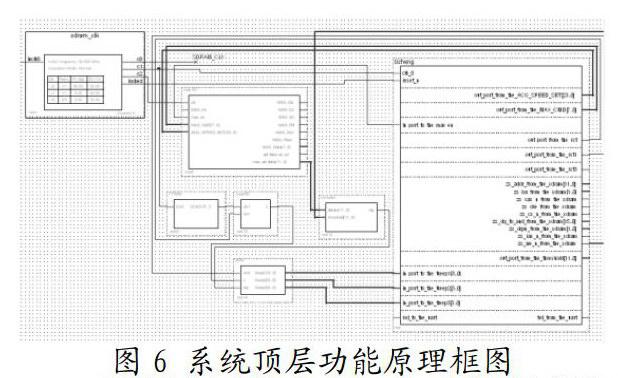

3.3系统功能原理框图

在SOPC系统定制生成后,就要在Quartus Ⅱ中将PLL时钟模块、用户自定义的脉搏测量模块、Nios Ⅱ系统模块进行布局布线集成系统功能原理图,如下图6所示。

在Ouartus Ⅱ工程的顶层实体中对SOPC系统进行管脚分配、时序约束,全编泽后通过JTAG接口将生成的.sof文件下载到FPGA开发板上。

4.结束语

该人体脉搏测量系统是利用VHDL编程,基于DE2开发的,可以方便实时测量人体脉搏,具有功能强、测量准确、测量范围宽,性价比高等特点,方便家庭及个人测量使用。同时利用FPGA/SOPC开发周期短、定制性高、扩展性好的特点,可以不断升级测量仪来延长产品的生命周期,并可以在使用过程中随时添加更多的功能,具有良好的应用前景。