一种P/L频段高度综合化航空平台的设计*

王世涛,李明兵

(1.海军装备部驻重庆地区军事代表局,成都610036;2.中国西南电子技术研究所,成都610036)

一种P/L频段高度综合化航空平台的设计*

王世涛1,李明兵**2

(1.海军装备部驻重庆地区军事代表局,成都610036;2.中国西南电子技术研究所,成都610036)

为进一步提升航空平台综合化程度,设计了一种用于航空平台的P/L频段功能高度综合化硬件平台方案。该方案通过射频直接采集2 GHz以下的低频射频信号,在数字域分离出探测、通信、导航、识别以及无源侦察等功能所需基带I/Q信号,最后通过软件完成各种信号的功能处理,实现了对探测、通信、导航、识别以及无源侦察等功能共信道和共信号预处理的高度综合设计。硬件实现验证了该方案能够有效降低硬件系统设计的成本和复杂性,降低系统功耗,有力推进了软件无线电在航空平台综合化中的应用。

P/L频段综合化航空电子;射频采样;软件无线电硬件平台;高效预处理算法

1 引 言

从战斗机的航空电子发展过程来看,综合航空电子技术发展至今近半个世纪,基本上经历了分散、联合、综合到高度综合这四个阶段[1],综合化已成为提升航空电子系统性能的主要途径之一。

1998~2012年,美国空军实验室联合波音公司和洛马公司就机载综合传感器系统的研究阐述了数字技术对射频综合基础架构的巨大影响[2],随着ADC的采样速率的提高,整个射频架构变得更加简洁,同时航空平台综合程度也越高。

近年来,俄罗斯亦进行了L频段机载多功能综合化设计[3]。采用高度综合化硬件架构取代目前机载平台上众多独立的天线孔径及射频前端,将综合推进到天线、射频前端及处理器,是未来机载传感器系统的发展趋势。

软件无线电的思想是将ADC尽量靠近天线[4],系统功能尽量通过软件来实现。基于这种思想的硬件平台,通过宽开天线、宽开接收机、高速 ADC/ DAC,同时将多信号在后端信号处理机进行统一处理,分离出各功能所需信号,实现多功能同时工作,极大简化硬件平台。

目前,国内外对P/L频段射频信号直接射频采样的综合化硬件平台研究很少。文献[5-6]对高速数据采集接口进行了研究,然而并未开展综合化硬件平台研究。截至目前,尚未见国外采样速率高达Gsample/s以上的综合化平台报道文献。

本文设计一套高度综合化处理硬件平台,通过高达5 GHz的高速ADC直接采样2 GHz以下射频信号,并采用高效的预处理方法,在数字端进行正交解调,既保证了正交解调的幅相一致性,又同时分离出探测、通信、导航、识别以及无源侦察等传感器所需基带信号,对新一代航空平台综合化具有重要的借鉴意义。

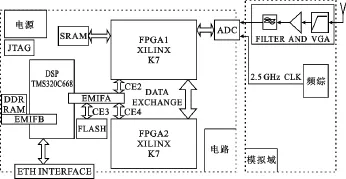

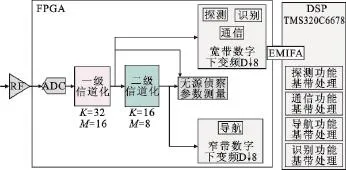

2 硬件平台设计

本系统的工作原理是,使用宽频天线接收0.5~2 GHz全频段射频信号,在射频前端直接对信号进行限幅、放大、滤波,然后高速ADC直接对前端输出射频信号进行射频采样,其后通过FPGA进行数字下变频等处理,提取出基带信号,最后将基带数据通过EMIF总线交给DSP进行后续处理。系统原理如图1所示。

图1 硬件平台框图Fig.1 The diagram of hardware platform

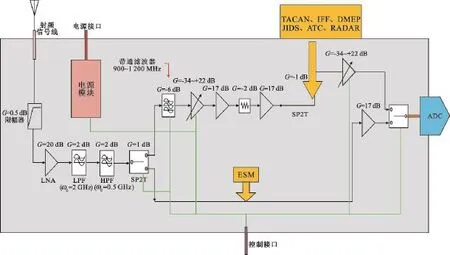

2.1 射频前端设计

直接采样射频前端主要采用放大器和滤波器,其在射频前端不需要混频、滤波,相比传统超外差接收机射频前端电路结构非常简单。

目前2 GHz以下低频段覆盖探测、通信、导航、识别以及无源侦察等功能,不同功能的信号带宽以及接收机都不相同。2 GHz以下探测、通信、导航、识别等功能频段主要集中在L频段[7],同时其灵敏度要求优于-90 dBm以上,而无源侦察功能需要覆盖0.5~2 GHz,同时其灵敏度只要求优于-60 dBm,因此,射频前端需要分两路分别进行设计,以满足不同功能对灵敏度的需求。

如图2所示,宽频天线接收后的射频信号经过限幅器以及低噪声放大后,通过一个低通和高通组合成的带通滤波器,然后将射频信号分为2路,一路为无源侦察功能接收通路,另外一路经过一个带通滤波器作为探测、通信、导航、识别等功能接收通路。

图2 射频前端设计Fig.2 The design of RF frontend

此外,电磁兼容设计也是射频前端的一个重要方面。射频前端电磁污染主要来自于系统内部的高频电路、数字控制电路和瞬变电路的电磁辐射,这些干扰源可以通过许多不同途径进入到受害敏感源,这些途径主要包括导线与导线之间的耦合、电磁场对导线的耦合等。

射频前端设计时主要采用独立屏蔽腔体,将电磁兼容滤波器、连接器与其他电路隔离开来,电源输入经过电磁干扰滤波后,再经过线性稳压,输出到相应的电路中。

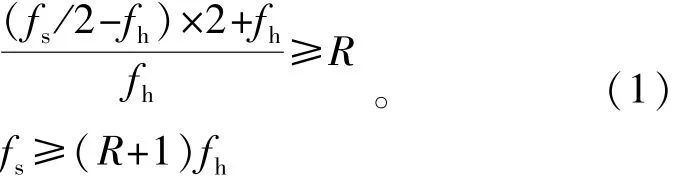

2.2 采样率的设计

探测、通信、导航、识别等频段主要集中900~1 200 MHz频段,根据低通采样定理只需2.4 GHz采样速率的ADC就可以解调出信号信息,工程上为保证上述功能解调质量,一般需要按最高频率的4倍进行采样,因此采样速率需满足4.8 GHz以上。

无源侦察功能需要侦察0.5~2 GHz射频信号。由于无源侦察只需测量脉宽、到达时间、功率等参数,工程按采样速率最高频率的2.5倍以上就可以测量出上述参数,因此,采样速率优于5 GHz即可。

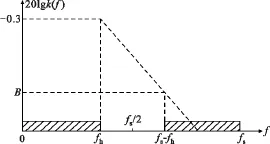

如3所示,对采样频率fs进行选择时,除考虑满足功能要求外,还需要考虑抗混迭滤波器的可实现性。采样速率与滤波器通带截止频率以及低通滤波器矩形系数R关系为[8]

式中:fh为信号截至频率;R为滤波器矩形系数。

图3 低通抗混叠滤波示意图Fig.3 The diagram of low pass anti-aliasing filter

根据低通滤波器矩形系数R和阶数之间的关系,R为1.5时,抗混叠滤波器阶数较低,在fh取2 GHz时,采样速率选择5 GHz较为合适。

经过市场调研,ADC选用 E2V公司的EV10AQ190高速数模转换器。EV10AQ190为10位高速ADC器件,最高支持大于5 Gsample/s的高速采样率,同时它提供40对差分接口,能在芯片内部复用为10 b,可满足直接射频采样0.5~2 GHz的要求。为了便于系统后期升级,研发了基于标准FMC子卡的5 GHz采样子卡。

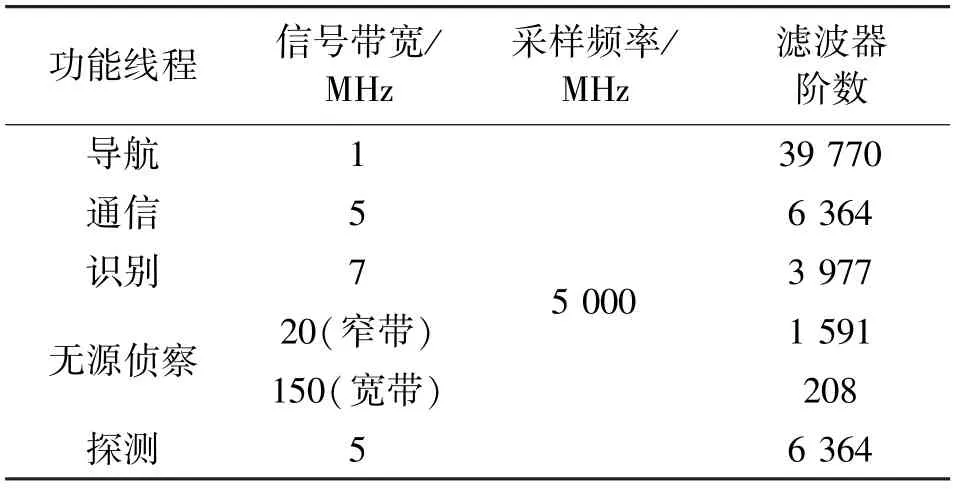

2.3 信号处理平台设计

综合化信号处理平台由大规模可编程门阵列(FPGA)和通过高速串行接口互联的高速ADC组成,ADC直接射频采样所需信号。在FPGA内采用多级信道化、数字下变频等预处理方法,在数字域分离出TACAN、DMEP、ESM等功能所需基带IQ信号,然后将这些基带 IQ信号送至 TI高性能 DSP TMS320C6678上处理完成基带信号处理功能。

数字处理部分的组成器件主要由FPGA、ADC、DSP、FLASH、PROM等组成。FLASH作为外围存储器件,用于大量数据的存储。可编程存储器(PROM)用于程序存储和加载。本地端连接在FPGA上的设备周边组件接口桥(ETH),用于监控计算机的参数设置。

FPGA选用Xilinx公司的大规模可编程门阵列XC7K480T-1FFG676I,可满足该系统多种功能模块和复杂并行算法的设计需要,实际算法占用硬件资源量40%。FPGA外部还提供大容量SRAM,用于存储ADC采集数据和中间结果,最大支持1 Gb数据容量。

设备采用可插入CPCI机箱的CPCI板卡形式,并选用TI公司的TMS320C6678芯片,使用6678集成的PCI模块与PC完成指令和功能结果的交换,同时6678也是基带数据处理以及系统控制和管理中心。FPGA内利用BLOCK RAM资源,将数据暂存在存储区,DSP从存储区取数,得到所需基带数据,然后根据功能需求,加载不同的基带处理软件进行处理。

频综模块的时钟流程如下:外供2.5 GHz高频时钟信号,经高速ADC,送到FPGA,FPGA内部锁相环PLL锁定时钟信号625 MHz作为接口时钟,分频时钟156.25 MHz为内部主逻辑工作时钟。对于625 MHz输入时钟,FPGA若直接分频使用,信号质量不佳,本方案中采用FPGA的模拟锁相环PLL硬核资源提高625 MHz输入时钟的精度,再对其分频使用,大大改善了分频时钟质量,能有效锁定ADC输出信号。

由于ADC输出速率高达1.25 Gb/s,而FPGA的普通IO口不能输入高于450 Mb/s频率的数据[7],因此,必须使用 FPGA的高速 IO口。FPGA有RocketIO GTX 高速接口,可输出100 Mb/s~3.2 Gb/s的数据,但GTX收发器数量有限,Xilinx K7 FPGA提供的GTX最多也不超过32个,而ADC需要的差分接口至少有40对,故本方案采用Xilinx提供的高速串行接口模块(ISERDES),它可以配置在任意一对差分接口上,最多可达400对,速率可达到3.2 Gb/s。

由于ADC硬件设计和FPGA接口的差异,数据很难同时到达FPGA内部,因此,必须先通过FPGA内部IODELAY模块进行数据时延调整,将ADC采样数据调节到FPGA时钟眼图中间,再通过ISERDES进行串并转换,FPGA才能正确得到采样数据。IODELAY模块数据对齐调节原理如图4所示。

图4 IODELAY调节原理Fig.4 The principle of IODELAY adjustment

3 综合化信号预处理算法设计

经过高速ADC接口后,需要进一步将射频的数字信号转为基带I/Q信号。

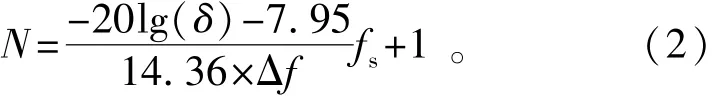

采用窗函数方法设计滤波器所需的低通滤波器阶数N为[9]

式中:δ为阻带衰减;Δf为过渡带带宽。

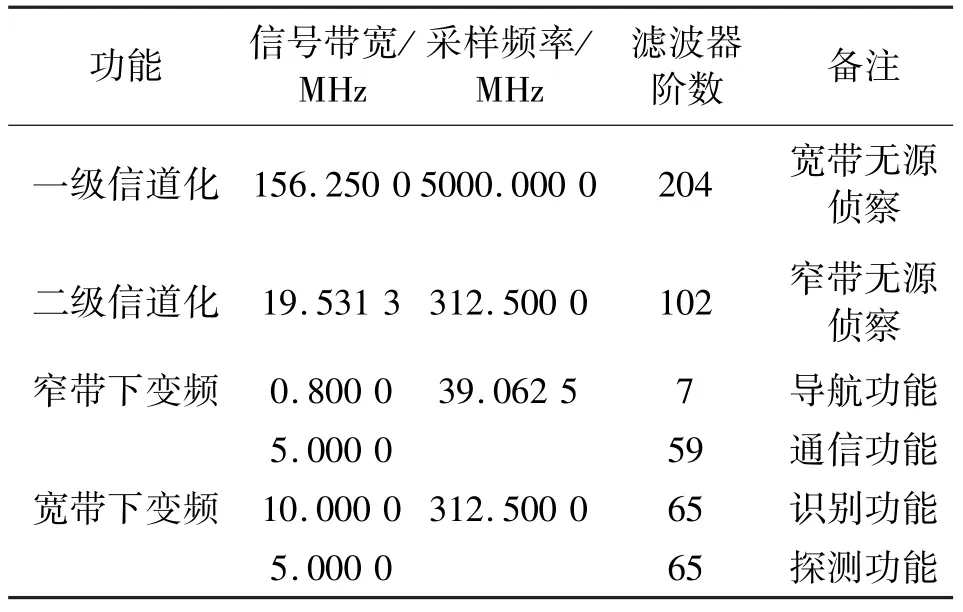

若按传统方式进行预处理,则所需资源如表1所示。

表1 传统接收机所需资源Tab.1 The required resources of traditional receiver

传统方式进行预处理所需滤波器阶数远远超过目前硬件所能承受水平。为解决此问题,本文提出了一种更高效的综合预处理算法,充分考虑每个功能的信号带宽、每级信道化后的采样速率、滤波器资源需求等,采用多级信道化加数字下变频的方式,同时进行探测、通信、导航、识别以及无源侦察等功能基带信号提取,其原理框如图5所示。

图5 高效预处理综合化接收机算法原理Fig.5 Algorithm principle of the high efficient integrated receiver

首先,采用数字信道化技术[10],将采样频率为5 GHz的数字信号分为K(32)路数据,每路数据抽取M(16)倍,构成一级信道化,每个子信道带宽为156.25 MHz,采样速率为312.5 MHz。然后,将一级信道化数据分3路:第一路直接进行无源侦察宽带信号的参数测量;第二路进一步做信道化以及导航功能下变频;第三路用于探测、通信、识别等功能下变频,用于提取出基带信号。

由于数字信道化接收机每个子信道的下变频中心为Fs/K×k(k为子信道号),而探测功能频率在L频段任意分布,因此,还需进一步进行数字下变频,将信道化后的探测、通信、识别等功能信号转为基带信号。导航功能信号带宽只有1 MHz左右,一级信道化后的采样速率远超过此信号带宽,为降低资源需求,一级信道化后的数据只用于探测、通信、识别功能的数字下变频处理。

对于无源侦察的窄带信号的侦收,需在一级信道化基础上,进一步划分信道,用于提高无源侦察接收机的灵敏度,经过二级信道化,将采样频率为312.5 MHz的数字信号分为K(16)路数据,每路数据抽取M(8)倍,每个子信道带宽为19.531 3 MHz,采样速率为39.062 5 MHz,然后数据分2路:第一路直接进行电子战窄带侦收的参数测量;第二路用于导航功能下变频,用于提取出基带信号。

采用高效综合化预处理方式所需资源如表2所示,与表1传统典型并行多通道无线电接收机所需资源对比可知,本文所提算法所需资源大大降低,非常有利于硬件实现。

表2 高效综合化结构所需资源Tab.2 The required resources of effective integrated structure

4 实验验证

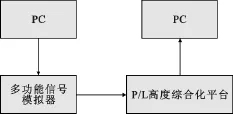

为了验证硬件平台综合化设计,采用如6所示的方式进行性能测试。P/L频段高度综合化平台一端直接与多功能信号模拟器连接,另一端通过以太网与PC电脑对接。ADC直接对雷达(探测功能)、塔康(导航功能)等射频信号进行采集。将ADC采样数据接收并存储下来,然后通过以太网将数据读取出来。

图6 硬件平台测试示意图Fig.6 Hardware platform test schematic diagram

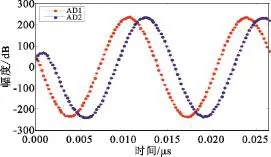

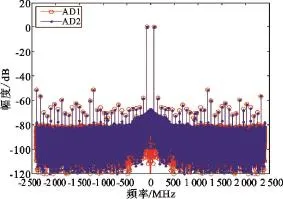

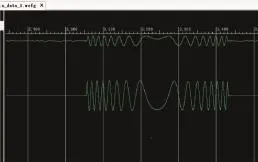

图7给出了ADC采样的时域波形,可以看出,连续两次采样的信号都比较平滑。由图8的频谱可以看出,无杂散动态范围达到50 dBc,从而验证了ADC采样数据的正确性。

图7 ADC采样数据Fig.7 ADC sampling data

图8 ADC采样数据的频谱显示Fig.8 The frequency spectrum of the ADC data

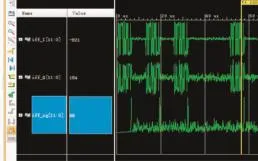

图9为雷达信号数字下变频后时域波形,图10为雷达脉压结果。

图9 雷达数字下变频后时域波形Fig.9 Time domain waveform of radar after DDC

图10 雷达匹配滤波后波形Fig.10 Radar waveform after the matched filtering

图11为塔康信号数字下变频后时域波形。

图11 塔康数字下变频后时域波形Fig.11 The time domain waveform of TACAN after DDC

图12为敌我识别信号数字下变频后时域波形以及相关匹配后波形,可以明显看出信号相关峰。

图12 敌我识别数字下变频后时域波形以及相关匹配后波形Fig.12 The time domain waveform of IFF after DDC

综上实验结果,说明本文设计硬件平台能够满足各种功能信号处理实现的要求。

5 结束语

本文从国内外机载综合传感器系统研究现状及应用情况出发,初步构建了一种适用于航空平台的P/L频段多功能一体化硬件平台,并进行了实验验证。采用高速射频直接采样,实现了对探测、通信、导航、识别及无源侦察等功能的共信道、共信号预处理的高度综合化设计。同时,针对传统典型并行多通道无线电接收机所需资源多,提出了多级信道化加数字下变频的高效的综合预处理算法,并给出了硬件资源的详细对比,表明该方案所需硬件资源显著减小,简化了设计复杂性及成本,具备较好的通用性,对新一代航空平台综合化设计具有一定参考价值。

在实际应用中,复杂电磁环境下的强干扰可能导致ADC饱和、系统性能下降,如何提高该硬件平台在复杂电磁环境的稳定性和适应性将是下一步的研究方向。

[1] 梁德文.战斗机航空电子系统最新的发展趋势——网络化[J].电讯技术,2008,48(6):93-97. LIANG Dewen.Review on the new development of fighter avionics system——networking[J].Telecommunication Engineering,2008,48(6):93-97.(in Chinese)

[2] 陈颖,陈德志.航空传感器综合处理机的开放式体系架构[J].电讯技术,2005,45(2):107-110. CHEN Ying,CHEN Dezhi.Open systems architecture of airborne integrated processor[J].Telecommunication Engineering,2005,45(2):107-110.(in Chinese)

[3] 高飞.俄第五代战斗机的前缘襟翼雷达[J].国际航空,2010(4):71-72. GAO Fei.The front flap of Russian fifth generation fighter radar[J].International Aviation,2010(4):71-72. (in Chinese)

[4] 任燕飞,张云,曾浩,等.新型宽带数字多波束相控阵天线设计[J].电讯技术,2013,53(7):932-937. REN Yanfei,ZHANG Yun,ZENG Hao,et al.Design of a novel wideband digital multi-beam phased array antenna [J].Telecommunication Engineering,2013,53(7):932-937.(in Chinese)

[5] 刘冀川.5Gsps高速采样系统的设计与实现[J].无线电工程,2014,44(12):22-24. LIU Jichuan.Design and implement of 5Gsps high-speed sampling system[J].Radio Engineering,2014,44(12): 22-24.(in Chinese)

[6] 肖汉波.基于EV10AQ190的高速ADC接口设计[J].电子器件,2015(3):569-575. XIAO Hanbo.Design of interface circuit for high speed ADC based on EV10AQ190[J].Electron Devices,2015 (3):569-575.(in Chinese)

[7] 赵远志,李宏波,高鹏.基于软件无线电的导航信号直接带通采样方案研究[J].火控雷达技术,2011(4):61-65. ZHAO Yuanzhi,LI Hongbo,GAO Peng.Study on plan of RF direct bandpass sampling to navigation signals based on SDR[J].Fire Control Radar Technology,2011(4):61 -65.(in Chinese)

[8] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2004:100-120. YANG Xiaoniu,LOU Caiyi,XU Jianliang.The theory and application of software radio[M].Beijing:Publishing House of Electronics Industry,2004:100-120.(in Chinese)

[9] 刘云龙.基于FPGA的数字下变频器的设计[D].哈尔滨:哈尔滨工业大学,2007:17-32. LIU Yunlong.Digital down converter designing based on FPGA[D].Harbin:Harbin Institute of Technology,2007: 17-32.(in Chinese)

[10] ZAHIRNIAK D R,SHARPIN D L,FIELDS T W.A hardware-efficient,multirate,digital channelized receiver architecture[J].IEEE Transactions on Aerospace&E-lectronic Systems,1998,34(1):137-152.

王世涛(1968—),男,辽宁清原人,1991年于海军电子工程学院获雷达工程专业学士学位,现为高级工程师,主要从事电子装备的研制生产质量监督工作;

WANG Shitao was born in Qingyuan,Liaoning Province,in 1968.He received the B.S.degree from Naval Electronic Engineering Institute in 1991.He is now a senior engineer.He is engaged in quality supervision in development and production of electronic equipment.

李明兵(1982—),男,四川宜宾人,2009年获硕士学位,现为工程师,主要研究方向为航空电子一体化。

LI Mingbing was born in Yibin,Sichuan Province,in 1982. He received the M.S.degree in 2009.He is now an engineer. His research concerns avionics integration.

Email:12865579@qq.com

Design of a Highly Integrated P/L Band Aviation Platform

WANG Shitao1,LI Mingbing2

(1.Military Representative Bureau of Naval Equipment Department in Chongqing Area,Chengdu 610036,China; 2.Southwest China Institute of Electronic Technology,Chengdu 610036,China)

In order to further improve aviation platform integration,a P/L band highly integrated hardware scheme for aviation platform is designed.In the scheme radio frequency(RF)signal under 2 GHz is acquired directly through RF and in the digital domain baseband I/Q signals for detection,communication, navigation,identification and passive reconnaissance are separated,and finally the functions of various signals are completed with software,thus implementing highly integrated design of co-channel and shared signal preprocessing of such function as detection,communication,navigation,identification,and passive detection.Hardware implementation shows that this scheme can effectively reduce the cost and complexity of the hardware system design,reduce the power consumption of the system,and strongly promote the application of software radio in aviation platform integration.

P/L band integrated avionics;RF sampling;;software radio hardware platform;efficient preprocessing algorithm

**通信作者:12865579@qq.com 12865579@qq.com

TN911;V243

A

1001-893X(2016)11-1273-06

10.3969/j.issn.1001-893x.2016.11.016

2016-04-05;

2016-07-26

date:2016-04-05;Revised date:2016-07-26

引用格式:王世涛,李明兵.一种P/L频段高度综合化航空平台的设计[J].电讯技术,2016,56(11):1273-1278.[WANG Shitao,LI Mingbing. Design of a highly integrated P/L band aviation platform[J].Telecommunication Engineering,2016,56(11):1273-1278.]