|R|G-B(DC)码在光纤高精度授时设备中的应用

杨君刚,王 超,王 凯

(西安通信学院信息服务系,西安710106)

|R|G-B(DC)码在光纤高精度授时设备中的应用

杨君刚,王 超,王 凯

(西安通信学院信息服务系,西安710106)

为了实现光纤授时设备输入/输出标准IRIG_B(D C)码,提出了一种基于FPG A的IRIG-B(D C)编解码设计方案。通过Q uart us II建立工程文件,采用Veri log HDL语言设计了B(D C)码编解码电路,解决了传统设计中B码准秒时刻对齐和1PPS恢复的问题。

IRIG-B(D C);FPG A;Veri log HDL;1PPS

0 引言

近年来,随着通信、电力、金融和军事等领域对时间统一的要求越来越迫切,时间同步的精度要求越来越高,采用光纤时间传递技术的高精度授时设备的时间同步功能,可以为上述领域的时间终端设备提供标准时间信号和标准频率信号,满足用户对于高精度时间同步的要求[1]。

IRIG-B码作为一种标准时间信息码输出格式已被广泛应用于其它时间信息传输系统中,B码接口也成为高精度授时设备连接时间终端设备的必备接口之一[2]。在传统的基于微处理器的IRIG-B码编解码设计中,存在B码准秒时刻对齐和1PPS恢复的问题,同时不便于进行系统集成。针对此问题,本文提出了一种基于FPGA实现IRIG-B(DC)时间码编解码设计方案,将编解码模块进行一体化设计,在准确可靠实现编解码功能基础上,有效节省了硬件资源。目前已将其应用于实际的光纤高精度授时设备中,实现设备对外输出高精度的标准时间信息和1PPS信号。

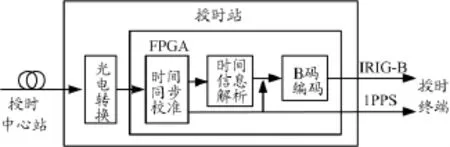

图1 IRIG-B码在光纤授时中的应用

1 IRIG-B(DC)码在光纤授时中的应用

在光纤授时系统中,授时中心站(主站)将标准的时间信息通过光纤传递到授时站(从站),同时对传输时延进行精确测量,通过主站或者从站补偿控制,实现主从站间的时间精确同步。如图1所示,授时中心站通过接收外部标准时间和1PPS信号获得时间信息,获得方式可以是脉冲或串口报文等形式;同样,授时站在接收主站时间信息并实现主从同步后,需要对外部的授时终端输出精确的时间信息和1PPS信号,一般也采用脉冲或串口报文形式。有人通过研究IRIG-B(DC)码的编码规则[3]发现,B码在传递时间信息的同时,还可以通过B码解码恢复出1PPS信号,因此通过对IRIG-B(DC)码编解码的合理设计和控制,可以实现时间信息+1PPS的高精度传递。

以授时站编码输出为例,在接收到授时中心站传来的包含有时间信息的光脉冲信号后,首先通过光电转换模块获得时间同步单元可以接收的电信号,然后将其输入到以FPGA为平台的时间同步校准模块,通过内部逻辑功能设计实现主从站的时间同步。为了对外部授时终端提供时间信号和1PPS的输出,一方面通过时间同步校准模块进行内部分频,产生精确的1PPS信号;另一方面通过时间同步校准模块将时间信息输出给时间信息解析模块,完成对时间信息的解析,获得B码编码所需要的时间信息;然后结合生成的1PPS信号,在内部时钟驱动下生成串行IRIG-B (DC)码;最后通过符合RS422/485电平标准的RJ45接口进行输出,提供给具有B码解码功能的授时终端使用。

2 IRIG-B(DC)码的编码和解码

2.1 编码模块设计

采用FPGA进行IRIG-B(DC)编码设计[4,5]是指将来自其它标准时间系统(如GPS、北斗、长短波等授时设备)的标准时间中的天、时、分、秒信息和TOD时间信息按照B码的编码格式进行编码,然后将其串行输出,并且使B码的准秒时刻与1PPS的上升沿保持对齐,从而保证时间的精度。

整个方案采用Verilog HDL语言进行设计。设计思路如下:FPGA利用原子钟提供的10MHz时钟信号经倍频产生20MHz时钟作为主时钟,同时为了节省FPGA硬件资源,利用内部分频电路对其进行分频处理,得到编码所需要的100PPS、1000PPS和10000PPS等脉冲控制信号,以减少计数器规模;然后在上述控制信号的作用下将输入的时间信息通过编码模块进行编码,从而生成IRIG_B(DC)串行码输出。

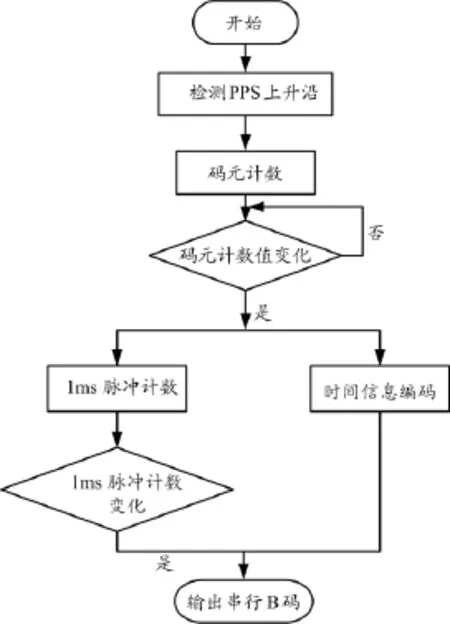

编码模块的设计流程如图2所示,主要包括:1PPS上升沿检测、码元计数、码元计数值变化检测、1ms脉冲计数、时间信息编码和编码输出等步骤。

①1PPS上升沿检测。按照B码编码规则,其准秒时刻表示一秒的开始时刻,对应1PPS信号的上升沿,因此在设计中使用内部主时钟20MHz对1PPS信号进行检测,一旦检测到其上升沿,立即对码元计数值、1ms脉冲计数值和时间信息编码寄存器进行清零,生成编码使能信号开始编码,以此保证B码准秒时刻与1PPS上升沿严格对齐。

图2 编码模块的设计流程

②码元计数。在100PPS信号的上升沿触发下,如果同时检测到1PPS信号的上升沿后,则计数清零重新开始计数,否则计数值加1,直到计数值等于99再次清零。码元计数值变化检测:在10000PPS信号的上升沿触发下,检测码元计数值是否发生变化,如果计数值变化,则产生一个高窄电平的脉冲作变化标志,否则保持低电平。

③1ms脉冲计数。在1000PPS信号的上升沿触发下,如果检测到码元计数值变化所产生的高窄脉冲,则计数清零,否则计数加1,直到计数到9再次清零。

④时间信息编码。按照IRIG-B(DC)的编码规则,将输入的时间信息随码元计数值变化进行编码。

⑤编码输出。在1ms脉冲计数值变化时将生成的码元按照串行方式进行输出。

2.2 解码模块设计

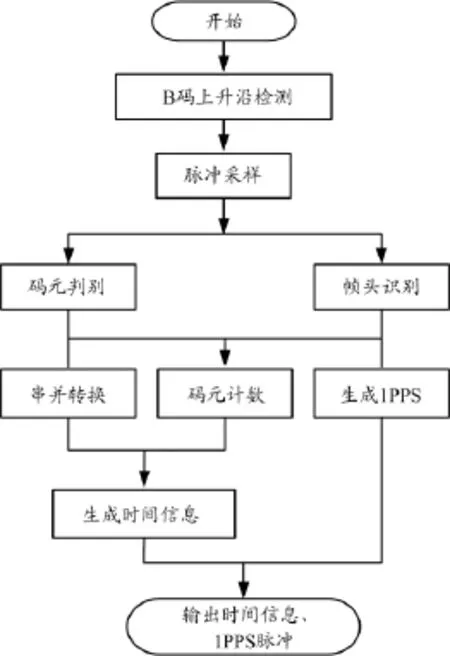

对输入的IRIG-B(DC)进行解码[6]就是将输入的B(DC)串行码中所包含的天、时、分、秒信息和TOD时间信息提取出来,同时通过检测准秒时刻恢复出1PPS信号。解码模块的设计流程如图3所示,主要包括以下几个步骤:B码检测、脉冲采样、码元判别、帧头识别、串并转换、码元计数和时间信息及1PPS信号输出。其中解码的关键在于帧头识别和1PPS生成。关键部分设计介绍如下:

图3 解码模块的设计流程

①码元判别。首先检测输入的IRIG-B(DC),在每个码元的上升沿开始每间隔2.2ms进行采样,则各码元对应的采样值分别为:0码元(0000)、1码元(1100)、P码元(1110)。因此按照该对应关系就可以获得相应码元位置的码元信息,然后将其存入位宽为100的编码信息寄存器的相应的位。在此规定将所有P码元以0码元进行存储。

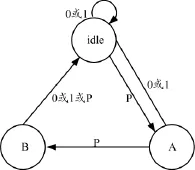

②帧头识别。从IRIG-B(DC)码的编码格式可以发现,当连续出现两个P码元的时候,则第二个P码元即为PR参考点,同时也是准秒时刻,其上升沿与1PPS的上升沿对齐。本文为此设计了一个三段式有限状态机(FSM),同时对采样值采用独热编码方式以实现帧头定位,状态转换图如图4所示。其中,idle为初始状态(001),当检测到采样值为1110(即P码元)时,跳转至A状态(010),否则保持状态不变;在A状态下,若检测到下一个采样值为1110,则跳转至B状态(100),否则跳回idle状态;在B状态下,无论下一个码元是P码元还是0或者1,都跳转至idle状态。

图4 帧头识别状态转换图

③1PPS信号输出。如图5所示,帧头识别完毕后,接下来每接收到一个P码元就对其计数值加1。当计数值为10时产生一个脉冲控制信号mask,并使其维持高电平;在接收到下一个码元的时候,将计数值清零、mask信号拉低,然后将其与输入的B码信号进行相与运算,即可得到1PPS信号。

图5 生成1PPS脉冲

④时间信息和秒脉冲输出。在码元识别中,通过采样得到了B码的码元信息,并保存在编码信息寄存器中,然后按照B码的编码格式,辅以年时间信息就可以得到完整的UTC时间和TOD时间。同时将帧头识别中恢复出的1PPS进行输出。

3 设计实现与功能验证

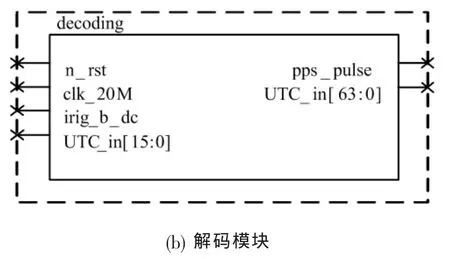

我们用Quartus II建立工程文件,编辑Verilog HDL代码进行设计[7],分别得到编解码模块的原理图如图6所示。

其中,图6(a)为编码模块,输入信号包括复位信号rst_n、秒脉冲信号pps_1、时钟信号clk_20M以及包含时间信息的UTC时间UTC_in[63:0],输出即为IRIG_B (DC)串行码irig_b_dc。图6(b)为解码模块,输入信号包括复位信号rst_n和时钟信号clk_20M以及IRIG_B (DC)码irig_b_dc,同时为了能够对外输出标准UTC时间,添加年时间信息UTC_in[15:0],经过解码模块后生成完整的UTC时间信息UTC_out[63:0]和准确的1PPS信号pps_pulse。

图6 编解码模块设计图

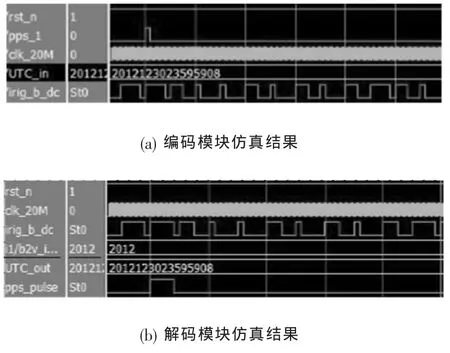

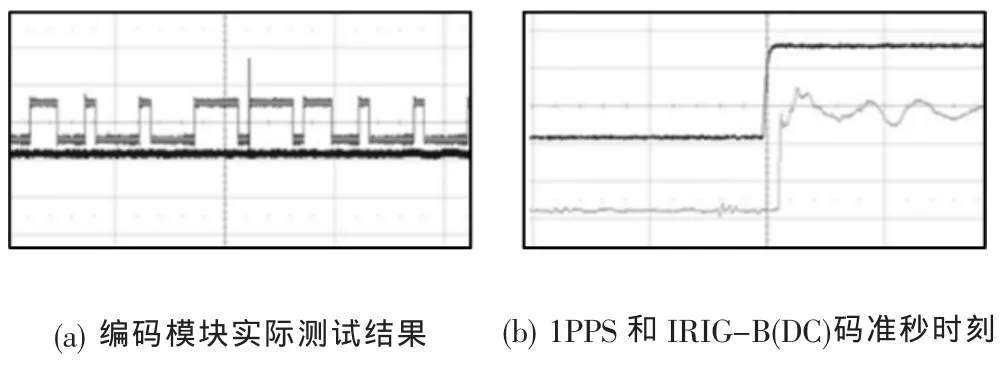

针对前文设计的编、解码模块,本文在ModelSim Altera 6.6d下进行了功能仿真验证[7],目前已将该编、解码模块在 Altera公司的 Cyclone III EP3C16-Q240C8芯片中实现,并应用到光纤高精度授时设备上。ModelSim仿真结果和实际设备测试结果如图7和图8所示。

图7 ModelSim功能仿真结果

图8 编码模块实际应用结果

在对编码模块进行ModelSim功能仿真验证时,输入时间UTC_in[63:0]为 16′h2012123023595908,则编入B码中的时间信息应为365天23时59分59秒,TOD=86399。仿真结果如图7(a)所示,串行输出的B码码元符合编码格式,输出时间信息符合预期。在对解码模块进行功能仿真验证时,为了便于产生激励,将编码模块的输出IRIG_B(DC)码直接作为解码模块的输入,输出结果如图7(b)所示。仿真结果表明,解码模块可以正确输出时间信息,同时能够正确恢复出1PPS信号。

我们将编码模块应用到光纤高精度授时设备上的实际测试结果如图8所示。其中,图8(a)是通过示波器观察到的设备输出的IRIG-B(DC)码和1PPS信号;图8(b)是对1PPS信号上升沿和IRIG-B(DC)码准秒时刻位置局部放大图。通过实测得到两者时间差skew值约为11.8ns,实现了1PPS上升沿和B(DC)码准秒时刻高精度对齐。

4 结束语

本文提出了一种基于FPGA的IRIG-B(DC)码的编解码实现方案,仿真结果表明,采用本方案所设计的IRIG-B(DC)编码模块可以产生稳定、可靠、连续的B(DC)码,保证与1PPS信号精确同步;解码模块也能够对输入的标准IRIG-B(DC)码实现正确解码输出,生成标准UTC时间信息和1PPS信号;解决了传统设计中B码准秒时刻对齐和1PPS恢复的问题。通过在光纤高精度授时设备上的实际应用,本文进一步验证了编解码模块输出的有效性和可靠性,保证了光纤高精度授时设备的时间同步精度,展现了良好的应用效果。

[1]王苏北.高精度光纤时间传递的码型设计与实现[D].上海:上海交通大学,2013.

[2]童宝润.时间统一系统[M].北京:国防工业出版社,2000.

[3]国防科学技术工业委员会.IRIG-B码接口终端[S].北京国防科学技术工业委员会,1991.

[4]胡跃祥,刘浩,张捷.基于GPS的IRIG-B直流码编码器设计[J].工业控制计算机,2014,28(4):98-100.

[5]XU Qiaoyu,WANG Xing.Design of IRIG-B Code Encoder Based on SOPC[C].The 2nd International Conference on Computer Application and System Modeling,2012:103-106.

[6]陈永胜.基于FPGA的IRIG-B(DC)解码器的设计与实现[J].无线电通信技术,2014,40(1):93-96.

[7]王金明,徐志军,苏勇.EDA技术与Verilog HDL设计[M].北京:电子工业出版社,2013.

Application of IRIG-B(DC)code in high precision timing devices based on optical fiber

YANG Jun-gang,WANG Chao,WANG Kai

(Department of Information service,Xi'an Communications Institute,Xi'an 710106,China)

In order to realize a port of the standard IRIG-B(DC)code for timing device based on optical fibers, a new designing scheme of IRIG-B(DC)coding and decoding based on FPGA was proposed.The coding and decoding circuits were designed by Verilog HDL in Quartus II,and the problems of the traditional B code with seconds time alignment and 1 PPS recovery was solved.

IRIG-B(DC),FPGA,Verilog HDL,1PPS

TN929.11

A

1002-5561(2016)03-0029-04

10.13921/j.cnki.issn1002-5561.2016.03.009

2015-11-11。

杨君刚(1973-),男,博士,副教授,主要从事光纤时间传递技术、通信网络关键技术研究。