基于SiGe HBT的38 GHz功率放大器设计

邸士伟,刘 昱,李志强,张海英

(中国科学院微电子研究所 “新一代通信射频芯片技术”北京市重点实验室,北京 100029)

基于SiGe HBT的38 GHz功率放大器设计

邸士伟,刘昱,李志强,张海英

(中国科学院微电子研究所 “新一代通信射频芯片技术”北京市重点实验室,北京 100029)

功率放大器(Power Amplifier,PA)是射频前端关键的模块,基于0.13 μm SiGe HBT工艺,设计了一款 38 GHz功率放大器。提出了HBT集电极寄生电容和传输线谐振的方法减小芯片面积,针对毫米波频段下,晶体管可获得最大增益较低,采用堆叠晶体管提高了功率放大器的增益,同时通过优化有源器件参数,提高了功率放大器的输出功率和效率。仿真结果显示,在4 V的供电电压下,工作在38 GHz的功率放大器1 dB压缩点输出功率为17.8 dBm,功率增益为19.0 dB,功率附加效率为32.3%,功耗为252 mW。

功率放大器;38 GHz;HBT;有源偏置

0 引言

近年来,随着移动互联网的蓬勃发展,移动通信数据呈现爆炸式的增长,现有的通信系统很难满足人们未来生活的需求。为了提高数据容量和通信速度,需要增加信道带宽,相比于拥挤的几百兆赫兹到几吉赫兹频段,毫米波频段有大量的有待开发的频谱资源,是无线通信领域最具发展潜力的技术之一。

作为收发机中最为重要的模块,功率放大器(PA)的性能决定着整个通信系统。CMOS功率放大器成本较低,但是输出功率较低和线性度较差,目前很难满足通信系统的要求。化合物半导体(砷化镓等)功率放大器工艺集成度低,成本过高[1-2]。SiGe工艺实现了性能和成本的平衡,而且效率高、增益大、线性度好、功率密度高,非常适合于功率放大器的设计,受到了国内外学术界和产业界的普遍关注。

工作在毫米波频段的功率放大器由于寄生电容影响增大、无源器件损耗增加,导致晶体管可获得增益较低,输出功率较小。针对该问题,本文基于0.13 μm SiGe工艺,设计了一款工作在 38 GHz频率的单级功率放大器,采用堆叠(Stacked)异质结(HBT)结构,提高了增益;通过优化级间有源器件尺寸、偏置等参数,实现了较高输出功率和效率的功率放大器。

1 技术原理

图1 传统功率放大器结构

如图1所示为传统功率放大器的基本结构[3],在毫米波频段,利用四分之一波长传输线作为晶体管负载阻抗。对于不同的工作频率和工艺,四分之一线长度不同。但是即使在 38 GHz,本项目使用的工艺下,四分之一波长仍有 930 μm,片上实现需要很大面积,而且传输线引入的插入损耗与其长度成正比,过长的传输线降低了功率放大器的输出功率和效率。

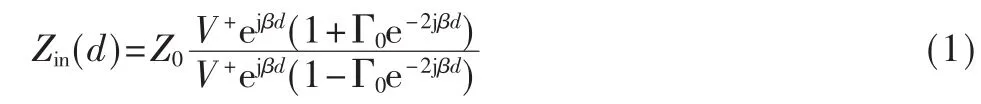

依据传输线理论,不同长度的传输线可以用来实现不同的电抗,长度为d的传输线终端接负载ZL的输入阻抗可以用下式表示[4]:

其中,V+表示入射波电压,Γ0表示终端反射系数,β表示相位阐述,Z0为传输线特征阻抗。当传输线终端短路时,Γ0=-1,式(1)可以化简为:

可以看出,当传输线长度不同时,可以表示不同的周期性变化电抗值,而且当传输线长度小于四分之一波长线时,传输线的作用等效为电感,等效电感值为:

HBT结构形成了许多PN结,所以有许多结电容。在集电极端,主要有有集电极-基极结电容 Cμ,集电极-衬底结电容CCS,将集电极对地总电容记为CC,如图1所示。

由于HBT集电极电容的存在,可以通过使传输线等效电感和HBT集电极寄生电容谐振实现高负载阻抗,谐振频率如式(4):

从式(4)可见,通过设计传输线的长度和特征阻抗等参数实现所需要的谐振频率。相比于在四分之一波长传输线,这种负载结构Q值降低,功率放大器带宽增大,而且传输线长度显著减小,因此减小了损耗,降低了芯片面积,节省了成本。

2 电路设计

2.1原理图设计

本文基于IBM 0.13 μm SiGe工艺,设计了一款采用有源偏置电路的功率放大器,其电路结构如图2所示。采用堆叠(Stacked)2个 HBT结构,其有以下优点:(1)增益近似是共射极HBT结构的两倍,单级放大器就可以实现很高的功率增益;(2)由于HBT击穿电压较小,采用这种结构提高电源电压,提高了输出功率;(3)功率放大器的输出电阻放大了(1+gmRout)倍,增强了驱动负载的能力[5];(4)反向隔离度(S21)增大,使得输出信号对输入信号的干扰减小。利用上文提到的传输线和集电极电容谐振的方法,使得传输线TL1长度从930 μm(四分之一波长)减小到 405 μm,面积和损耗减小,提高了输出功率和效率。输入端匹配电路将端口50 Ω匹配到晶体管输入阻抗的共轭值以减小信号反射;输出端利用负载线原理优化负载阻抗值,实现最大输出功率。

图2 功率放大器电路结构

2.2有源器件设计

本项目所用工艺中,提供了高速和高压两种类型的HBT器件,主要参数如表1所示。高击穿电压HBT结构对应截止频率低,高截止频率HBT对应增益较高,为了提高放大器增益,选用高速HBT器件。击穿电压BVceo= 1.8 V,BVceo是基极开路时发射极-集电极的击穿电压,而当基极处于低阻,BVce超过5 V,因为雪崩击穿产生的空穴经低阻的基极流出[6]。HBT尺寸需要多方面的考虑折中,增加HBT发射极面积可以增加输出功率,但是随着 HBT尺寸的增加,输出最优负载阻抗(Zopt)和输入阻抗(Zin)减小,输出最优阻抗匹配到 50 Ω和将输入阻抗匹配到 50 Ω难度增大,增大HBT发射极面积增加的输出功率被匹配电路消耗,因此发射极面积存在最优值。晶体管的偏置决定了功率放大器的工作状态,偏置较低,PA的效率较高,但是可能产生增益膨胀效应,线性度变差;偏置较高时,增益和线性度提高,相应功耗也较高,静态工作点的选择要在线性度,功耗,效率,增益中进行优化。综合考虑,选择基极电压为0.83 V。输出电压过低时会导致Stacked HBT提前进入饱和区而限制了输出电压摆幅,同时偏置过低会导致共射极HBT集电极-发射极电压过高而击穿。Stacked HBT基极电压选择为2 V。

表1 HBT主要工艺参数

2.3有源偏置电路设计

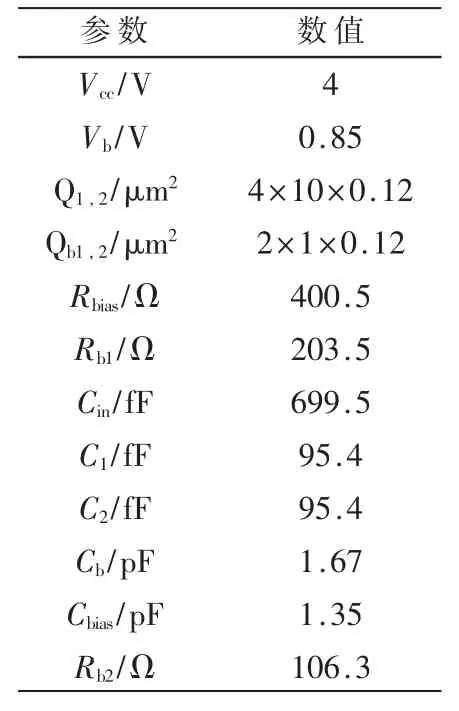

功率放大器的偏置常采用电阻分压或者电感实现。但是由于电阻在工艺制造中误差较大[7],引起偏置不准确。电感偏置实现所占用芯片面积较大,同时在毫米波段,工艺库提供电感通常Q值很低,需要通过电磁仿真设计,不易实现。而有源偏置电路具有实现面积小、设计方便的优势,如图中虚线框所示,由二极管连接的 Qb1、Qb2和电阻 Rbias1和电容 Cb给镜像支路 Qb3提供稳定的基极电位,Rbias2的加入减小了Qb3的非理想因素,提高偏置的稳定度。通过改变Q1,Q2,Rbias1的参数使得偏置电路输出稳定的 0.83 V电压。本设计电路器件参数如表2所示。

表2 功率放大器原理图器件参数信息

3 结果及分析

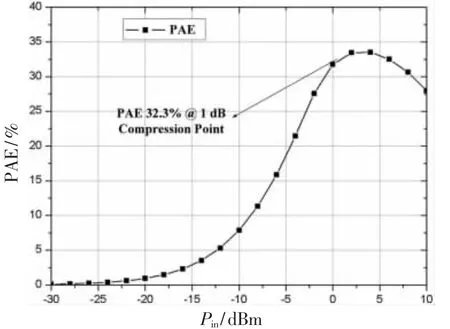

采 用 Cadence Spectre软件对电路进行仿真,仿真结果如图3~图5所示,从图中可以看出,在整个频带内,稳定性因子(K)大于1,功率放大器无条件稳定;在 35~40 GHz内,S11<-10 dB;输出1 dB压缩点功率(P1dB)17.8 dBm,P1dB处的功率附加效率(PAE)为33.2%,在38 GHz处功率增益达到最大值19.0 dB,功耗252 mW。表3给出了本设计与其他文献的性能对比,可以看出,本文设计的功率放大器提高了输出功率、增益和效率。

图3 S11,S21,K随频率变化关系

图4 PA输出功率(Pout)和功率增益(Gp)

图5 PA功率附加效率(PAE)

表3 本文功率放大器性能与文献对比

4 结论

本文基于 IBM 0.13 μm SiGe工艺设计了一种应用于38 GHz频段的功率放大器。由于四分之一波长占用面积较大,提出了利用传输线的电感效应和HBT寄生电容谐振的方法,减小了芯片面积;同时采用堆叠HBT的结构,提高了功率放大器的增益;通过优化有源器件的尺寸和静态工作点,增加了输出功率和效率。仿真结果表明:38 GHz功率放大器 1 dB压缩点输出功率为17.8 dBm,功率增益为 19.0 dB,1 dB压缩点处的功率附加效率(PAE)为32.3%,功耗为252 mW。与其他文献对比,本设计实现了输出功率大,增益和效率高的设计目标。

[1]Ali M,HASHEMI N H.Mm-Wave silicon technology 60 GHz and beyond[M].Cambridge:Springer,2008:81-83.

[2]HSIEN C,BO K.High performance V-band GsAs power amplifier and low noise amplifier using low-loss transmission line technology[C].Nanjing:High Speed Intelligent Communication Forum,2012.

[3]池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2006.

[4]REINHOLD L,PAVEL B.RF circuit design theory and applications[M].北京:科学出版社,2003:69-77.

[5]AUSTIN C,YVES B,YOUNG C,et al.An 83-GHz Highgain SiGe BiCMOS power amplifier using transmission-line current-combining technique[J].Transactions on Microwave Theory and Techniques,2013,61(4):1557-1569.

[6]KUNAL D,HOSSEIN H.Performance limits,design and implementation of mm-Wave SiGe HBT Class-E and stacked Class-E power amplifiers[J].Journal of Solid-State Circuits,2014,49(10):2150-2171.

[7]TOLGA D,ILKER K,MEHMET K,et al.An X-band,high performance,SiGe-HBT power amplifier for phased arrays[C]. Proceeding of the 7thEuropean Microwave Integrated Circuits Conference.Amsterdam:IEEE,2012.

[8]HAYG D,JOOHWA K,LAWRENCE E,et al.A 45-GHzSiGe HBT amplifier at greater than 25%efficiency and 30 mW output power[C].Bipolar/BiCMOS Circuits and Technology Meeting.Atlanta:IEEE,2011.

[9]NADER K,JAMES F.A 19.4 dBm,Q-band class-E power amplifier in a 0.12 μm SiGe BiCMOS process[J].Microwave and Wireless Components Letters,2010,20(5):283-285.

A 38 GHz power amplifier based on SiGe HBT process

Di Shiwei,Liu Yu,Li Zhiqiang,Zhang Haiying

(Beijing Key Laboratory of Radio Frequency IC Technology for Next Generation Communications,Institute of Microelectronics of Chinese Academy of Sciences,Beijing 100029,China)

Power Amplifier(PA)is an important unit in the RF front-ends.A 38 GHz power amplifier is designed based on 0.13 μm SiGe HBT process.This paper proposed a method to decrease chip area.Due to the low maximum stable gain of transistors in millimeter wave frequency band,stacked HBT structure is utilized to improve power gain of the PA.High output power,gain,and efficiency are achieved by optimizing the active devices.The simulation results show that the PA achieves an output 1 dB compression point power of 17.8 dBm,power gain of 19.0 dB,power add efficiency(PAE)of 32.3%at 1 dB compression point,and has 252 mW power dissipation.

power amplifier(PA);38 GHz;HBT;active baising

TN722.1

A

10.16157/j.issn.0258-7998.2016.02.009

邸士伟(1989-),男,硕士研究生,主要研究方向:毫米波集成电路设计。

刘昱(1975-),男,博士,研究员,主要研究方向:高性能模拟/射频 CMOS集成电路,硅基毫米波集成电路,超低功耗短距离无线通讯系统等。

中文引用格式:邸士伟,刘昱,李志强,等.基于SiGe HBT的38 GHz功率放大器设计[J].电子技术应用,2016,42(2):36-38,45.

英文引用格式:Di Shiwei,Liu Yu,Li Zhiqiang,et al.A 38 GHz power amplifier based on SiGe HBT process[J].Application of Electronic Technique,2016,42(2):36-38,45.