基于RMAP机制的SpaceWire星载高速总线设计与实现

闫梦婷,安军社,龚泉铭

(1.中国科学院 空间科学与应用研究中心,北京 100190;2.中国科学院大学,北京 100190)

基于RMAP机制的SpaceWire星载高速总线设计与实现

闫梦婷1,2,安军社1,龚泉铭1,2

(1.中国科学院 空间科学与应用研究中心,北京 100190;2.中国科学院大学,北京 100190)

基于RMAP协议对 SpaceWire高速总线进行了架构设计与实现。首先给出了 SpaceWire高速总线的整体设计;其次对SpaceWire编解码器中的DS编码进行了优化;然后根据RMAP协议的基础要求,设计了 RMAP SpaceWire总线的工作流程与实现方法;最后通过仿真平台对该设计进行仿真测试。仿真测试表明:设计实现了RMAP SpaceWire高速总线的基础功能,数据链路传输速度可以达到79.84 Mb/s。

SpaceWire;RMAP;DS编解码;高速总线

0 引言

SpaceWire高速总线标准是ESA (European Space A-gency)于 2003年正式通过的一种总线标准。ESA基于IEEE 1355-1995和IEEE 1596.3(LVDS)两个商用总线标准,并且根据航天应用的特点,在可靠性、功耗等方面进行了改进,实现了一种串行、高速、点对点、全双工的专用于空间高速数据传输的总线标准。该标准提供了一种统一用来连接传感器、数据处理单元、大容量存储器的基础架构,具有很好的EMC特性,并且在错误检测、异常处理、故障保护和故障恢复及时间确定性方面也做了相应加强。使得SpaceWire能够满足新一代航天器电子系统对总线结构的性能要求,具有独特优势。

SpaceWire由节点、链路和路由 3部分组成,在基础协议簇中对这3个重要单元进行了定义和功能设计,目前已有成熟的IP核、软件支持和测试设备等研究成果,使得SpaceWire应用于多个空间任务中。SpaceWire能够在物理层和数据链接层满足空间航天器中标准化的高速率网络交互需求,SpaceWire工作组目前致力于高层协议的研究,拟定首个SpaceWire高层协议,即RMAP(Remote Memory Access Protocol)。

国际上拥有SpaceWire协议IP核产品的公司与科研机构主要包括 STAR-dundee和ESA等,相关产品主要包括 Codec和Router IP核,不同型号 FPGA的实现性能则差异明显,GRSPW2 IP核集成的 Codec模块在 Xilinx基于SRAM的Virtex2系列FPGA中实现的收发数据率可达200 Mb/s,但在Actel公司的反熔丝RTAX系列FPGA实现性能仅为 100 Mb/s[1]。目前基于 flash技术 FPGA可实现的性能为180 Mb/s,该性能指标为ESA的Codec IP核在速度等级为-2的 ProASIC3系列 FPGA中的实现结果[2]。

目前我国已对SpaceWire开展研究并取得一定成果。文献[3]完成了 SpaceWire链路接口 IP核和 SpaceWire与PCI总线之间的接口卡设计,SpaceWire链路接口工作速度可达100 Mb/s。文献[4-5]对SpaceWire在运载火箭中的应用以及实时分布式中断系统设计进行了研究。文献[6]主要对 SpaceWire CODEC IP核进行了设计,链路速度可达80 Mb/s。本文在SpaceWire节点、链路和路由3个重要单元的基础上,设计了基于RMAP的SpaceWire路由工作机制。为SpaceWire总线中各节点间的功能提供了标准化工作机制。

1 SpaceWire总线整体架构设计

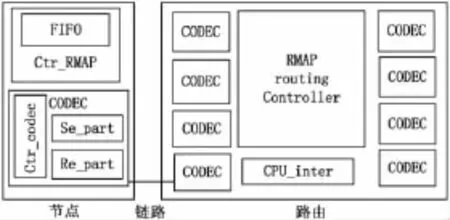

SpaceWire总线网络由节点、链路和路由器三种基本单元组成。SpaceWire节点是指传输包的流出设备或者流向设备,一般是处理器、存储单元、传感器或连接在SpaceWire网络上的其它单元。SpaceWire链路是指传送数据包的传输路径,连接在各个节点之间,数据包通过链路进行传输通信。SpaceWire路由则实现了节点通过链路进行数据交换机制。本设计中基于RMAP高层协议的SpaceWire总线整体架构如图1所示。

图1 SpaceWire总线平台示意图

图中节点(Note)、链路(Link)和路由器(Router)是构成SpaceWire总线的基本单元。节点用于连接外接设备和总线,节点模块包括RMAP外设控制模块(Ctr_RMAP)和编解码器模块(CODEC)。外接设备数据接口连接到节点中RMAP外设控制模块里的FIFO(First-In-First-Out)中,数据经过RMAP外设控制模块处理为符合RMAP传输要求的数据包后,通过编解码器进行编码,链路传输至SpaceWire总线路由器。图1中内部包含8个编解码器,编解码器接收到数据包后,通过接收模块(Re_part)进行译码,然后通过RMAP路由器进行路由,送至目的地址,通过目的地址接口的编解码器进行编码,输出总线路由器。编解码器同时在节点和路由器中调用,主要包括接收模块、发送模块以及控制模块。接收模块实现接收数据包及译码功能,发送模块实现发送数据包及编码功能。控制模块则实现了编解码器执行收发数据包功能的状态机。

2 SpaceWire编解码器优化设计

SpaceWire基础协议定义了信号层、字符层和交换层,这几个低层协议定义的功能由编解码器实现。SpaceWire总线的信号层定义了SpaceWire总线中传输信号的电压水平、噪声幅度和编码方式。指定采用低压差分信号(LVDS)作为信令技术,这是由于LVDS是一种高速数据传输、省电、抑制噪声、成本低以及可以采用较高集成度的技术,能够满足供电电流低、功率低的要求,有助于降低系统成本。

2.1DS解码电路的优化设计

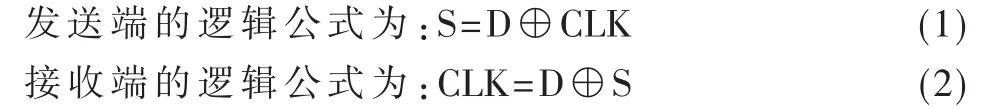

SpaceWire总线的信号编码采用DS(Data-Strobe)编码。DS编码如式(1)和式(2)定义:

根据上述公式,搭建门电路时若用简单的组合逻辑实现异或,容易产生竞争冒险,导致接收到的数据异常。为了对该现象进行改进,探讨DS信号变化的内在规律。从图2中左图可见,DS信号的每次转换有且只变换其中的1位信号,通过2次变换后DS数据都将发生翻转。

图2 DS信号转移图

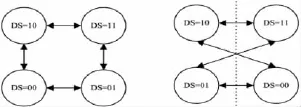

从DS编码规律可知,有且只有当时钟信号为上升沿时,D和S信号发生从同相至反相的跳变;同理,有且只有当时钟信号为下降沿时,D和S信号发生从反相至同相的跳变。根据上述分析结论设计的DS数据时钟恢复电路如图3所示。图3电路是由异或门、锁存器以及触发器构成。当时钟信号为上升沿时,同相状态的 data数据将保持不变,如图3中上方电路;当时钟信号为下降沿时,反相状态的 data数据将保持不变,如图3中下方电路。

图3 优化后的DS解码电路

2.2SpaceWire的数据字符与控制字符

SpaceWire总线标准的字符层定义了数据字符、控制字符和控制码、奇偶校验以及时间码等内容,此外为了更好地支持路由和网络协议,还提供了 Time-Code来支持在网络层传播系统时间。字符层定义有数据字符和控制字符。数据字符包含8位有效数据位,一位奇偶校验位、一位为0的标志位。控制字符有4个,分别是FCT、EOP、EEP和 ESC,编码由 4个位构成,包含一位奇偶校验位,一位为1的标志位和两位控制数据。协议中还有两个重要的控制码NULL和Time-Code,其中NULL是由控制字符ESC加上FCT组成的。当链接不传送数据或控制字符时,SpaceWire端口通过传送NULL字符维持链路连接。

3 SpaceWire路由器设计

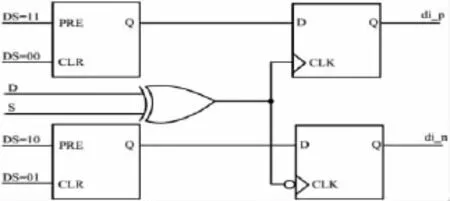

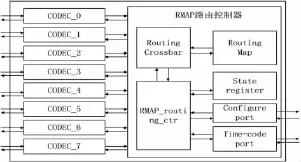

本设计中的8口基于RMAP的SpaceWire路由器如图4所示,8个编解码器用于接收和发送数据包,与上述介绍的编解码器模块一致。

图4 基于RMAP的SpaceWire路由器框图

基于 RMAP的 SpaceWire路由器中核心模块为RMAP路由控制器,路由矩阵实现了各个接口之间的链路搭建。RMAP路由管理器实现功能控制和工作协调,路由表用于地址索引,Time-Code管理模块用于 Time-Code码的广播,减少时间误差。配置端口模块用于实现对路由表配置等工作。SpaceWire的路由地址表用于配合逻辑地址的索引,使用路径地址来表示目的地址时,目的地址由一系列路由器的输出端口标识符组成,通过这一系列路由标识符来决定包在网络中的传播路径,将包从发送端传输到目的地址。

RMAP协议提供了一个标准化的方案,使得一个SpaceWire节点能够对另一个SpaceWire节点进行读写操作、传输数据。协议中包含3种操作,即写操作、读操作以及读改写操作。

写操作包括非数据校验非应答写、非数据校验应答写、数据校验非应答写、数据校验应答写4种不同的写操作。数据校验类写操作为了实现对数据的检查校验,需要在写操作之前在目的节点将数据缓存。但由于存储单元数量有限,无法满足大量的缓存需求,因此此类写操作应该用于相对短的数据。非数据校验可用于数据量较长的写操作,目的节点接到写操作指令后立即执行写数据的动作,无需缓存数据进行校验。

读操作机制提供了一个策略给源节点,源节点根据该策略去读取目的节点存储区域内的一个或者多个字节的数据。读取的数据将被封装在一个数据包中返回到源节点。当它到达源节点时,源节点用户将从数据包中得到所读取的数据。

读改写指令读取一个寄存器或者存储器的数据,返回它的值,并对寄存器写入一个新的值,新的值被确定在指令中。RMAP读修改写操作的发起方能够将网络中其它节点指定存储区域的数据读出,并进行修改后重新写入该存储区。1次最大可实现4 B数据的读改写。

图5 RMAP SpaceWire路由器工作流程图

图6 RMAP SpaceWire路由器工作波形图

4 仿真与总结

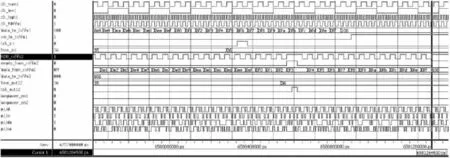

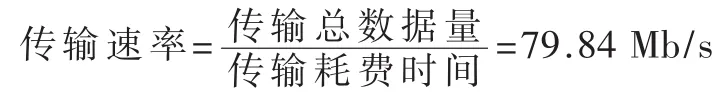

在 Modelsim6.2g下,通过 Xilinx Virtex-4 FPGA开发平台上搭建仿真平台,对SpaceWire总线进行仿真测试,波形如图6所示。图中显示优化后的DS编码波形图,D和S信号能够精确跳变实现DS编解码功能。通过仿真波形可以看出,RMAP SpaceWire总线在工作时,能够进行连续大数据量的时间码与数据包收发,运行正常。数据发送的起始时间 Tstart与接收完成时间 Tend分别为40μs和6 581μs,可以得出传输速率为:

由此可以看出,本设计基于RMAP这一先进的高层通信协议设计实现的SpaceWire总线平台能够完成数据包的路由通信,传输速率达到高速总线的使用需求。

[1]WORSFOLD P.Evolution of the MARC SpaceWire and power disstribution architecture from concept to tested hardware[C].International SpaceWire Conference,2010.

[2]WALKER P.IEEE 1394 compared with SpaceWire.4Links Ltd.,Milton Keynes,2004.

[3]Asaf Baron.Benchmarking SpaceWire Networks[C].International SpaceWire Conference,2007.

[4]Philippe Fourtier.Simulation of a SpaceWire Network[C]. International SpaceWire Conference,2010.

[5]WOLFRAM K D.A new radiation-hardened satellite on board LAN based on IEEE Std 1394,AIAA 2004-5869,2004.

[6]杨志,李国军,李芳,等.SpaceWire星载网络通信协议设计[J].宇航学报,2012,33(2):200-209.

[7]田园,张杰.基于SpaceWire的链路状态算法研究与设计[J].计算机工程,2011,37(23):113-115.

Design and implement of SpaceWire on-board high speed bus based on RMAP protocol

Yan Mengting1,2,An Junshe1,Gong Quanming1,2

(1.Center for Space Science and Applied Research,Chinese Academy of Science,Beijing 100190,China;2.University of Chinese Academy Sciences,Beijing 100190,China)

The structure of SpaceWire high speed bus is designed and realized base on RMAP protocol.The basic design of SpaceWire high speed bus is given first.Method is given for the realization of the functions of encoder and decoder.The working process and realization of RMAP SpaceWire bus is designed according to basic requirements of RMAP protocol.In the final part, the design is tested on a simulation platform.The result shows that our design realize the basic functions of RMAP SpaceWire high speed bus.The transmission speed of the data link can reach 79.84 Mb/s.

SpaceWire;RMAP;DS(Data-Strobe)encode and decode;high speed bus

TN95

A

10.16157/j.issn.0258-7998.2016.01.028

2015-08-31)

闫梦婷(1989-),通信作者,女,博士研究生,主要研究方向:星载电子系统、计算机应用技术,E-mail:yanmengting0101@163.com。

安军社(1969-),男,博士,研究员,主要研究方向:星载电子系统、星载计算机系统。

龚泉铭(1990-),男,博士研究生,主要研究方向:星载电子系统、计算机应用技术。

中文引用格式:闫梦婷,安军社,龚泉铭.基于RMAP机制的SpaceWire星载高速总线设计与实现[J].电子技术应用,2016,42(1):108-110,114.

英文引用格式:Yan Mengting,An Junshe,Gong Quanming.Design and implement of SpaceWire on-board high speed bus based on RMAP protocol[J].Application of Electronic Technique,2016,42(1):108-110,114.