SRIO交换单元的任意互连设计实现*

王青波,高 俊,崔中普

(海军工程大学 电子工程学院,湖北 武汉 430033)

SRIO交换单元的任意互连设计实现*

王青波,高 俊,崔中普

(海军工程大学 电子工程学院,湖北 武汉 430033)

SRIO采用基于设备ID的方式来搭建系统。在将SRIO应用于多通道短波通信系统时,交换单元的指定端口需接入指定的目标ID设备,而且交换单元全局的复位设计存在缺陷,在工作状态下热插拔接入设备时,将会引起整套系统的复位。根据对SRIO协议的可靠性传输机制、错误恢复机制及维护操作的分析,设计了一种似因特网交换机的动态设备ID分配、器件任意端口接入,且在热插拔接入时不对系统产生全局影响的SRIO交换单元实现方案。

SRIO;交换单元;错误恢复;任意互连

0 引 言

随着微处理器技术的发展、存储器性能的提升,各服务器之间的I/O性能越来越重要,且随着科学技术的发展,现在的系统越来越复杂,越来越趋于I/O密集型系统。数据在网络和存储器之间频繁、高速地进行交换和传输,I/O性能的稳定性和可靠性成为制约系统性能的一个重要因素。

RapidIO是基于请求响应模型的可靠性传输总线。它凭借优异的性能在嵌入式系统中得到了广泛应用,是现在唯一的嵌入式国际互连标准[1]。但是,由于它采用了设备ID的标识方法,因此在使用交换器件连接SRIO设备时,必须遵循特定端口接入特定设备ID器件,且全局的复位设计会使各设备产生相互关联,致使整套系统复位,无法实现和因特网交换机一样的各个设备独立动态接入和IP动态分配功能。

1 I/O互连

1.1传统总线

I/O互连的发展经历了共享总线、分层总线、点对点传输总线。为了使系统的体积更小,性能更好,稳定性更高,便捷性更佳。I/O互连总线向着更高的数据传输速率、更低的EMI(ElectroMagnetic Interference)、更少的物理引脚等方向发展。

传统总线多采用并行工作方式。要提高此类总线的数据传输速率,只有通过提高传输数据的宽度和提高传输速率(即提高频率)达到。第一,提高数据宽度也就增加了总线的引脚数,使得与总线互连的各个器件的引脚数不断增加,器件的封装尺寸增加。在PCB(Printed Circuit Board)印制时,这不符合现在电子设备日趋小型化的特点。现有部分总线采用了数据线和地址线复用的方式来解决此问题,如PCI总线。但是,由于采用了同样的物理连线传输两组数据,因此需要另外的控制仲裁单元,且降低了数据的传输速率。第二,提高数据频率。但是,通过提高总线频率的方法会受到与总线连接设备的数目限制。这是因为当总线频率超过130 M时,在总线上增加器件相当于增加容性负载[2],而容性负载增加会使数据传输信号的上升和下降时间增加,限制总线的工作频率,且频率的不断增加会使PCB板间的EMI增加,影响系统的稳定性。所以,对于传统总线如PCI、VME等,信号时钟的偏移容忍问题成为了影响总线性能的一个重要因素。

1.2SRIO总线

RapidIO互连架构是一个开放的标准,满足了嵌入式基础设施在应用方面的广泛需要。可行的应用包括连接多处理器、存储器、网络设备上的存储器映射I/O器件、存储子系统和通用计算平台[3]。

RapidIO互连定义包括两类技术:面向高性能微处理器及系统互连的并行接口;面向串行背板、DSP和相关串行控制平面应用的串行接口[4]。串行和并行RapidIO具有相同的编程模型、事务处理和寻址机制。

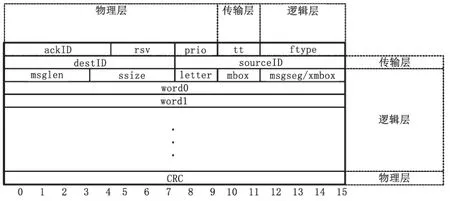

SRIO(Serial RapidIO)总线是基于报文交换的点对点传输串行互连体系结构,具有高性能、低引脚数的特点。SRIO总线由逻辑层、传输层、物理层三层组成,主要特点是采用了唯一的传输层规范,兼容不同的物理层和逻辑层规范[5]。逻辑层位于最高层,定义全部协议和包格式,为发起和完成事务提供必要的信息;传输层位于规范的中间层,定义RapidIO地址空间和在断点器件间传输所需的路由信息;物理层规范位于整个分层结构的最底层,包括器件级接口的细节,如包传输机制、流量控制、电气特性和低级错误管理[3]。其数据包格式及相应位域的所属层次如图1所示。SRIO通过数据包中包含的CRC、ACKID保证数据的正确性,通过控制符消息的重传、包定界等功能来保证数据的完整性。

图1 SRIO包格式

2 多通道短波通信系统

如图2所示,在一个多通道短波通信系统中,包含4个发射单元,6个接收单元、1个交换单元、4个业务单元及1个密码单元。各模块均通过SRIO交换器件连接,形成高效的点对点数据传输通路[6]。交换单元选用IDT公司的Tsi578作为SRIO交换器件。交换模块上有一块DSP芯片和FPGA芯片。由于DSP采用了TMS320C6416的定点高性能,不自带SRIO接口,故由FPGA生成ALTERA公司的提供的SRIO的IP核模块完成DSP芯片与Tsi578之间的数据通路搭建。DSP芯片负责数据转发控制、部分数据的中转及Tsi578的LUT(Look-up Table)的配置和管理。

图2 短波电台

发射单元和接收单元均采用DSP+FPGA结构,由FPGA进行大量数据的处理,DSP负责复杂算法的控制,以充分发挥DSP和FPGA的优势,提高处理效率。密码单元的设计采用黑盒子的思想,只对外提供数据接口和电源接口,不探测和响应外部状态的变化,表现为“供电即工作,断电即停止”的行为方式。接收到一包数据后即进行加密处理,作为系统中一个完全被动的从方存在。

业务单元为整个系统的功能单元,负责各种功能的实现。为了满足不同的功能业务需求,业务单元通常需要在各波形(波形应用软件,简称波形应用或波形,指的是软件无线电中产生通信波形的软件[7])之间切换。

3 任意接入设计

3.1在线状态共享

SRIO的可靠性传输是通过SRIO网络中每层的可靠性传输来实现的[8]。比如,三层SRIO网络中,发起者将数据包发送给中间器件,若中间器件返回ACKID,那么发起者则认为数据包成功发送,然后由中间器件将数据转发到目的器件,由目的器件返回ACKID给中间器件,如此完成数据包完整正确的发送,而并不是数据包准确到达目的器件后再逐层返回ACKID。以这样的方式传输数据,在发起者(Initiator)看来,这样的传输方式省去了中间数据传输的时间,所以此方式有效提高和保证了SRIO的数据传输速率。此方式使得采用SRIO总线的各模块能够更好地独立存在于系统中。在数据传输工程中,任一单元只与其直连单元产生关联,而与其他单元没有关联性,其传输方式如图3所示。

图3 SRIO数据传输模型

采用SRIO总线连接的系统中,各设备只与直连设备相关联,并不了解整个系统的状态。例如,本系统中,在业务单元突然从交换单元上移除的情况下,接收单元依然会不断上报数据到业务单元。数据会在接受单元和交换单元之间完成可靠性传输,但是在交换单元和业务单元之间必然产生非可靠性传输,引起系统堵塞,使系统产生错误。因此,交换单元需要实时将各单元的在线状况共享给各个单元。各单元在进行数据传输时,需进行目的ID是否在线判断。

交换单元监测各端口Port x Error and Status CSR寄存器中的PORT_OK和PORT_ERR位。当任一端口出现上下线时,更新各模块在线状态,立即下发各单元。本系统交换单元管理模块以64 k的频率检查更新端口在线状况,并下发给在线的各单元。

3.2ID分配方案

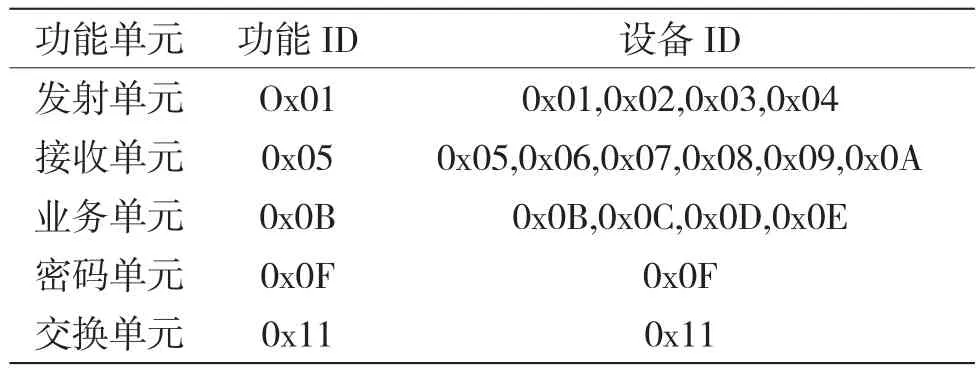

为了避免因同一功能单元各器件设备ID不一致而致使各器件内部软件不统一的现象,以实现系统中同一个功能模块的软硬件统一,各功能模块使用同一个功能ID,即同一功能模块采用同一ID进行软件设计,而在接入系统时由交换单元再次分配具体ID。例如,本系统中的功能ID和设备ID分配如表1所示。

表1 功能ID设置

交换单元由于印制在电路板上,故其对应Tsi578的端口号已经固定为0号端口;交换单元通过更改LUT中对应port的设备ID,发送门铃信息到此port连接设备,而后通过其响应的门铃信息获取相应的功能ID,再根据设备ID分配情况分配设备ID,随后再次配置LUT,并下发在线状态到各单元,其流程如图4所示。

图4 设备ID动态分配

由于配置路由时不知道连接到此端口的设备ID,而我们通过匹配端口的LUT和相应发送数据包目的ID的方法,将此数据包从该端口路由发送。所以,此时发送的数据包的目的ID与连接器件的设备ID不一致,需要在进行SRIO的IP核设计时,指定设计参数Transport and maintenance中的Disable Destination ID Checking by default功能打开,关闭SRIO IP核的目的ID检测功能,否则探测门铃信息将会被丢弃。

通过此ID分配流程,可以完成各器件设备ID的自动分配及任意器件连接交换器件任意端口功能。

4 独立性设计

4.1全局复位设计

在传统的复位方案设计中,在系统运行阶段不断监测SRIO的端口状况,对RapidIO IP核物理层提供的port_error信号采用周期性访问查询。若port_eror信号有效,则对自身进行复位,恢复到开机上电的原始状态。由于密码单元的特殊性,其并没有进行复位设计,而是作为一个功能单元挂接在系统中。

4.2全局复位设计存在的缺陷

传统的复位设计采用回到原点的做法来实现错误恢复,但是这样的设计存在两个缺陷:

第一,传统的复位设计使系统各模块之间产生级联性,若其中任一单元出现错误,产生复位时,与其连接的单元由于状态不相符合,无法与其进行通信,将跟随产生复位操作,产生连带效应,直到整个系统中的全部模块均完成复位操作。这对于大型系统需要耗费大量时间,从而不满足各功能模块通过交换单元连接,相互独立地存在于系统的要求。

第二,复位后无法进行正常通信,当出现密码单元以被动方式存在于系统的模块时,自身复位完成后,若密码单元不进行复位,这种在两个直连单元之间的非对称复位将导致AckID同步失败,导致通信中断。

4.3单端口复位设计

对于只有一个端口的SRIO器件而言,全局复位和单端口复位是一致的。但是,对于SRIO交换器件或者Tms320C6455这样集成多个SRIO端口的DSP则不一样。对系统中含有多个SRIO端口的器件采用单端口复位,由于各个设备都是直连于交换芯片上的,与交换芯片上的端口形成对联,故对交换单元上的Tsi578采取单端口复位将可以割断各单元之间的关联性,即一个器件故障只会影响其对应的连接端口,而不会对系统其他单元产生连带效应。在对单端口复位完成后,此端口的LUT处于不定状态,需要重新配置LUT。

各个器件连接到交换单元完成复位后,可能会出现错误,致使输入端口进入到output_error_ stopped状态、输出端口进入到input_error_stopped状态,产生的连接器件无法正常完成数据传输,此错误是由于两互连器件之间的AckID不同步引起的。因此,需要在复位完成之后进行AckID同步。

单端口复位设计的流程为:

(1)向Tsi578的寄存器SP_MODE中的SELF_RST写1,复位自身;

(2)向Tsi578的寄存器SP_CS_TX中写入0x40FC4000,通过控制命令符消息向连接器件端口发送reset_port命令;

(3)完成AckID同步。

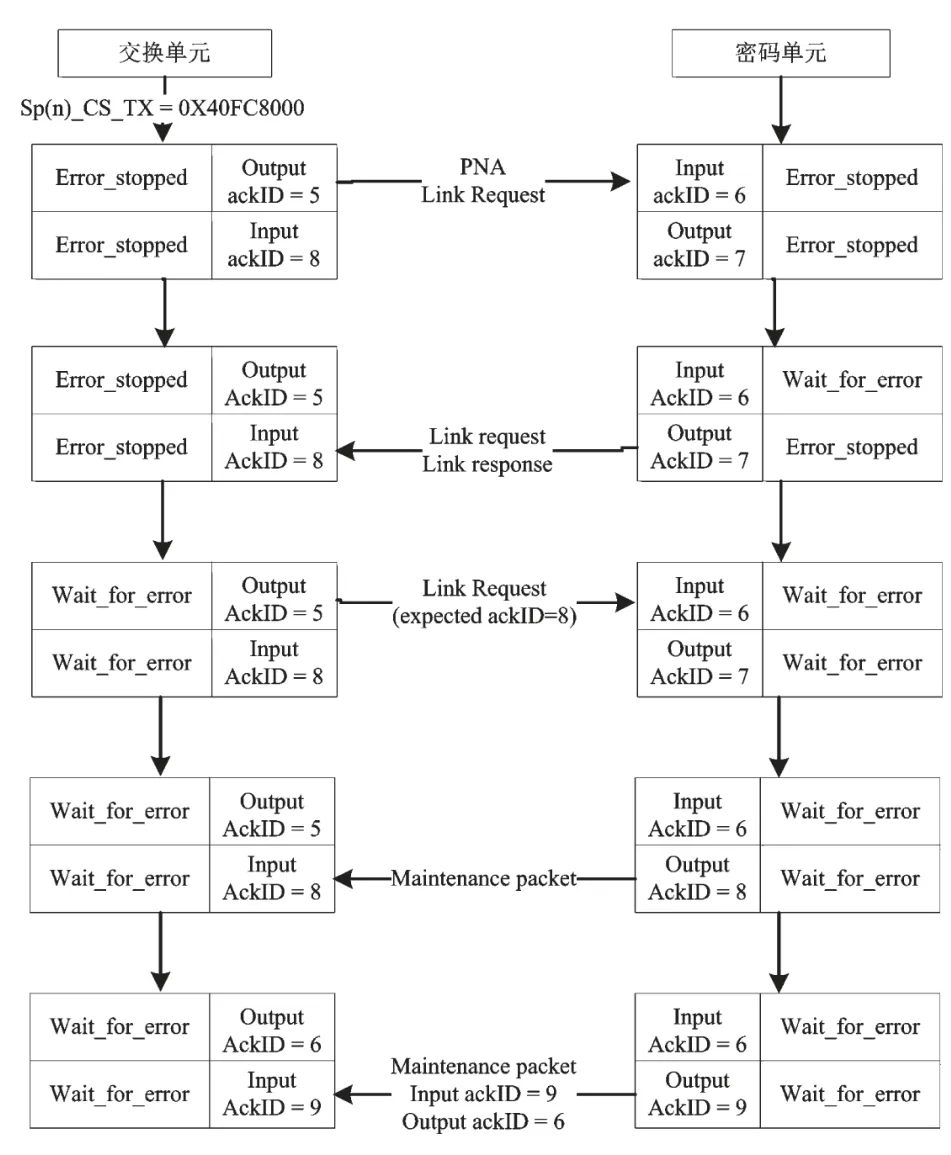

4.4AckID同步

通过SRIO的维护操作和控制符消息来完成ackID的同步。以密码单元和交换单元为例,其AckID同步过程如图5所示。

图5 AckID同步流程

(1)交换单元的DSP对交换单元SRIO的SP(n)_CS_TX(端口n控制传输寄存器)写入0x40 FC8000;向密码单元立即发送一个PNA和链接请求端口状态的控制符,在端口错误环境下,一个端口状态请求控制符会被当作restart-from-error控制符。密码单元SRIO收到此请求后,密码单元从Error stopped状态转移到wait_for_error状态;

(2)密码单元SRIO发出链接响应及链接请求,交换单元接收到链接响应将从stop_output状态转移到recover状态。此链接响应会本地在SP(n)_ LM_RESP(端口n链接响应寄存器)中写入密码单元SRIO的期望确认输入值(expected ackID),交换单元接收到链接请求,交换单元SRIO的输入端口从Error stopped状态转移到wait_for_error状态;

(3)密码单元SRIO收到交换单元SRIO的链接响应,密码单元SRIO的输出端口从Error stopped状态转移到wait_for_error,交换单元读取SP(n)_ LM_RESP寄存器的值,并将其写入本地SRIO的SP(n)_ACKID_STAT(端口n本地ackID状态寄存器)的outbound和outstanding AckID域中,使本地的输出端口的ackID和密码单元SRIO的期望ackID相匹配;

(4)交换单元发送一个维护包到密码单元SRIO的SP(n)_ACKID_STAT寄存器,将其输出端口的输出和正在输出ackID改写为本地SRIO期望的输入ackID,并将密码单元SRIO的输入ackID改写为步骤3中获取的ackID+1;

(5)此时,对连的两个SRIO的输入输出端口状态均恢复到wait_for_error且ackID完成同步,可以继续进行数据传输。

4.5交换单元复位设计

交换单元的各端口复位过程中需要包括ID动态分配、在线状态共享及AckID同步,其总体流程如图6所示。

图6 交换单元复位流程

交换单元通电开机之后,以64 kHz的中断速率检测并记录Tsi578各个端口的状态,当端口状态由坏变好,即端口设备上线时,对此端口进行单端口的复位操作,恢复Tsi578的端口恢复到原始状态,不对其他端口产生影响,并完成收发端口之间的AckID的同步,使得此端口可以与相连器件正常通信,之后通过配置路由完成动态ID的分配,最后更新各单元的在线状态,并下发到各在线器件,通知此设备ID器件加入系统并可以正常通信,进行数据传输。

当端口状态由好变坏时,即下线时,立即更新状态状况并下发,广播此设备ID器件脱离系统,不能对此设备ID进行数据传输,防止发生非可靠性的传输,使系统不稳定。

5 结 语

本文在将SRIO总线技术应用于多通道短波通信系统的背景下,提出了一种SRIO交换单元的设计方案。此方案实现了SRIO交换单元和因特网交换机一样的特性,支持任一端口接入和自动分配设备ID,交换单元上各单元相互独立存在于系统。此方案可以扩展到多交换器件系统中,但是在较大SRIO系统中的器件任意接入问题,仍然有待研究。目前,SRIO协议凭借优异的性能得到了广泛认可与应用,但是在使用过程中的灵活性较弱。如何提高SRIO总线的灵活性尚待深入研究。

[1] 仲维亮,杨斌,雷国志.基于DDS的传输插件的性能比较和分析[J].通信技术,2013,46(03):13-15. ZHONG Wei-liang,YANG Bin,LEI Guo-zhi.Comparison and Analysis on Performances of DDS Transmission Plugins[J].Communications Technology,2013,46(03):13-15.

[2] 刘琳.基于RapidIO的高数数据传输系统设计[D].哈尔滨:哈尔滨工程大学,2013. LIU Lin.The Design of High-speed Data Transmission System based on RapidIO[D].Harbin:Harbin Engineering University,2013.

[3] 张娟娟,陈迪平,柴小丽.VxWorks下RapidIO互连系统的实现[J].计算机工程,2011,37(03):236-240. ZHANG Juan-juan,CHEN Di-ping,CHAI Xiao-li. Implementation of RapidIO Interconnect System Under VxWorks[J].Computer Engineering,2011,37(03):236-240.

[4] 邓豹,赵小冬.基于串行RapidIO的嵌入式互连研究[J].航空计算技术,2008,38(03):123-126. DENG bao,ZHAO Xiao-dong.Research of Embedded Interconnection Frame based on Serial RapidIO Technology[J].Aeronautical Computing Technique, 2008,38(03):123-126.

[5] 李少龙,高俊,娄景艺等.基于SRIO总线的数字信号处理系统的实现[J].通信技术,2012,45(05):101-103. LI Shao-long,GAO Jun,LOU Jing-yi,et al.Implementation of Digital Signal Processing System based on SRIO Bus[J]. Communication Technology,2012,45(05):101-103.

[6] IDT.Tsi578 Serial RapidIO Switch User Reference Manual[EB/OL],www.idt.com.

[7] 楼才义,徐建良,杨小牛.软件无线电原理与应用[M].北京:电子工业出版社,2014:321.LOU Cai-yi,XU Jian-liang,YANG Xiao-niu.Software-Defined Radio:principles and practice[M],Beijing:Publsh ingHouse of Electronics Industry,2014:321.

[8] RapidIO.

王青波(1992—),男,硕士研究生,主要研究方向为数字通信、软件无线电;

高 俊(1957—),男,博士,教授,博士生导师,主要研究方向为通信理论与技术;

崔中普(1993—),男,硕士研究生,主要研究方向为数字通信、软件无线电。

Design and Implementation of Arbitrary Interconnection for SRIO Switch Unit

WANG Qing-bo, GAO Jun, CUI Zhong-pu

(College of Electronic Engineering,Naval University of Engineering,Wuhan Hubei 430033,China)

Based on device ID, the system of SRIO protocol is constructed, and when SRIO protocol is applied in multi-channel short-wave communication system,the specific device ID module should be connected to the specific port of switch module,and however there exists a defect in global reset design of the switch, and a hot swap insert in operation state would lead a reset of the whole system.Based on analysis of reliability transmission mechanism,error recovery mechanism and maintenance operation of SRIO protocol,a design scheme with dynamic device ID assignment,arbitrary port access and hot swap insert without any impact on the whole system,and similar to the Internet switch is proposed and implemented.

SRIO;switch unit;error recovery;arbitrary interconnection

TN915.05

A

1002-0802(2016)-08-01098-06

10.3969/j.issn.1002-0802.2016.08.027

2016-04-20;

2016-07-23

date:2016-04-20;Revised date:2016-07-23