基于PXI总线多通道时序监测电路系统设计

杨 光,朱宏飞

(北京航天测控技术有限公司,北京 100041)

基于PXI总线多通道时序监测电路系统设计

杨 光,朱宏飞

(北京航天测控技术有限公司,北京 100041)

通过对箭载发动机的时序监测方法进行研究、分析,设计出一款基于PXI总线多通道时序检测电路系统;介绍了系统的软硬件结构和功能,设计了输入光电隔离电路、数字消颤电路、数字跳变检测电路、计时器电路、FIFO存储器电路和PXI总线接口电路,在Labwindows/CVI环境下开发了测试系统软件,并通过控制测试设备实现对箭载发动机的时序监测;时序监测电路系统已经应用在导弹和火箭发射地面测试发射控制系统中,经过多次测试和发射场真实发射试验验证,达到了预期效果。

时序监测;PXI总线;监测技术

0 引言

随着国防现代化程度的提高,大型发射系统中对于发动机时序在线监测提出了更高的要求。发动机时序控制系统的工作状态正确与否,关系到导弹和火箭发射成败,所以在地面检测时对其充分的检测是非常必要的,发动机时序控制电路检测是地面测试发射控制系统重要工作之一。基于PXI总线的多通道时序监测系统作为一种自动实时时序监测及计时电路装置,实现了发动机时序控制电路全过程自动检查、判读、累计计数并保持记录,对于导弹和火箭发动机时序测量起到了至关重要性,在军用装备中得到大量应用。

以往对弹上和箭上发动机时序测量只局限于盲测和单路人工测试比对,需要耗费大量人力、物力和时间成本。而且测试可靠性较低,一旦系统出现故障后,不能精确定位,给后期维修及查找原因都带来了大量工作。

本文设计时序监测电路系统采用PXI总线结构,拥有在线监测和相对计时两种功能,并且设计1 MHz或1 KHz两种采样频率,计时器宽度为32位的72通道全双线输入方式,支持查询和中断两种工作方式,输入电压为0V~42V,可以满足目前弹上和箭上信号通用的时序测量范围。

1 设计原理

系统按照模块化设计思路,重点攻关消颤、计时和保持记录等功能。本设计采用成熟器件组成标准模块的设计架构模式,将全部设计分为输入光电隔离模块、数字消颤电路模块、数字跳变检测电路模块、计时器模块、FIFO存储器模块和PXI总线接口电路模块等组成。其系统原理框图如图1所示。

图1 时序检测电路系统框图

其中PXI总线接口模块、32位计时器模块、状态和时间寄存器模块以及输入跳变检测电路在一片Altera公司的FPGA芯片EP1C6Q240上实现。

每一次输入端口数据跳变时系统都会将输入端口状态和当前计时器时间保存到一组时间和状态寄存器以及FIFO存储器、置位一个状态位并向PXI总线控制器发出中断请求。通常可以通过寄存器组实时监测输入端口变化,FIFO存储器中记录输入端口数据变化的过程细节。

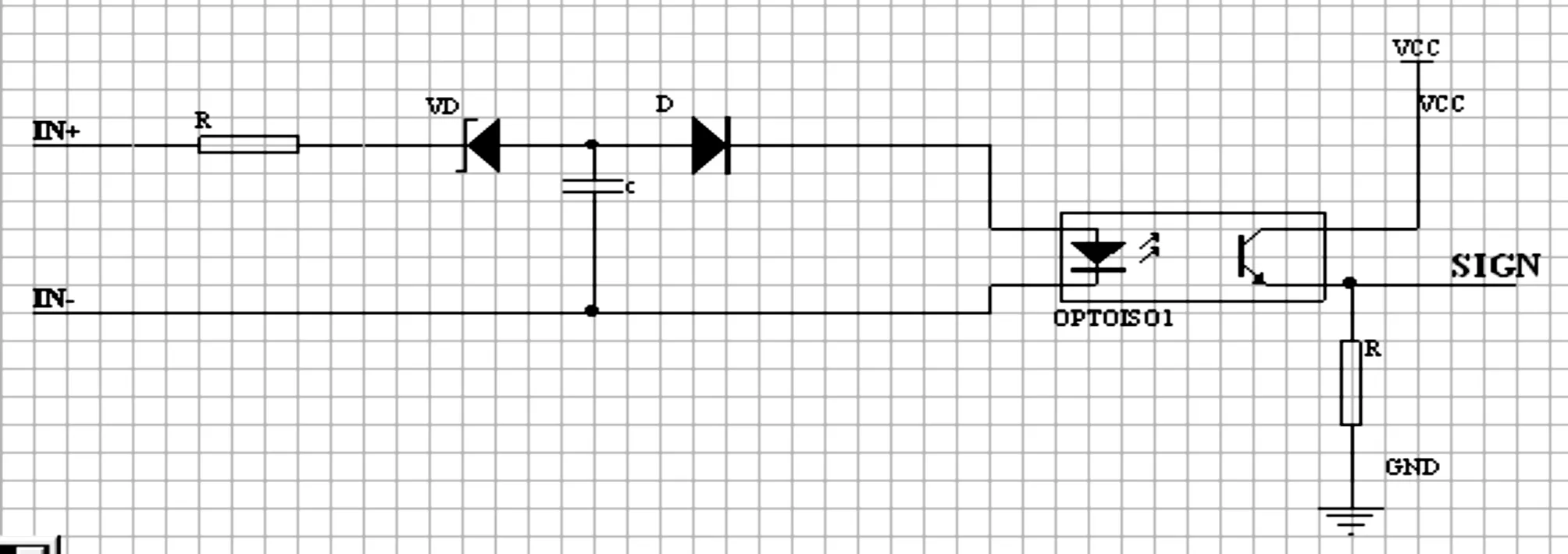

1.1 隔离电路模块的设计

隔离电路主要用于信号接受后的隔离,避免箭载或弹上系统和地面检查系统互相干扰,在隔离电路前增加了RC滤波电路、稳压电路和消除反流信号电路。隔离后对信号进行整形和电平信号的转换,为后续电路提供标准方波输入信号。如图2所示。

图2 隔离电路图

1.2 数字消颤电路模块的设计

这里举例说明,对1 ms以下抖动窄脉冲的滤除采用如下方法:用1 kHz的时钟对输入信号进行连续采样,当连续采样2次有效后才在事件寄存器中保存该次事件。这样就能保证模块对1 ms以下窄脉冲不做响应。

1.3 边沿监测电路设计

系统在检测到输入信号跳变时锁存输入信号状态及输入信号跳变的时间。如果直接用输入信号跳变来锁存输入信号状态及输入信号跳变的时间可能会在计时器改变时锁存到错误的时间值。解决的办法就是用计时器的时钟信号同步输入信号,在时钟信号的上升沿采样输入信号并且计时器加一,而在时钟信号的下降沿判断是否锁存输入信号及计时器的时间值。

PXI中断器的工作机制是通过PXI总线中断请求信号线向位于控制器模块上的中断处理器发送中断请求,位于控制器模块上的中断处理器在收到中断请求后会启动相应得中断应答周期,而发送中断请求的PXI中断器会响应中断应答,返回系统的中断向量并且清除中断请求。控制器模块及相应的设备驱动及VISA库会将收到的中断向量发送给相应的应用程序,调用相应的中断服务程序[1]。

系统时间计时器模块功能结构框图如图3所示。

图3 计时器模块功能结构图

1.4 FIFO计数器设计

在系统设计中,为了增加数据传输率、处理大量数据流、匹配不同传输率而采用FIFO存储器,从而提高了系统性能。

1) FIFO存储器是系统的缓冲环节,如果没有FIFO存储器对系统采集到的连续的数据流进行缓存,就有可能造成数据丢失。

2) 采用FIFO设计可避免频繁的总线操作,减轻CPU的负担,允许系统进行DMA操作,提高数据的传输速度。

本系统在FIFO设计使用中,我们使用了半满标志,即写入到FIFO 数据到了半满时产生中断,上位机响应中断读数据的时候,还可以向FIFO 中写数据,数据的读写操作互相不冲突,很好的实现了数据读写时钟的异步匹配。例如:FIFO的一端是AD数据采集,另一端是计算机的PCI总线,假设其AD采集的速率为16位 100 KSPS,那么每秒的数据量为100 k×16 bit=1.6 Mbps,而PCI总线的速度为33 MHz,总线宽度32 bit,其最大传输速率为1 056 Mbps,在两个不同的时钟域间就可以采用FIFO作为数据缓冲。

2 软件设计

本系统提供符合VXIplug&play规范的软面板驱动程序及函数库,兼容Windows2000/XP操作系统,可用于Visual C++6.0软件编程及Labwindows/CVI软件编程[2]。

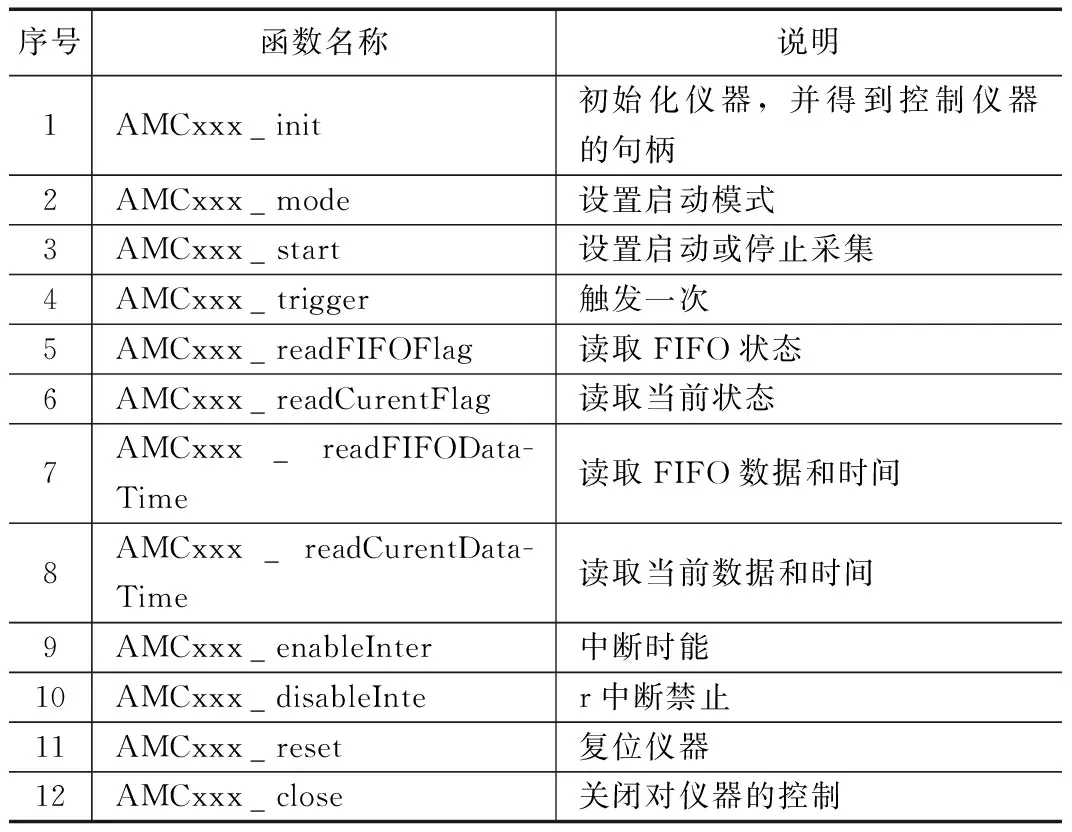

2.1 软件函数功能介绍及设计流程

本系统所使用的驱动函数名称及函数说明详见表1。测试软件流程图如图4所示。

表1 驱动程序函数列表

图4 软件流程图

编程事例:

本示例主要完成模块工作于查询方式下,读取FIFO数据的过程。

include "AMCxxx.h"

include

main( )

{

ViSession instrG;

ViStatus status;

ViBoolean empty,half_full,full;

//初始化,假设该模块逻辑地址为PXI0::12::INSTR,复位并获得模块句柄

status = AMCxxx_init (“PXI0::12::INSTR”, 0, 1, &instrG);

if (status<0)

{

printf ("初始化失败!/n");

return 0;

}

//设置计时分辨率为mS,测试方式立即启动

status = AMCxxx_mode (instrG, 1, 0, 0);

//启动采集

status = AMCxxx_start (instrG, 1);

……

//停止采集

status = AMCxxx_start (instrG, 0);

//读取半满标志位有效后退出

while(1)

{

status = AMCxxx_readFIFOFlag(instrG, &empty, &hfull, &full);

if(empty==0) break;

Status = AMCxxx_readFIFODataTime (instrG, data,&time);

if (status < VI_SUCCESS )

{

printf ("读取数据失败!/n");

}

}

printf ("读取数据完毕!/n");

status = AMCxxx_reset(instrG) ; //模块复位

status = AMCxxx_close(instrG); //关闭仪器

return 0;

}

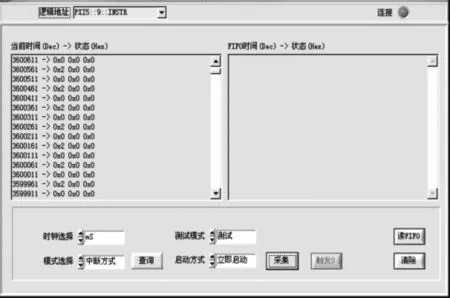

2.2 系统软件界面功能说明

系统软件界面包含以下功能:

1)逻辑地址:显示受控模块的VISA资源名;

2)连接:指示灯。当仪器运行时呈现“绿色”,未找到仪器时指示灯灭;

3)当前时间 —〉状态:显示中断或查询收到的72通道的时间和状态数据;

4)FIFO时间 —〉状态:显示从FIFO中取回的72通道的时间和状态数据;

5)时钟选择:选择模块测量时序的时钟;

6)模式选择:选择中断或查询模式接收数据;

7)查询:查询模式时使能/禁止查询定时器;

8)测试模式:选择是否输出自检信号,在“自检”模式时模块输出一个10Hz的0/1信号到1、33通道;

9)启动方式:选择“立即启动”还是“触发启动”;“立即启动”方式下单击“采集”/ “停止 ”控制模块;“触发启动”方式下,单击“采集”以后需要再单击“触发0”才能启动模块;单击“触发0”操作将在PXI 背板TRIG0上产生一个触发信号,可用于启动其它模块;

10)读FIFO:单击“读FIFO”时将模块FIFO中的取回显示在FIFO时间 —〉状态;

11)显示数据格式:时间—〉低32路状态,33-64路状态,65-72路状态。

3 试验结果及分析

3.1 仿真测试

为了验证系统的所有功能都能够实现,并保证各项功能都正常,通过Quartus II 软件进行仿真验证,得到的仿真图和逻辑分析仪图如图5~6所示。

图5 仿真图

图6 逻辑分析仪图

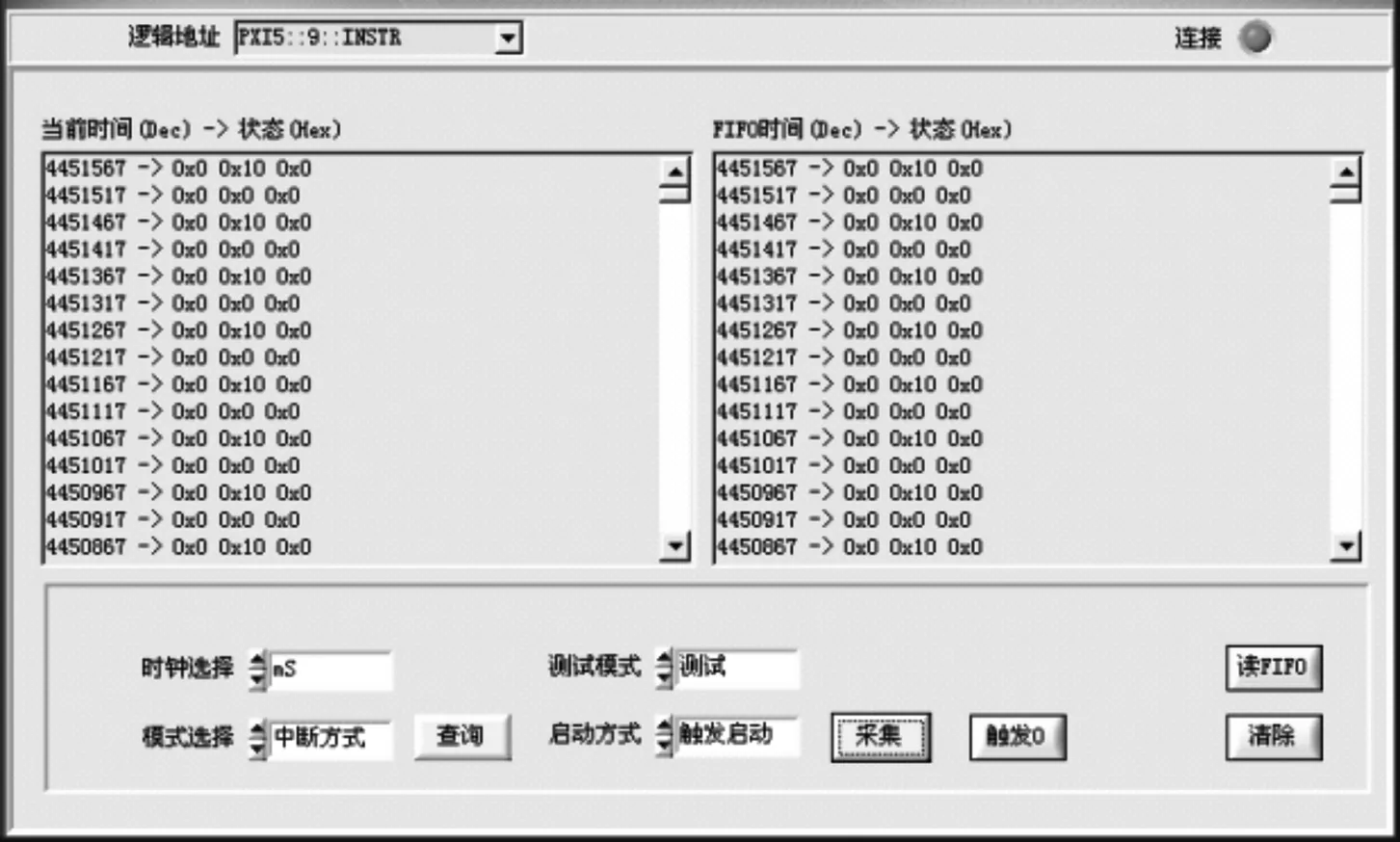

3.2 软件测试结果及分析

对实验测试结果进行分析,下面所示的图列为对系统的功能进行实际测量所得的测试结果。其中,图7为系统自检测试结果,实时监测的结果与最后从FIFO中取回的数据完全相同;图8为毫秒计时功能测试结果,t=1/f/2变化一次状态,并且显示的状态值与输入信号的通道数一致;图9为微秒计时功能测试结果,t=1/f/2变化一次状态,并且显示的状态值与输入信号的通道数一致;图10为计时范围测试结果,模块计时3 600秒后仍然可以进行测量,证明模块计时范围为3 600秒;图11为存储深度测试,FIFO栏所显示的数据个数大于1 k,证明模块存储深度大于1 kSam。

图7 自检时序检测功能测试结果

图8 毫秒计时功能测试示意图

图9 微秒计时功能测试示意图

图10 计时范围测试示意图

图11 存储深度测试

4 结论

本文所提供的检测方案,已应用在多型号弹载和箭载地面测发射系统中,实现对弹箭载发动机时序控制系统的精确测量。并能通过测试程序对出现的异常数据,进行精确的定位及处理,在与导弹及火箭其他测试程序同时工作时没有出现不兼容的问题。

本系统的成功实现,对于弹箭载发动机控制时序可信测量,提供较好的技术保障[4]。在方案的设计实现上,利用FPGA实现了部分计时、计数和监测电路设计,提高了系统集成度。在工程应用中还可以基于此设计方案进行其它总线的研究,使小型化导弹和火箭地面测试系统改造在规范化、标准化上更加完善。

[1] 韩大伟,周 军,于晓周. 基于PXI总线的导弹自动测试系统设计[J].计算机测量与控制,2008(11):1650-1652.

[2]沈 辉,关振宏. 基于PXI的虚拟仪器测试技术[J].现代科学仪器,2004(6):16-18.

[3]冉隆燧. 运载火箭测试发控工程学[M].北京:中国宇航出版社,1989.

[4]樊尚春,周浩敏.信号与测试技术[M]. 北京:北京航空航天大学出版社,2002.

Multi-channel PXI Bus System Based on Timing Monitor Circuit

Yang Guang, Zhu Hongfei

(Beijing Aerospace Control Technology Co., Ltd. Beijing 100041,China)

Through the research and analysis of the time series monitoring method of the engine, a PXI bus based multi-channel sequential detection circuit system is designed. The hardware and software structure and functions of the system are introduced. The input circuit, digital circuits, FIFO memory circuit and PXI bus interface circuit are designed. The time series monitoring circuit system has been applied in the ground test and launch control system of missile and rocket launching, and it has been verified by the test of many times on the launching field, and achieved the expected results.

Timing monitoring; PXI bus; monitoring technology

2015-09-16;

2015-10-26。

杨 光(1986-),男,河北唐山人,主要从事VXI、PXI测试技术,综合保障工程方向的研究。

1671-4598(2016)03-0214-04

10.16526/j.cnki.11-4762/tp.2016.03.058

TP311

A